SerDes:串行和并行通信有何区别?

描述

关键要点

SerDes(Serialization/Deserialization)是一种在数字通信系统中提供重要优势的串行/并行转换电路。

串行通信比并行通信更受青睐,因为它可以减少连接线数量、降低电磁干扰、节省功耗等。

SerDes是一种将并行数据转换为串行数据,并将串行数据转换为并行数据的过程,具有多种实现方式和功能。

总结

本文介绍了串行和并行通信之间的区别,并详细讨论了为什么在数字通信系统中串行通信更为常见。并行通信虽然可以实现更快的数据传输速率,但需要更多的连接线,易受电磁干扰。而串行通信能够用较少的连接线传输任意位宽的数据,并且可以降低功耗,提高抗干扰能力。SerDes是实现串行/并行转换的关键技术,通过将并行数据转换为串行数据进行传输,并将串行数据重新转换为并行数据进行处理。它还具有多信道支持、时钟倍频和发送/接收同步等功能。SerDes已成为数字电子技术中不可或缺的一部分,特别适用于视频接口、电信连接和其他高数据率应用。

在我的工程职业生涯的早期,我认为并行通信通常比串行通信更可取。我很欣赏同时移动所有 8 个(或 16 个、或 32 个……)数据位的简单性和效率,使用一个或两个控制信号进行握手,并且不需要复杂的同步方案。

但不久之后,人们就发现流行的数字通信协议(UART、SPI、I2C等)使用串行接口,而且我还注意到,专用应用程序的高级协议有利于串行传输。尽管 微控制器和中央处理器单元 (CPU)需要并行数据来进行内部存储、检索和处理操作,这意味着串行通信涉及额外的序列化和反序列化硬件。

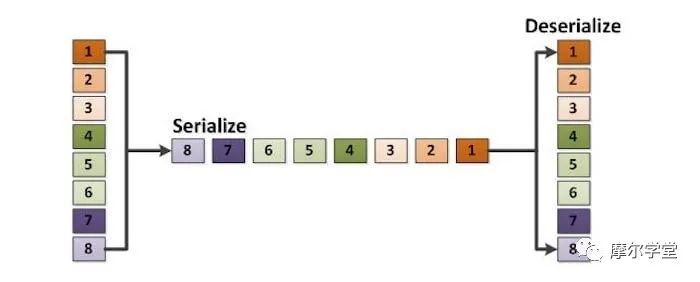

SerDes 是空间到时间到空间的转换。并行数据同时传输,但占用不同的物理互连,而串行数据共享相同的物理空间,但占用不同的时间时刻(图 1)。

图 1. 显示序列化和反序列化的示例图。图片由德州仪器 (TI)提供

考虑到所有这些,让我们看一下并行数据传输的局限性,然后我将讨论一些重要的 SerDes 概念。

为什么串行通信优于并行通信?

并行传输更直接的缺点之一是涉及的导体数量。如果您仍然在 8 位世界中工作,相对于简单、同步数据传输的好处来说,使用一系列互连似乎是合理的。然而,随着总线宽度扩展到 16 位或 32 位范围,PCB 布局任务变得越来越低效且难以管理。当您不仅需要将数据从一个组件移动到另一个组件,而且还需要从一个 PCB 移动到另一个 PCB 时,问题会变得更加严重。

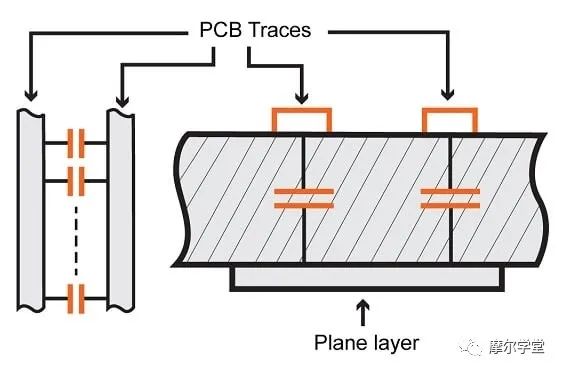

此外,每条并行数据线不仅仅是布局和布线人员关心的问题。间隔紧密的电线或 PCB 走线(如图 2 所示)容易受到串扰的影响,尤其是数字信号的高能逻辑转换特性,并且较大的导体组更难以屏蔽环境电磁干扰 (EMI)。

图 2: 当迹线是原理图中的线路时,它们具有完美的电气隔离,但在真实的 PCB 上,它们会电容耦合到附近的迹线和平面层。

通过串行,一些互连就足以传输任何位宽的数据字,并且您可以减少虚假逻辑转换的可能性,这些逻辑转换会损坏数据或需要重新传输,从而降低通信质量。

从理论上讲,并行确实可以实现更快的数据传输,但即使这种优势也比最初看起来的更具有偶然性。较长的走线或电线意味着信号需要更多的时间从发送器传播到接收器,并且随着数据速率的增加,通过匹配走线长度来均衡整个总线的延迟变得更加重要。高速 32 位总线的迹线长度匹配并不是微不足道的,如果我进行布局,这将是支持序列化/反序列化的一个非常有力的论据。如果您需要均衡走线长度,这会很有帮助,但当您尝试最小化电路板面积时,它就没那么有用了。

高速并行总线的另一个问题是功耗过高。串行化可以通过将标准逻辑信号转换为低压差分信号来降低功耗。

什么是串行解串器?SerDes 功能和特性概述

SerDes 是一个涉及两个独立电路块的过程:在其基本形式中,串行器将由多个同时数字信号(例如由微处理器或 ASIC 输出)表示的数据转换为沿一根导体传输的逻辑电平的时间序列。解串器将逻辑电平的时间序列转换回沿多个导体同时传输的一组信号。

除了这个基本功能之外,SerDes 实现还具有各种细节和附加功能。

多个串行导体

并串转换不一定将多根导线压缩为一根导线。更一般地说,串行化的目标是显着减少导体的数量。

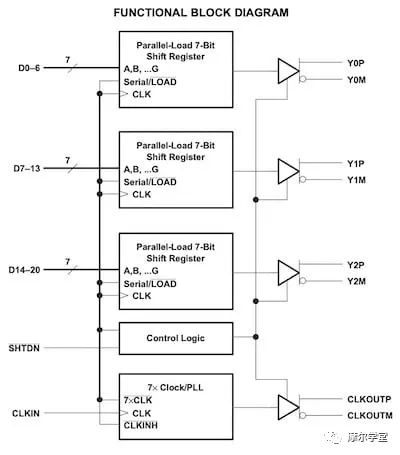

首先,单个串行通信线路通常需要两个物理导体,因为许多串行接口(例如RS-485和USB)使用差分信号。此外,吞吐量和接口复杂性之间的最佳平衡可能需要多个串行通道。例如,在下面图 4 的框图中,根据TI SN65LVDS95 LVDS串行器的数据表,21 位并行数据被转换为三个独立的串行输出流。

图 4. 数据表中 SN65LVDS95 串行器的功能框图。图片由德州仪器 (TI)提供

时钟倍频

如果串行器以特定频率接收并行字,则它必须增加输出比特率以使输出字速率与输入字速率相匹配。由于串行传输比并行传输更适合高比特频率,因此串行化不需要降低吞吐量。如上图所示,可以使用锁相环(PLL)根据并串转换中实现的压缩因子来倍增输入时钟。

发射/接收同步

与任何数字通信接口一样,SerDes 需要一些同步机制来确保接收器知道如何采样和解析传入的逻辑电平。一些系统(包括上图中所示的系统)会随数据一起发送时钟信号。

解串器还可以从传入的串行比特流中获取同步:PLL 可以锁定比特流并产生采样时钟。然而,如果输入信号的转换密度不足,PLL 将发生漂移。例如,传感器信号可能在正电源轨处饱和,并被数字化并串行化为一长串逻辑高位。为了防止与低转换密度相关的问题,您可以将 SerDes 系统与标准(例如 8b/10b)或自制编码方案结合起来。

传输媒体

将并行数据作为串行数据传输为您提供了物理传输选项,否则这是不可行的。即使所有信号都位于同一 PCB 上并且所有内容都使用普通走线进行布线,串行化也可以极大地简化电路板布局。如果您要在电路板之间、模块之间、模块之间或系统之间传输数据,您可能更喜欢使用同轴电缆或光纤链路。如果您有序列化数据,您就可以从普通电线升级到同轴电缆或光纤。

获得 SerDes 的优势

SerDes 已成为数字电子产品不可或缺的一部分。使用并行传输无法类似地实现视频接口、电信互连和各种其他应用所需的极高数据速率。

审核编辑:刘清

-

串行通信和并行通信的区别是什么2025-07-22 3447

-

并行通信和串行通信是什么意思?同步传送和异步传送又有何区别2024-02-18 2423

-

串行线调试与JTAG有何区别?2024-01-15 1002

-

并行总线和串行总线的区别2023-12-07 6456

-

什么是SerDes呢?为什么我们需要此项技术呢?有哪些设计要求和技巧?2023-11-07 4181

-

串行接口和并行接口有什么不同2022-06-21 12270

-

串口通信、串行通信和通用串行总线有何联系及其区别2022-02-16 2871

-

什么是并行通信和串行通信2022-01-13 1915

-

串行通信和并行通信的区别是什么?2021-12-10 3338

-

并行与串行通信机器的通信方式有哪几种2021-12-08 1432

-

并行通信和串行通信的区别2021-07-27 2147

-

并行与串行有什么区别2019-07-23 2696

-

串行和并行的区别2017-11-24 18441

全部0条评论

快来发表一下你的评论吧 !