什么是数字中频?FPGA怎么实现数字中频?

描述

数字中频

所谓中频,顾名思义,是指一种中间频率的信号形式。中频是相对于基带信号和射频信号来讲的,中频可以有一级或多级,它是基带和射频之间过渡的桥梁。

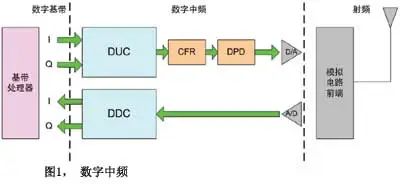

如图1所示,中频部分用数字方式来实现就称之为数字中频。数字中频技术通常包括上下变频(DUC/DDC)、波峰因子衰减(CFR)和数字预失真(DPD)。

DUC/DDC

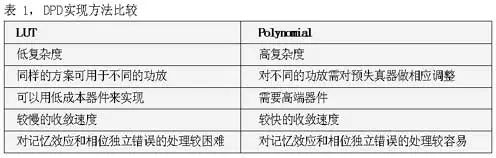

DUC实现了从“复”基带(Baseband)信号到“实”带通(Pas***and)信号的转换。输入的复基带信号采样率相对较低,通常是数字调制的符号率。基带信号经过滤波,然后被转换成一个更高的采样率,从而调制到NCO的中频载波频率。

DUC通常需要完成频谱整型(Pulse shaping),然后调制到中频载波,以便于经由DAC驱动后面的模拟转换器。

在图2中,通道滤波器(Channel Filter)完成基带信号的频谱整型,通常由FIR实现。插值(Interpolation)部分完成信号采样率变换和滤波功能,可以采用CIC或者FIR实现。对于一个窄带信号,如果需要高倍采样率变换,那么CIC将是非常合适的,无论是在实现性能或是资源节省方面,CIC都将优于FIR。

NCO是一个数控振荡器,也叫DDS,可以用来产生一对相互正交的正弦和余弦载波信号,与插值(增加采样率)以后的基带信号混频,完成频谱上搬。

与DUC相反,DDC基本上完成了以下几个工作:

1. 频谱下搬:将ADC送来的数字信号有用频谱,从中频搬移到基带

2. 采样率降低:将频谱搬移后的数据从ADC的高速采样率降低到一个合适的采样速率水平,通过抽取(Decimation)实现。

3. 通道滤波:在将I/Q信号送入基带处理以前,需要再对其进行滤波

实际上,数字上下变频技术应用非常广泛,其在无线通信、有线电视网络(Cable Modem)、数字电视广播(DVB)、医学成像设备(超声),以及军事领域当中,都是不可或缺的功能。

CFR

目前许多无线通信系统,如WCDMA、WiMAX,其中频信号通常由多个独立的基带信号相加而成。合成的中频信号有较大的峰均比(Peak-to-Average Ratio),并符合高斯分布。而通常功放(PA)的线性区是有限的,较大PAR的中频信号对应的PA的工作范围将被缩小,从而引起PA效率的降低。因此在PA之前减小中频信号的PAR是非常重要的。波峰因子衰减(CFR)正是用来完成这一功能的,它将有利于保证PA输出的线性度,降低带外辐射,提高PA效率。

目前,中频采用的CFR算法有:波峰箝位(Clip),波峰修整(Peak Windowing)和波峰消减(Peak Cancellation)。其中波峰修整方式的性能和可实现性都较为适中。波峰消减相对于波峰修整有较好的带外特性,但需消耗更多的FPGA资源。

DPD

在无线通信系统中,往往需要PA的输出具有很高的线性度以满足空中接口标准的苛刻要求,而线性功放又非常昂贵。为了尽可能提升PA的输出效率和降低成本,必须校正PA的非线性特性,而对PA的输入信号进行预失真处理是一个不错的选择。

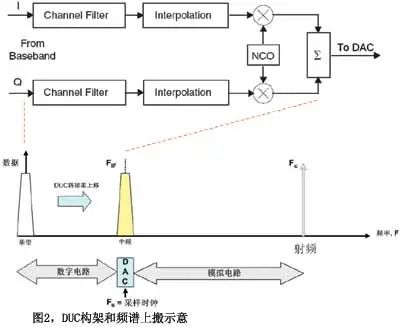

DPD实现方式分为查找表(LUT)和多项式(Polynomial)两类。两种算法的优缺点如表1所示。

FPGA实现优势

FPGA实现数字中频

随着WiMAX/LTE等宽带无线通信技术的逐渐成熟,对无线设备数字中频带宽的要求也越来越高。同时如MIMO等多天线技术日渐广泛应用,数字中频的通道数也在迅速增加。

对于如此大的运算带宽需求,许多DSP处理器难以满足实际应用,而专用芯片(ASSP)又缺乏相应的灵活性。采用FPGA实现数字中频,能够很好的协调处理能力和灵活性之间的矛盾。同时Altera公司针对3G/4G等应用开发了大量的数字中频参考设计和IP,简化了设计者的开发难度,缩短了设计周期。

FPGA器件属于硬件,它的特点是比较适合速度较高、逻辑关系不复杂的数据通路实现。

通过我们对前面DDC和DUC功能的分析,我们发现实现DDC/DUC的模块和运算主要有CIC/FIR滤波、NCO、插值/抽取、混频。这些基本上属于算法简单、但计算速度较高的处理,非常适合于FPGA的实现。

从另一个角度讲,FPGA相比DSP处理器的优势是并行构架。一个DDC/DUC模块完成以后,只要做简单的复制,就可以扩展到多路DDC/DUC。同时,一个ADC/DAC器件可以连接多个通道的DDC/DUC,从而可以轻松支持多载波(Multi-carrier)系统。

而有时候FPGA内部的资源有限,多路DDC/DUC甚至可以做时分复用,公用一块DDC/DUC的电路,当然电路工作时钟也需要提高相应的倍数,只要在该FPGA性能允许范围以内就可以了。Altera拥有支持包括WCDM A,TD-SCDMA,和WiMAX的参考设计。

CFR电路的计算量较大,例如TD-SCDMA,采样率从61.44MHz~92.16MHz,基于FPGA的并行处理可以轻松完成。

多项式DPD分为前向和反向模块,前向模块为预失真器,由多个FIR滤波器组成,非常适合硬件FPGA实现,Altera的IP核可以提供完善的FIR支持。反向模块为特定的收敛算法,如LMS、RLS,Altera都可以提供相应的参考设计。其中,对于RLS,Altera的参考设计采用QR分解方式,缩短了收敛时间,提高了算法的稳定性。

Altera提供的资源

Altera公司除了在器件设计上考虑了数字中频应用的实际情况外,也在IP核、控制粘合逻辑、接口逻辑、设计工具和流程,以及参考设计方面做了大量的工作。

在FPGA器件资源上,Altera最新的Cyclone和Stratix系列在内嵌存储器和乘累加模块方面,无论是数量还是速度都有较大程度的提高。

在DSP的IP核组件方面,Altera能提供包括FIR,NCO,CIC,CORDIC等功能组件。为了方便用户的系统集成,同时还提供了用于这些模块之间互联的统一接口:Avalon Streaming(Avalon-ST)接口。另外,为了多通道的复用和解复用,Altera还设计了Avalon-ST接口的包格式转换器(Packet Format Converter),用于将输入的单个或多个Avalon-ST通道与输出的单个或多个Avalon-ST通道提供时间和空间接口,用于多通道的复用与解复用。

在一些需要灵活性的领域,比如DPD,Altera的Nios II嵌入式处理器正好可以发挥功用,例如,在DPD的反馈路径上,它可以帮助用户灵活增加自己的插值例程。Nios II嵌入式处理器还可帮助系统做一些数据统计、参数重配以及其它管理工作。

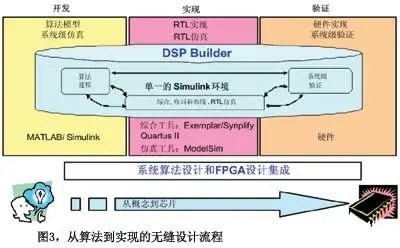

在设计验证工具和流程方面,Altera力推MATLAB/Simulink+DSP Builder+Quartus II的一体化设计流程。如图3所示。

同时Simulink还可以集成ModelSim和FPGA内嵌逻辑分析仪SignalTap-II来协助用户做功能仿真、调试。另外,硬件在环(Hardware In Loop)功能方面可以帮助用户在实际硬件上验证设计算法,同时也加速了验证的速度。

-

数字中频和模拟中频频谱仪原理及设计对比2015-10-29 2648

-

数字中频概述2018-05-21 4822

-

怎么实现中频数字化接收机系统的设计?2021-04-22 2197

-

什么是数字中频?FPGA怎么实现数字中频?2021-05-08 2914

-

数字方法中频信号相干检波实现2010-06-15 945

-

宽带中频数字接收机的FPGA实现2006-03-11 1828

-

数字中频的设计2011-04-08 1157

-

数字中频与FPGA探讨2011-08-11 1096

-

基于FPGA的全新数字化PCM中频解调器设计2012-03-05 1260

-

软件无线电数字中频系统的设计与实现2013-01-08 857

-

基于FPGA的并行处理实现数字中频的设计2020-03-03 3905

-

基于多相滤波的正交采样零中频数字化接收及QPSK高速解调的FPGA实现2021-03-19 1304

-

基于多相滤波的宽带中频正交采样数字零中频接收方案2022-12-12 705

-

基于FPGA的并行处理实现数字中频设计2023-04-26 2742

-

基于软件无线电技术的数字中频系统的实现方案2023-10-20 508

全部0条评论

快来发表一下你的评论吧 !