FPGA引入光芯片设计是未来矩阵计算新模式?

可编程逻辑

描述

FPGA是可以先购买再设计的“万能”芯片

FPGA现场可编程门阵列,是在硅片上预先设计实现的具有可编程特性的集成电路,它能够按照设计人员的需求配置为指定的电路结构,不必依赖由芯片制造商设计和制造的ASIC芯片。

广泛应用在原型验证、通信、汽车电子、工业控制、航空航天、数据中心等领域FPGA 硬件三大指标包括:制程、门级数及SERDES速率,配套EDA软件工具同样重要,比较FPGA产品可以从技术指标入手。

从FPGA内部结构来看,主要包括:可编程输入/输出单元(I/O)、可编程逻辑块(LC)、 完整的时钟管理(CMT)、嵌入块式 RAM(BRAM)、布线资源、内嵌的底层功能单元和专用硬件模块等。

根据赛灵思披露的数据,一个LUT6等效1.6个 LC,一个 LC对应几十到上百“门”,1000万门约等于10万LC,即100K CLB级别FPGA。

与ASIC不同的是,在选购FPGA产品不仅考虑硬件参数,配套EDA软件的性能也同样重要。

目前国内厂商高端产品在硬件性能指标上均与赛灵思高端产品有较大差距。

相对于ASIC,FPGA具有3点优势:(1)可编辑,更灵活、(2)产品上市时间短,节省了 ASIC 流片周期、(3)避免一次性工程费用,用量较小时具有成本优势。

新型光学芯片已被发现

近日,研究人员开发了一种易于使用的光学芯片,可以自我配置实现多种功能,他们实现的正实值矩阵计算使芯片具有应用于需要光神经网络的应用程序的潜力。

光神经网络可用于各种数据密集型任务,如图像分类、手势解释和语音识别,此前已经开发出可以在制造后重新配置以执行不同功能的光子集成电路。

然而,它们往往难以配置,因为用户需要了解芯片的内部结构和原理,并单独调整其基本单元。

中国华中科技大学研究团队负责人董建绩说:“我们的新芯片可以被视为一个黑盒子,这意味着用户不需要了解其内部结构就可以改变其功能。他们只需要设定一个训练目标,在计算机控制下,芯片将自我配置,以实现基于输入和输出的预期功能。”

可实现任何所需应用的电子集成电路

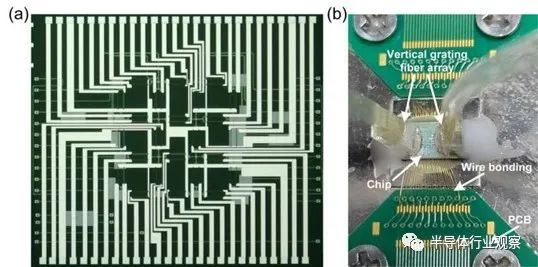

在《光学材料快报》杂志上,研究人员描述了他们的新芯片,该芯片基于一种名为马赫—曾德尔干涉仪(MZI)的波导光学组件网络,该网络以四边形模式排列。

研究人员表明,该芯片可以自我配置,以执行光路由、低损耗光能分裂和用于创建神经网络的矩阵计算。

在未来,预计将实现更大规模的片上可编程波导网络。随着进一步的发展,它可能会实现与现场可编程门阵列(FPGA)相媲美的光学功能——在制造后可以重新编程以执行任何所需应用的电子集成电路。

创建可编程MZI网络

芯片上的四边形MZI网络可能对涉及光神经网络的应用有用,这些网络是由相互连接的节点创建的。

为了有效地使用光学神经网络,网络必须使用已知数据进行训练,以确定每对节点之间的权重,这项任务涉及矩阵乘法。

片上矩阵操作通常使用前向传播MZI网络或微环阵列来实现。受电子学中FPGA的启发,希望使用MZI拓扑网络结构,允许矩阵操作的前馈和反馈传播。

开发的芯片可以通过调整电极的电压来重新配置,这在四边形网络中创建了各种光传播路径。研究人员集成了一种梯度下降算法来加快代价函数的收敛速度,该函数在每次训练迭代中衡量网络的准确性。

在每次训练迭代后,芯片更新所有可调电极的电压,而不是单一变量的值,这进一步提高了代价函数的收敛速度,有助于使训练过程更快。

该芯片在未来的价值

该芯片可用于执行所谓的正实数矩阵计算,验证了其在四边形 MZI 网络中的可行性。芯片的训练结果与目标矩阵之间的误差很小。

光路由可以在数据中心的处理器和内存单元等设备之间有效地路由光信号。与电气方法相比,光学方法有助于在处理大量信号时减少延迟和功耗。

此外,该芯片还用于低损耗光功率分离,将单个输入光分离成在其输出端口具有成比例能量的光束。

而且在分裂过程中的能量损失保持在1.16 dB以下,低损耗光能量分裂可用于将信号发送到芯片上的不同组件,例如处理器和光电探测器,这有利于同时处理输入信号。

结尾:

研究人员目前正在努力改进该芯片,以实现更多的矩阵运算功能,同时将其用于光学神经网络之外的矩阵计算的其他应用。

审核编辑:刘清

-

这家公司研发玻璃光计算芯片,算力超传统AI推理芯片千倍2026-01-19 7404

-

FPGA+AI王炸组合如何重塑未来世界:看看DeepSeek东方神秘力量如何预测......2025-03-03 7672

-

波形图属性里的刷新模式无法选取修改是怎么回事??是只有波形图表才可以修改刷新模式吗??2016-06-12 6278

-

基于FPGA的计算器设计:矩阵键盘模块(含程序)2016-08-09 5982

-

勇敢的芯伴你玩转Altera FPGA连载19:4X4矩阵按键电路2017-11-03 4025

-

labview波形图表之三种刷新模式2018-10-13 15862

-

LVGL MIPI屏无法进入局部刷新模式怎么解决?2023-04-19 1058

-

基于MT90系列与FPGA的交换矩阵设计2010-07-15 637

-

移动电视新模式发展方向2010-12-22 893

-

基于FPGA Nios-Ⅱ的矩阵运算硬件加速器设计2011-12-06 1605

-

数字2030未来制造业新模式,推动着新一代信息技术与制造业融合2018-10-10 2462

-

Apple Watch将引入全新模式2020-03-31 2917

-

SchoolTime模式和Kid模式引入iPhone2020-04-17 3341

-

AGM观点:独立FPGA公司将不复存在2022-03-10 8091

-

基于数据算法驱动的配方研发新模式2025-08-06 1411

全部0条评论

快来发表一下你的评论吧 !