介绍一种具备RDMA功能的FPGA网卡实现方案—RNIC

描述

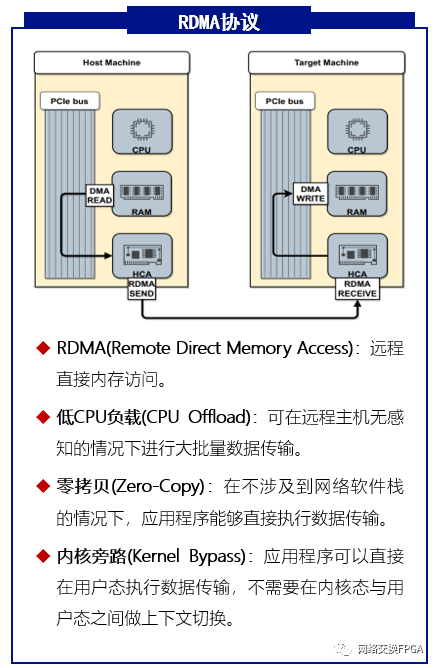

传统TCP/IP技术处理数据包需通过操作系统和其他软件层,导致数据在系统内存、处理器缓存和网络控制器缓存间频繁复制,增加了服务器CPU和内存的负担,特别是在网络带宽、处理器速度与内存带宽不匹配时,网络延迟会进一步加剧。RDMA技术通过将数据处理从CPU旁路并卸载到硬件上来实现低时延和高带宽特性。

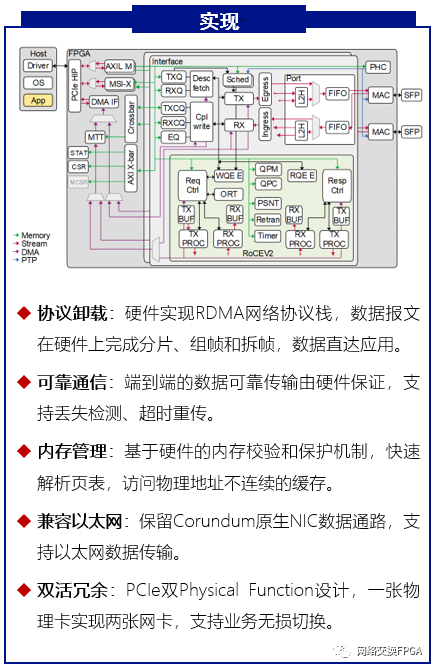

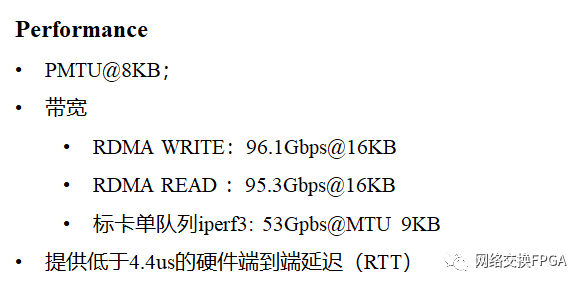

基于这一研究背景,介绍一种具备RDMA功能的FPGA网卡实现方案—RNIC 。本方案以Corundum开源高性能原型平台为基础, 实现了100Gbps的RoCE v2网络协议栈卸载加速;在保留Corundum原生PCIe DMA引擎等组件的基础上,通过精准的拆分设计、逻辑耦合和路径复用,将RoCE v2网络协议栈嵌入以太网网卡设计。方案支持单边RDMA READ和RDMA WRITE操作、双边SEND/RECV操作以及立即数操作,提供Back-to-N的重传机制保障数据传输完整性的同时提供了可达256的Outstanding能力, 并支持基于DCQCN算法的拥塞控制机制为本方案在数据中心等场景的大规模部署提供保障。实测RNIC能够实现低至4us左右的硬件端到端延迟以及高达96Gbps的吞吐量。

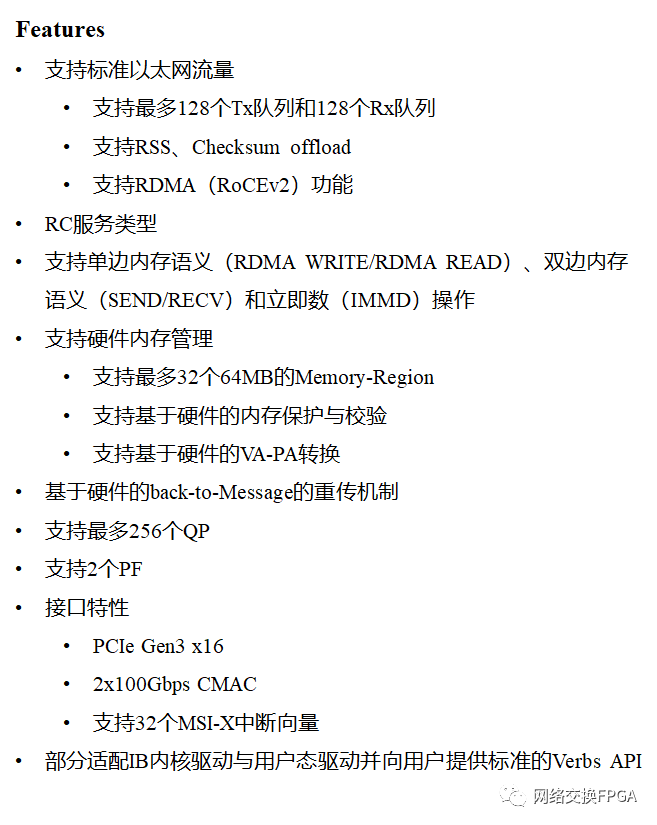

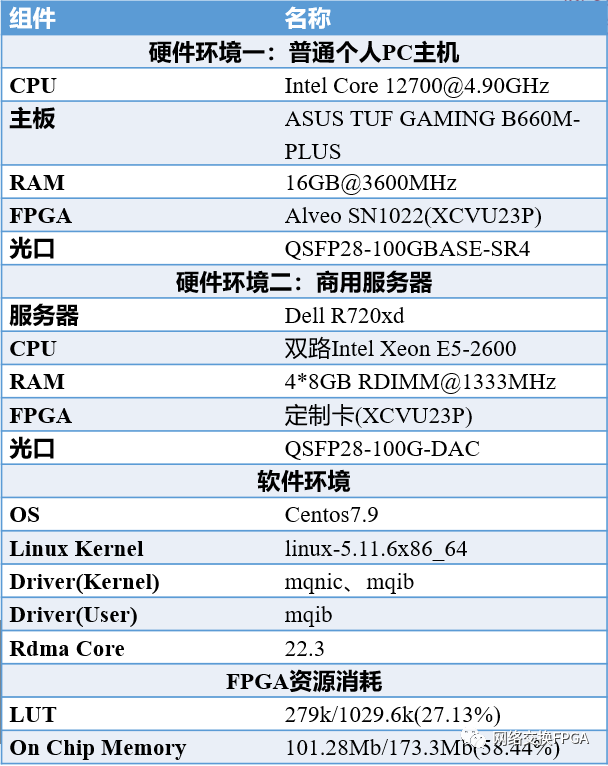

我们实现的100G RDMA网卡具体指标和性能如下:

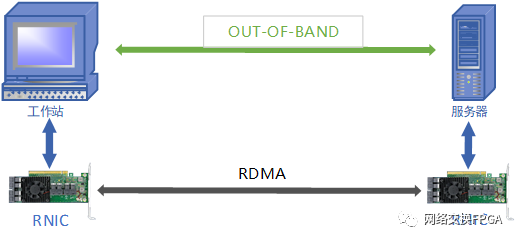

测试场景及拓扑连接图如下。

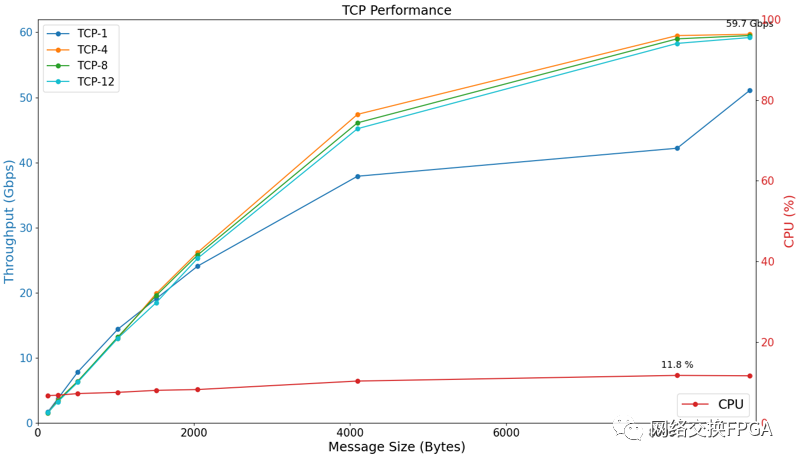

TCP测试结果如下。

TCP性能表现:实测在Linux系统环境下,端到端连接拓扑,当MTU=9214B,不进行多核优化时,本方案的iperf TCP带宽可达59.7G bps;CPU占用率为12%左右 ; TCP/IP协议普遍延迟在100–200微秒之间。

TCP测试分析:性能开销集中在内核协议栈的系统调用、内存拷贝、协议处理与中断处理等方面。这些开销占用了大量的CPU 资源,增加了数据延迟。

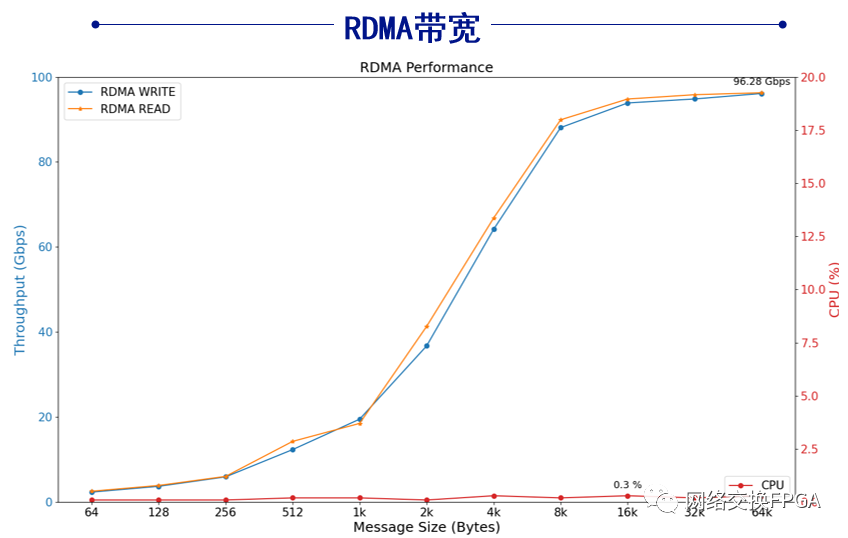

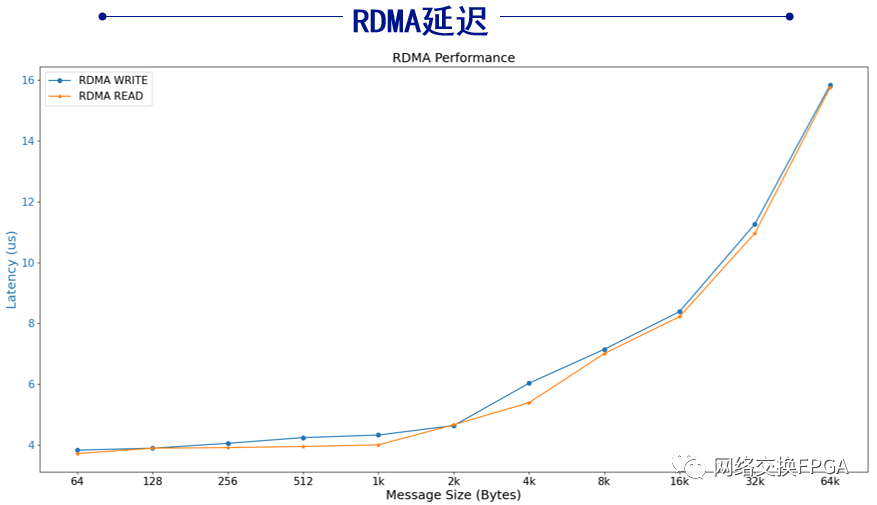

RDMA测试结果如下。

RDMA性能表现:在Linux系统环境下,相同测试拓扑,使用配套驱动程序和应用程序发送RDMA命令进行测试。本方案的RDMA网卡实测单边RDMA语义读写带宽可达96.28G bps;CPU占用率不超过0.3%;硬件端到端读写延迟低至4us左右。

RDMA测试分析:当消息大小大于8KB时,系统吞吐量可以逼近满带宽,当消息较小时,吞吐量会显著降低。原因一方面是数据帧帧头开销占比上升导致有效带宽下降,另一方面在于硬件设计无法支撑更高的消息速率。时延会随消息大小出现近似线性的增长,最大的延迟花费在PCIe链路和网络链路上,硬件的处理开销占比很小。

对比以太网和RDMA的测试结果可知,在相同的硬件条件下,使用RDMA技术的网卡可以拥有更高的网络带宽和更低的传输时延,对于云服务、数据中心等具有高吞吐量的网络业务需求场景,RDMA技术更能满足实际需要,能充分解放处理器资源,提高带宽,降低成本。

下面视频详细介绍实际测试情况:

我们未来有很多工作要做,如添加我们之前做的P4可编程的工作(【Verilog开源】一种用于智能网卡或可编程交换机的,支持P4语言的高性能开源解析器的设计),突破Corundum架构限制支持百万QP对和提升小包性能,进一步优化流量控制、拥塞管理和负载均衡等问题,进一步的提高数据中心网络的数据传输速率和稳定性。

审核编辑:刘清

-

RDMA简介2之A技术优势分析2025-06-04 6603

-

RDMA RNIC虚拟化方案2024-01-23 4115

-

RDMA网卡相比以太网卡的优势在哪里呢?2023-04-11 5466

-

NVIDIA ConnectX智能网卡驱动RDMA通讯技术在分布式存储的应用2022-11-03 2069

-

分享一种智能网卡对热迁移支持的新思路2022-07-05 4040

-

RDMA技术有助于实现网络和设备的性能提升2022-03-28 1175

-

RT-thread实现U盘升级的一种OTA方案2022-01-20 1138

-

如何选择最适合自己的RDMA网卡2021-10-21 1215

-

求一种复数浮点协方差矩阵的实现方案2021-04-29 2855

-

一种基于FPGA的多通道频率测量系统的实现方法介绍2019-06-27 1853

-

一种基于FPGA的ZigBee物理层发射机的数字基带实现方案_陈2017-03-14 1248

-

一种通用SPI接口的FPGA设计与实现2011-09-09 857

-

一种基于FPGA的误码性能测试方案2009-06-20 1183

全部0条评论

快来发表一下你的评论吧 !