Marvell高速芯片互连采用台积电最新3nm工艺,传输速率每秒240Tbps

描述

美满电子科技(Marvell Technology)技术副总裁Mark Kuemerle告诉《EE Times》,Marvell新推出的高速芯片互连技术采用台积电(TSMC)最新3纳米(3nm)工艺,应用于小芯片架构时,能够有效降低数据中心的能源消耗。

Marvell的芯片对芯片(die-to-die)互连技术可将数据传输速率提升到每秒240Tbps,比目前多芯片封装产品中使用的最先进互连技术更快45%。

这项技术将作为Marvell未来芯片设计与知识产权(IP)开发的稳固基础,透过更有效率的芯片互连,为数据中心与未来的自驾车应用提供宽带更高、效能更高,并且能源效率更佳的芯片产品。

Kuemerle表示:“多芯片系统并不一定要使用昂贵的硅中介层连接芯片。我们非常关注汽车市场对于多芯片系统的需求,因为我们很快就会在汽车市场看到和数据中心一样的趋势— —人们开始重视能源效率和成本的优化。汽车芯片的应用很快会走向多芯片整合系统。”

Marvell开发的技术等于是对台积电今年开始量产的3nm节点投下了信任的一票。据半导体产业分析公司Arete Research的数据,Marvell是台积电的前十大客户之一。

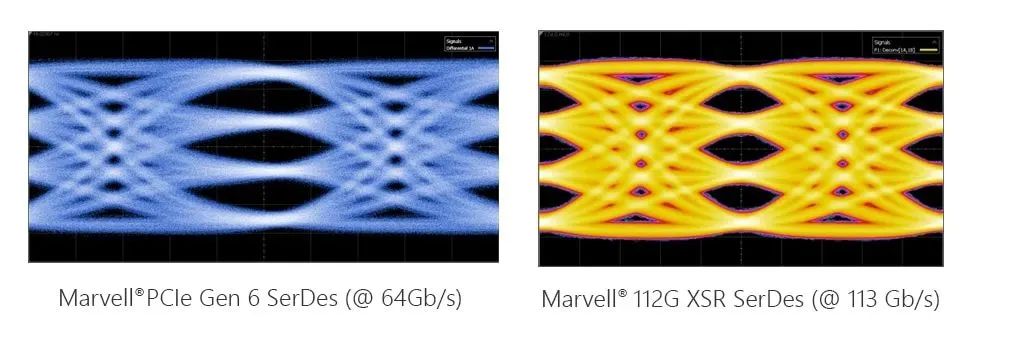

采用3nm节点的几项业界领先的技术包括112G XSR SerDes、长距离SerDes、PCIe Gen 6/CXL 3.0 SerDes以及240Tbps平行芯片到芯片互连。当初,Marvell也领先业界,率先以台积电5nm工艺为基础提供112G SerDes以及数据基础架构产品。

Marvell估计数据中心会是最早从这些新IP技术中受益的领域。

蓝色眼图表示为PCIe Gen 6/CXL 3.0优化的3nm SerDes传输高性能信号,而橘色眼图则表示为112G XSR优化的低延迟3nm SerDes传输信号。眼开的垂直高度、大小和相对对称性表示减轻了噪声与误码率。(来源:Marvell)

650 Group分析师Alan Weckel表示:“服务供应商的云端资源使用量正以每年50%的速度成长,AI应用的成长率更高达100%。Marvell生产的3nm SerDes与互连技术,将能够帮助云端服务供应商满足不断成长的速度与流量需求。”上述技术可以支持标准或低成本的重分布层(RDL)封装方式,也可以支持基于硅的高密度互连。Marvell估计新的互连技术最多可以降低数据中心的能源消耗达20%。

Kuemerle表示,如果Marvell能成功将这些组件整合于同一封装中,那么能源效率的成长甚至可以高达10倍。而这仅仅是因为这些组件距离更近了,使其间的数据通信更有效率。互连结构的功耗通常约占整体装置的三分之一。如果能将互连结构的功耗降低10倍,那一个100W芯片其中的30W就可以降低为仅仅3W。

根据《Nature》期刊中的一篇文章指出,训练一个大型AI语言模型所制造的碳足迹约为300公吨的二氧化碳(CO 2 )。这相当于一辆客机在纽约和北京之间来回125次的量。

Kuemerle表示,新的互连技术可望减少数据中心的碳足迹。

当系统中的组件彼此紧邻,就没有必要在系统上再使用驱动器和中继器。“藉由减少芯片间的通信接口,可以改善约20%的能源效率。但整体系统的建构方式都要重新思考。虽然我们改善了功耗,但也连带增加了散热的困难。Marvell内部正积极地寻找更创新的散热解决方案。”

01

汽车芯片

Kuemerle认为他们看到了新芯片技术在汽车产业中的发展潜力。

“当今汽车产业的品质标准会告诉你‘不要碰多芯片系统’,你甚至不能在封装上堆叠导孔。但我们也看到产业导入越来越多系统级的安全措施。这些在设计上具有足够安全性的汽车应用,将有办法妥善地运用多芯片的环境。”

Kuemerle进一步补充,结合了机器学习的ASIC以及先进驾驶辅助系统(ADAS)在汽车产业中充满了发展机会。此外,在PCIe接口的应用上目前也有一些新发展。

在汽车产业持续面临芯片短缺的同时,半导体公司也越来越重视汽车产业的需求。

Marvell表示,由台积电开发的3nm技术,最终也可能由其他晶圆厂代工。

Kuemerle说道:“在整个产业合力之下,新的互连技术标准化最终会让客户拥有更多选择,不论是选择代工厂或是现成的组件。这是我们所有人对这项技术的愿景。最终你将可以从厂商A、厂商B、厂商C各取需要的芯片组件,整合在一起,最后变成你的产品。”

编辑:黄飞

-

台积电产能爆棚:3nm与5nm工艺供不应求2024-11-14 1684

-

台积电3nm工艺产能紧俏,苹果等四巨头瓜分2024-06-12 1458

-

台积电3nm工艺预计2024年产量达80%2024-01-03 1884

-

iPhone15系列或采用3nm苹果A17芯片 台积电代工2022-10-10 3748

-

台积电2nm和3nm制程工艺2022-07-04 4409

-

苹果M2 Pro和M3芯片将会采用台积电3nm工艺?苹果或许没那么好心2022-06-29 3447

-

台积电3nm工艺进度超前 EUV工艺获突破:直奔1nm2021-02-19 3003

-

台积电或将在2022年下半年为英特尔代工采用3nm技术的CPU制造芯片2021-01-28 2825

-

Intel将部分芯片外包给台积电 看上后者3nm工艺2021-01-27 2649

-

台积电研发3nm工艺遇阻2021-01-05 2921

-

苹果已预定台积电3nm产能2020-12-23 2819

-

台积电3nm工艺将实现15%性能提升2020-12-21 2645

-

台积电宣布3nm Plus工艺将在2023年推出,消息称苹果将是3nm Plus工艺的首个客户2020-12-18 2742

-

台积电:3nm芯片将是2022年最先进的芯片工艺2020-11-25 7638

全部0条评论

快来发表一下你的评论吧 !