PowerLogic制作原理图

电子说

描述

PowerLogic制作原理图

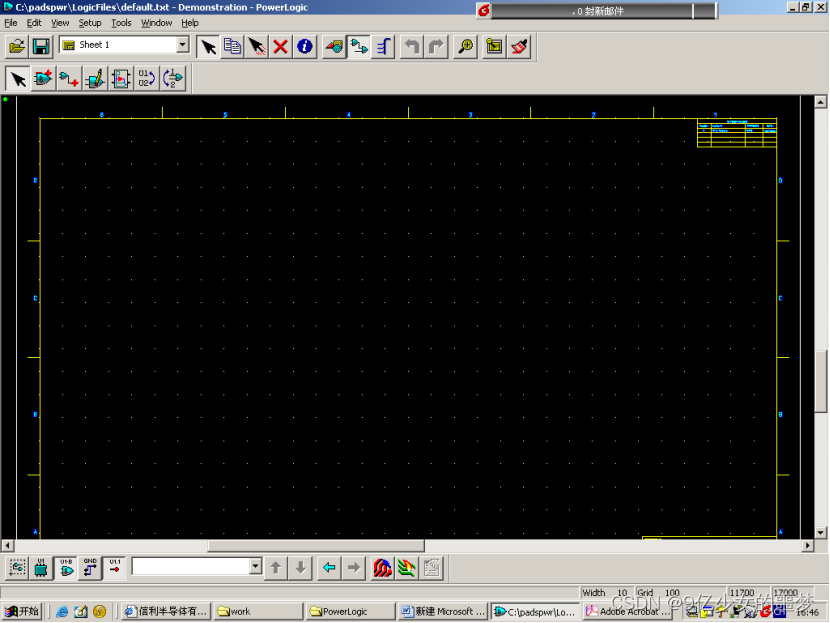

Powlogic是我们显示模块开发部制作原理图的基础软件,下面通过一个简单的原理图制作来一起学习这个基础软件。为了方便大家的学习,下面进行图形和文字相结合的方式进行学习。

这里介绍的只是对大家刚入门的学习,方面大家对本软件认识各种操作界面,在以后的工作中,还需要大家更多的努力细心体会。

当我们打开这个软件的时候,我们可以通过快捷健8,2,4,6,进行上下左右移动视图的操作,利用快捷健9,3进行扩大缩小视图的操作。快捷健7是回到原视图。快捷健5是局部扩大。

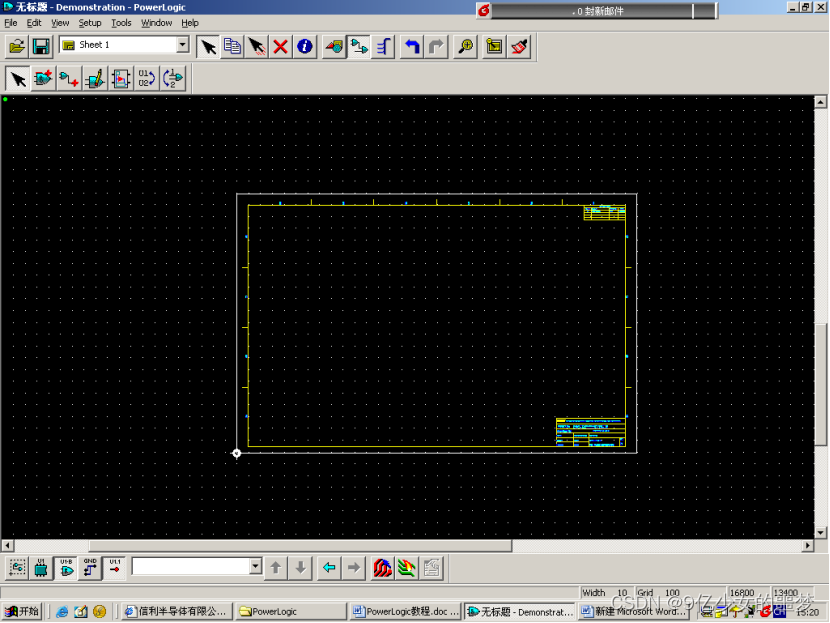

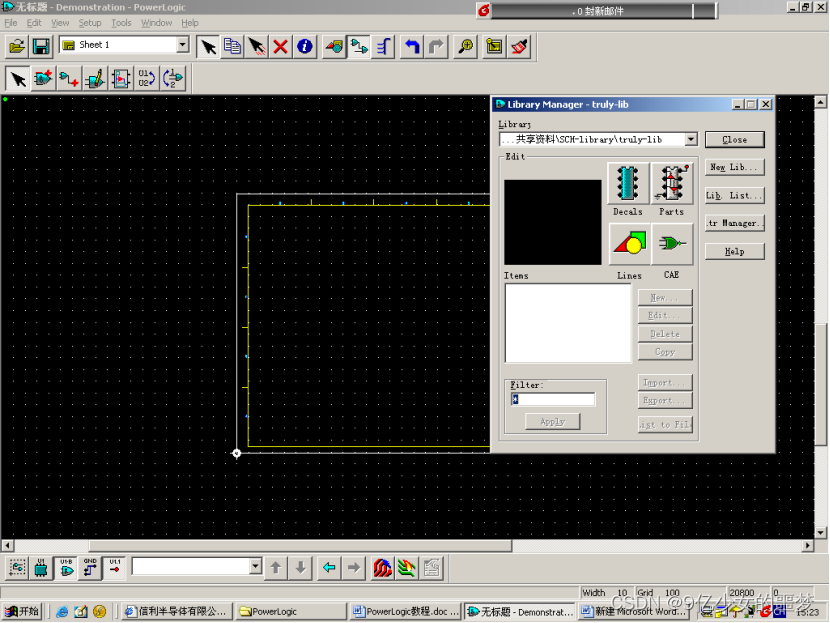

首先我们来进行库的管理我们可以通过以下操作进入库。FILE-LIBRALY MANAGER你可以看到

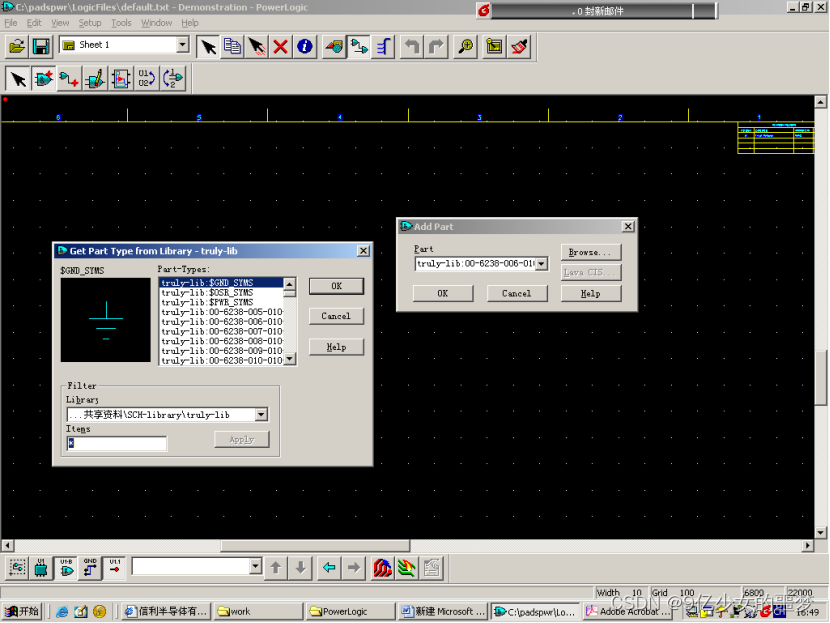

你可以通过按键NEW LIBRALY找到路径lcmserver显示模块开发部内部共享资料SCH-library里面的truly-lib文件导入,这是我们的标准文件框,以后可以从这里导入以前用过的物料原理图。

单击decals你可以查看各种元件封装。

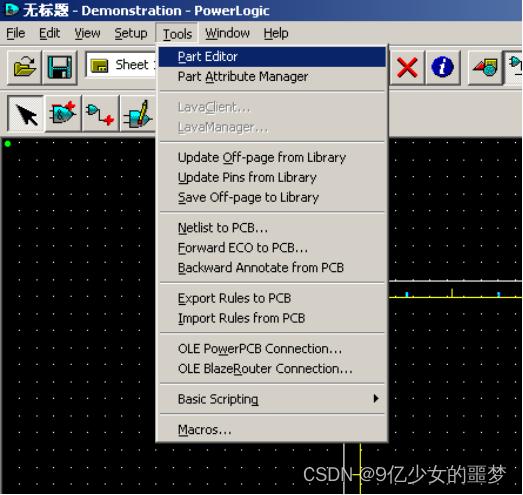

当我们需要开始制作一个元件的时候,我们可以通过以下操作进入原理图元件编辑程序。

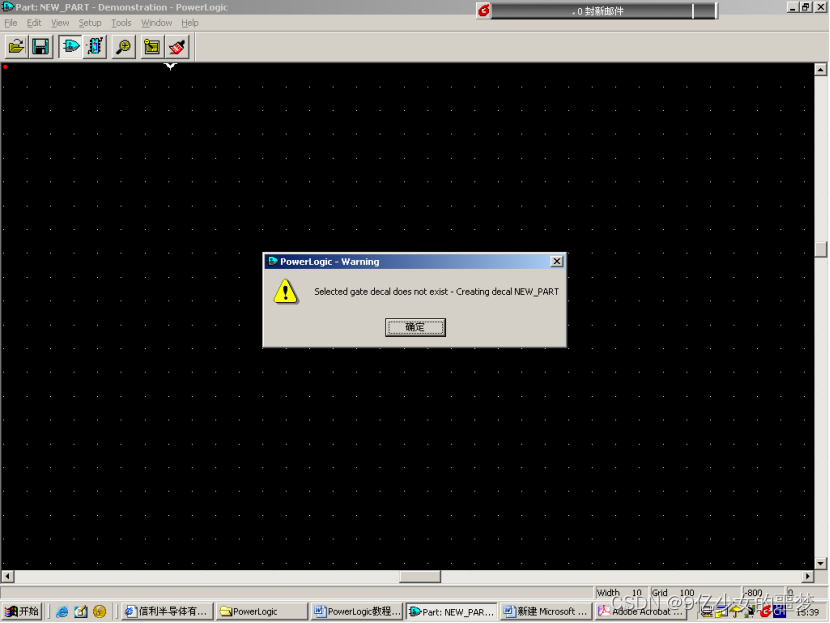

进入后, 我们可以进行如下操作,开始逻辑原理图的编辑。

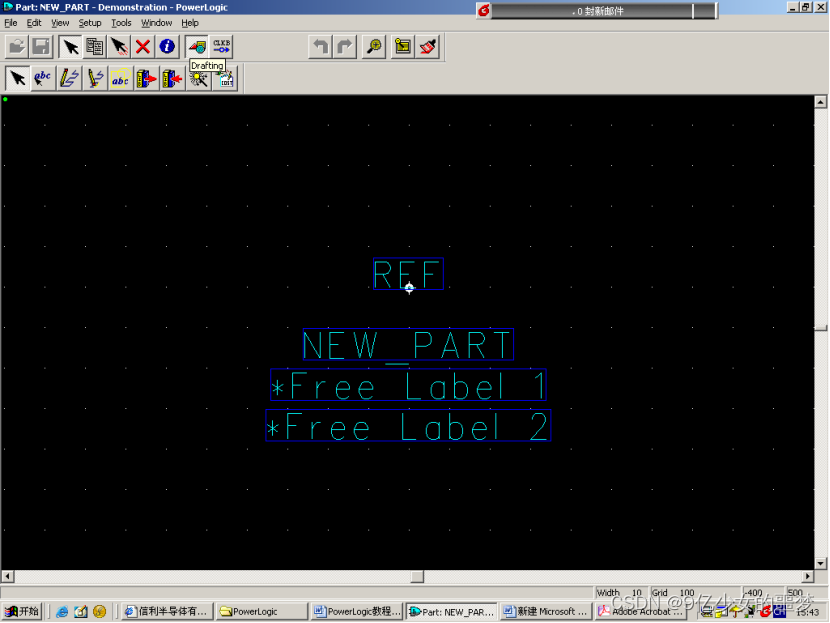

点击确定后,进入如下界面:单击工具栏drafting。

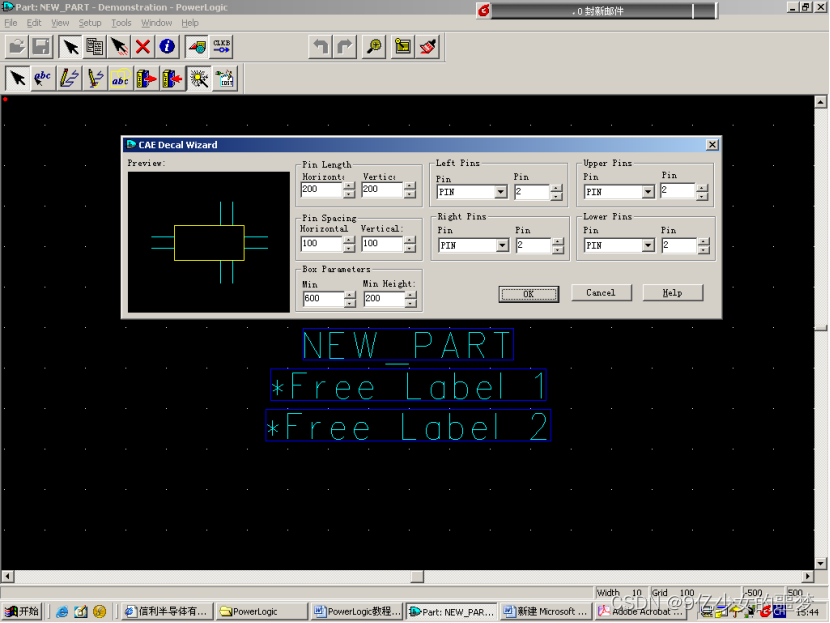

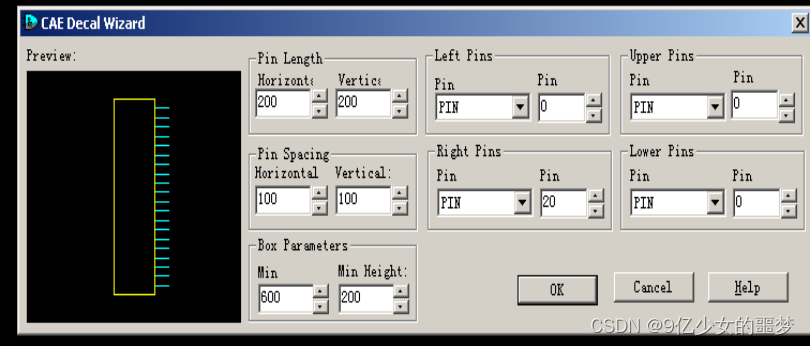

然后再在CAE 封装工具(CAE Decal Wizard)中建立CAE 封装(CAE Decals)

我们可以通过设计各种参数来达到我们设计的目的。下面我们进行设计如下:

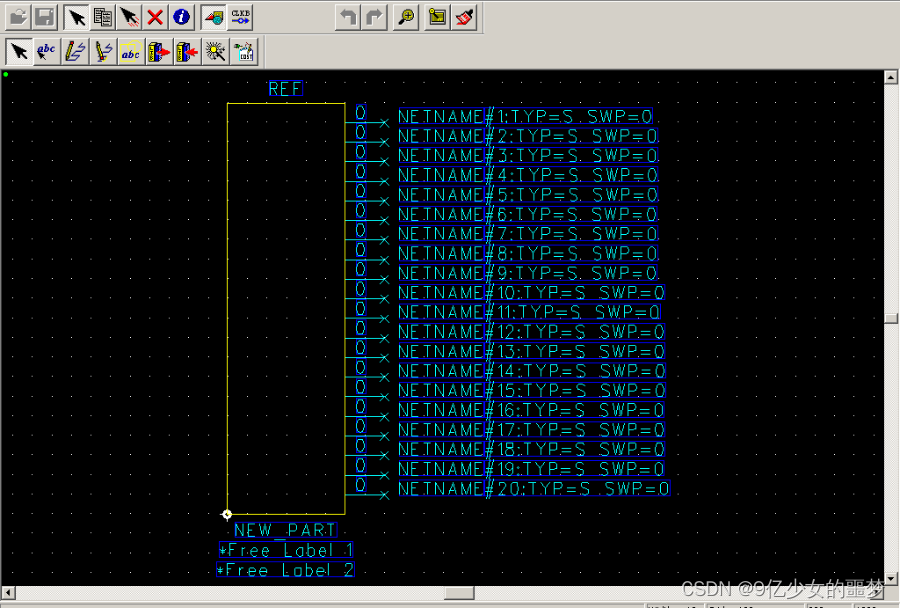

单击OK后就可以进入如下界面:

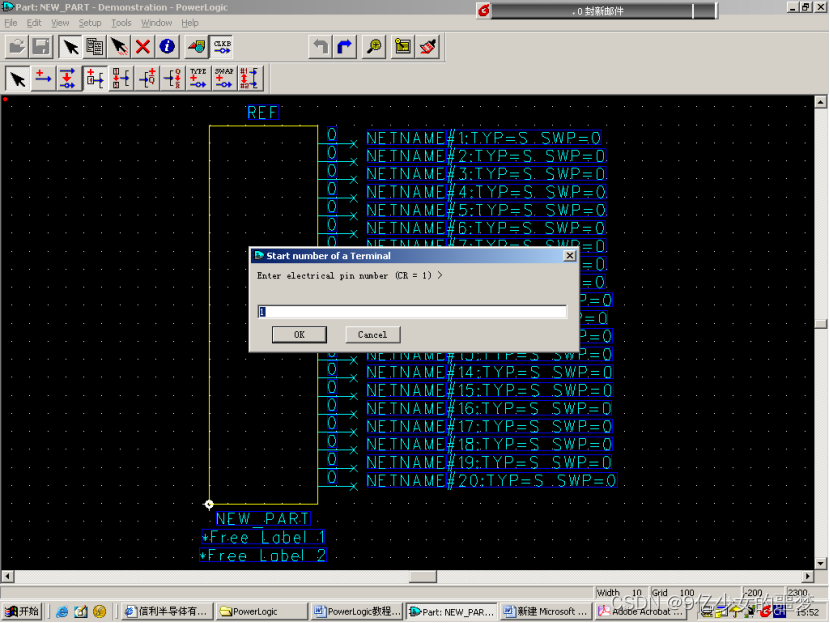

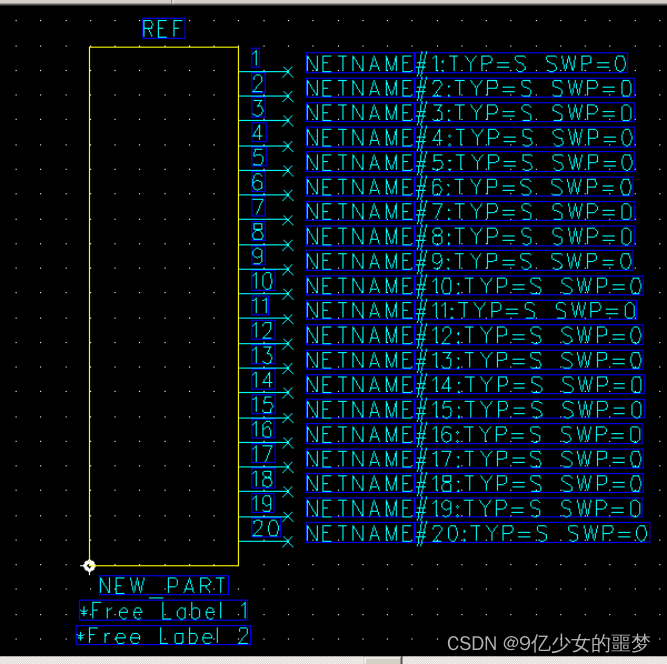

下面再通过以下操作进入如下界面,在输入框中输入我们要开始添加的pin number。然后按顺序点击,它将一次排列下去:

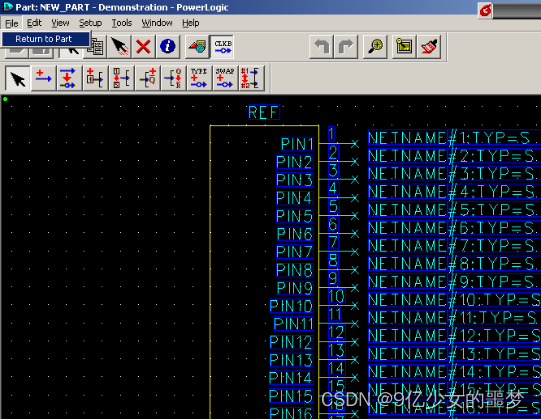

接下来是设计PIN脚的名字:为了简化,我们命名为pin1-20。点击工具栏

的set pin name工具。输入我们要命名的pin脚的名字。然后点击那个pin脚,操作结果如下:

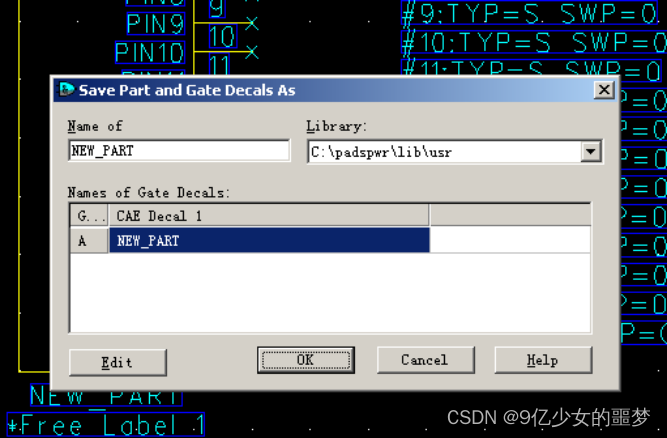

然后进行如下操作return to part

在跳出的对话框中点击yes后进入元件封装编辑窗口,再通过FILE-SAVE保存设计。在跳出的对话框中输入我们需要保存的元件封装的名字和保存路径,然后单击OK

通过操作file-exit part editor退出元件编辑窗口,进入powlogic工作空间。然后单击工具栏design进入设计元件窗口。

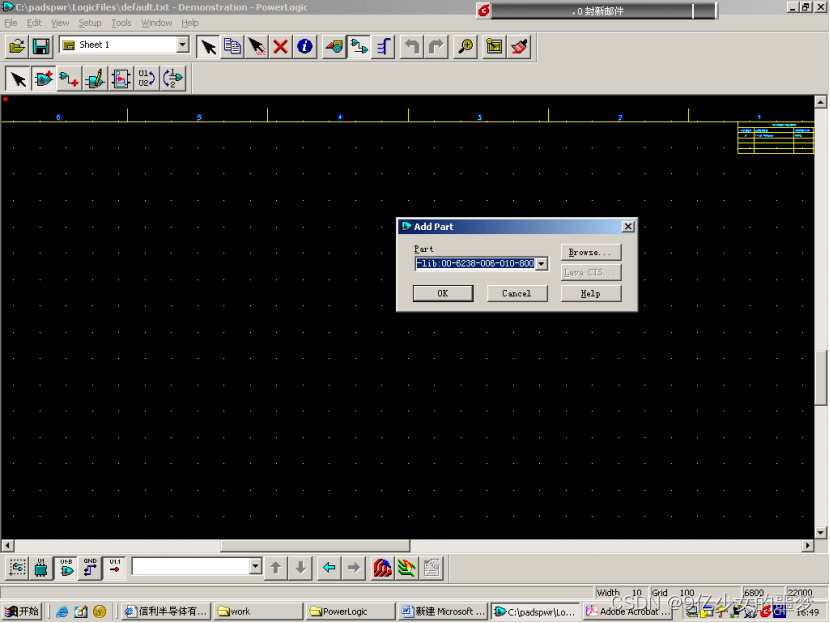

在元件设计窗口中,我们单击添加元件工具按钮。进入如下所示

点击浏览按钮找到我们设计文件的保存路径

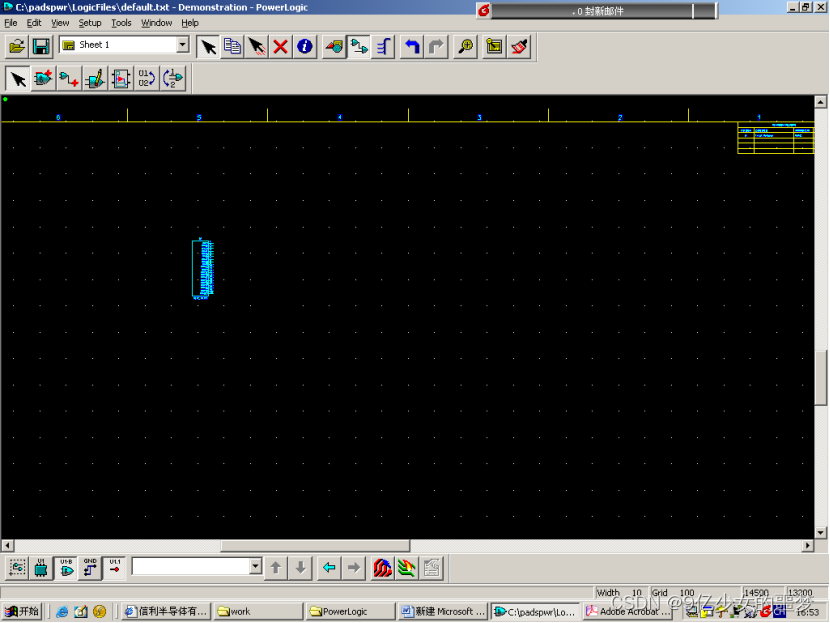

比如我们找到我们刚才设计的元件之后点击OK,再在跳出的对话框中填上元件简称,单击OK就可以把这个元件添加到适当的位置,如下所示

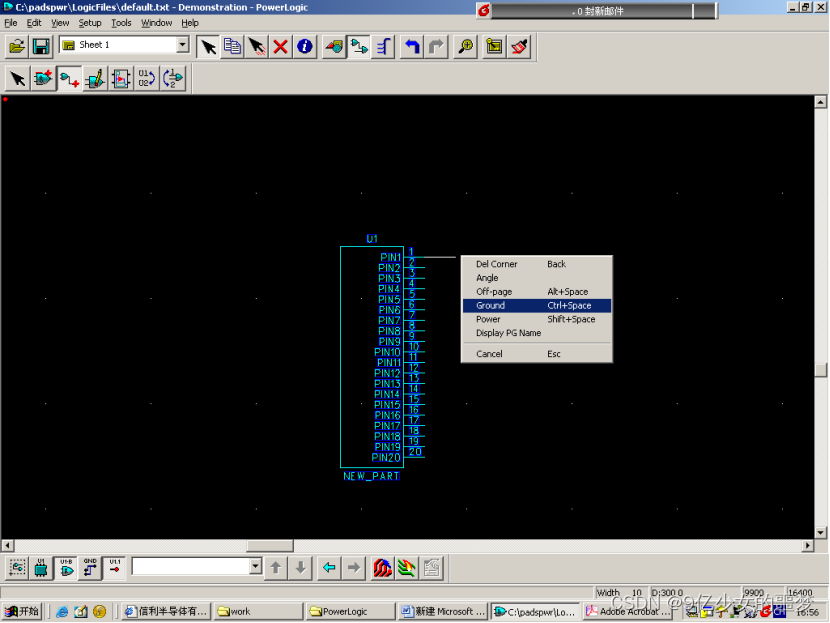

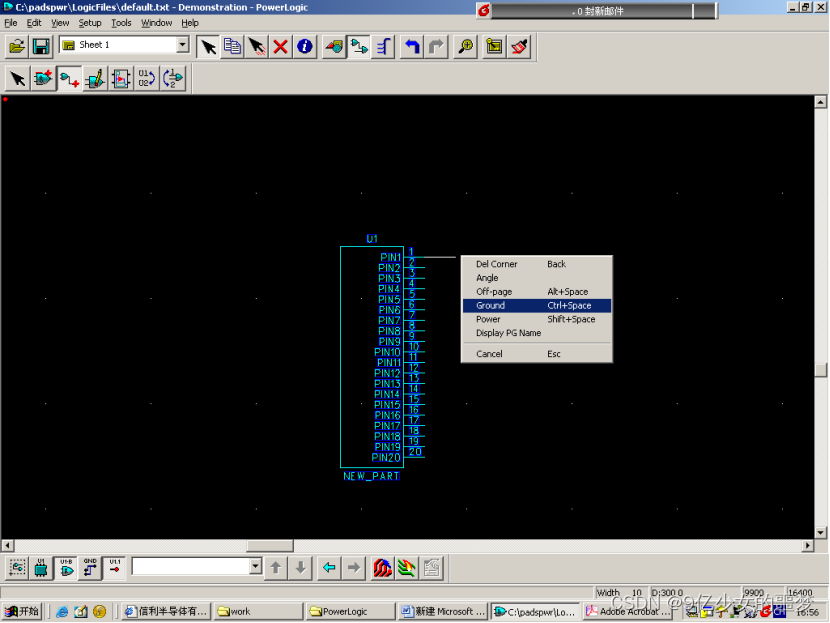

接下来我们为PIN脚添加连接如图所示,我们点击工具栏按钮添加连接之后,对各脚进行各种连接。单击右键可以进行相关的操作。如图是接地连接。

选择连接方式之后,我们也可以再单击右键改变方向。然后调到适当的位置单击左健,它会跳出一个对话框,我们可以对其命名如图

接下来就是类似的操作,我们这里就不在多说了。

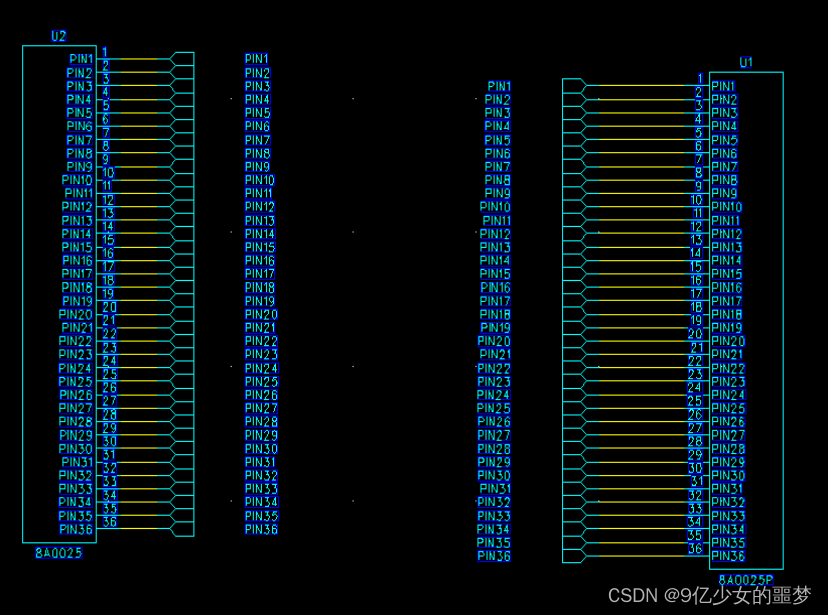

在设计好一个元件的封装之后,在建立多一个元件的封装,基本上就可以完成了。下面是完成了的一个最简单的原理图。

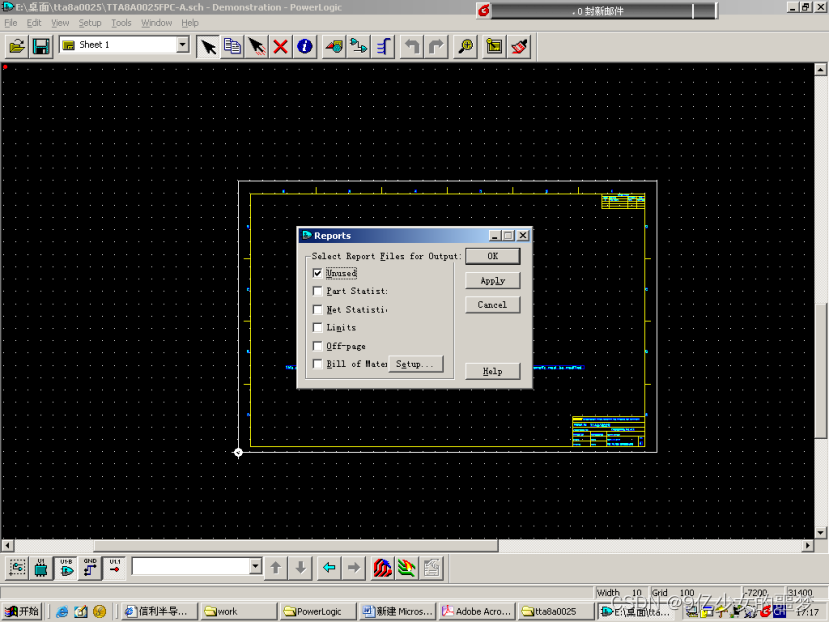

我们完成一个原理图之后需要检查一下我们的原理图有哪些错误,点击file-reports,然后在跳出对话框中选择需要生成的各种报告。点击OK生成各种报告描述。

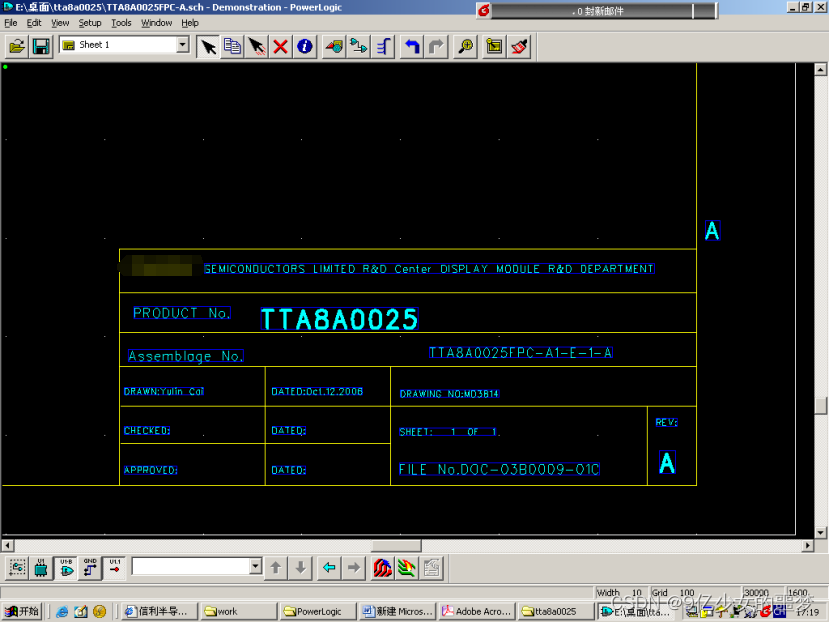

下面需要注意的是型号和集成版型号的填写。

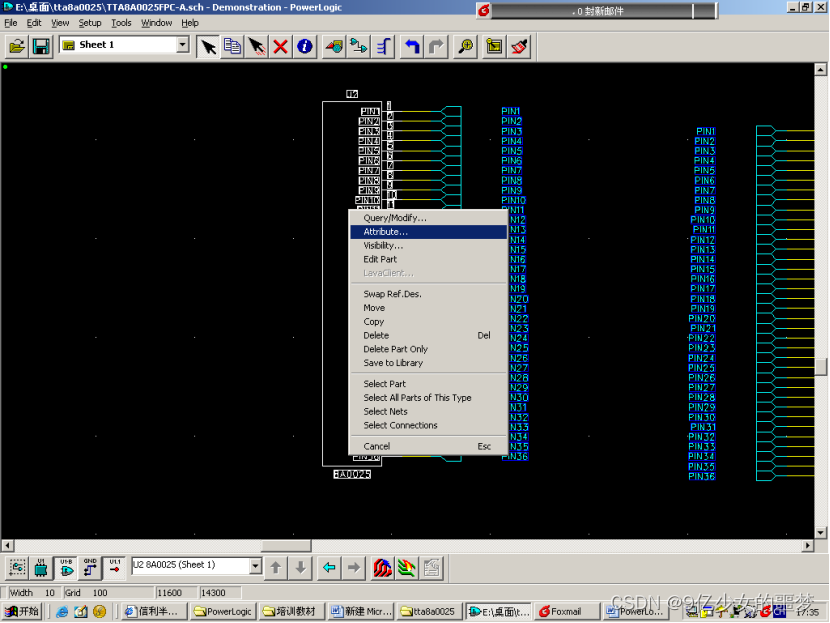

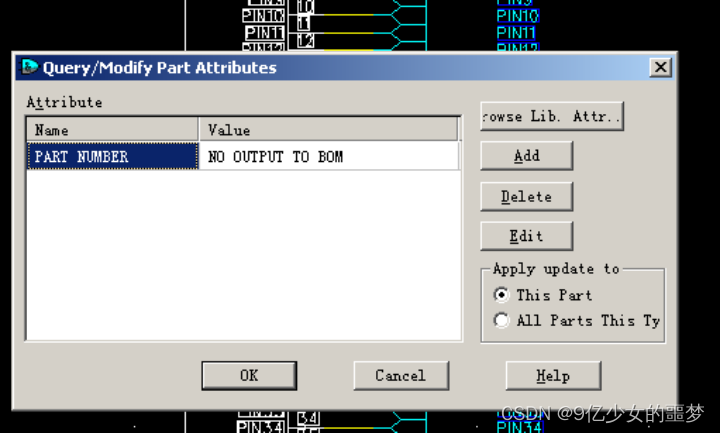

还有元件属性的描述:

点击属性后进入下面对话框:在没有元件输入的时候,我们必须填写如下:点解ADD就可以对其进行添加填写。

总结:制作原理图是一种非常细心的工作,我们必须充分考虑到各种错误避免错误的发生, 以上只是一个简单的操作,可以方便大家的简单界面的认识,在以后的工作中我们还会接触到比这个复杂多的原理图的设计。当你学习了这些基本的内容后,可以参考PowerLogic 的在线帮助(On-line Help)部分,以便得到PowerLogic 全部功能的详细介绍。为以后的工作做好充分的准备。

本文为CSDN博主「9亿少女的噩梦」的原创文章

审核编辑:汤梓红

- 相关推荐

- 热点推荐

- 原理图

- PowerLogic

- 显示模块

-

MP3的详细制作原理图+PCB2021-06-09 2992

-

彩灯制作(原理图和源代码)技术报告.pdf2018-04-24 1365

-

powerlogic2016-07-29 870

-

ds1302原理图+pcb制作2015-12-31 2127

-

光立方体制作原理图2013-09-05 19933

-

powerlogic教程2012-08-20 2340

-

PowerLogic 教程2010-08-12 1167

-

电风扇电子调速器原理图及制作2009-01-21 22118

-

请问版主:POWERLOGIC如何从原理图更新PCB2008-11-04 13140

-

POWERLOGIC 自动重新编号的的解决方法2008-07-21 19088

-

powerlogic 材料清单BOM制作过程方法2008-03-12 4175

-

powerlogic教程下载2007-11-28 1682

-

orcad &protel 转powerlogic 的工具2006-05-28 845

全部0条评论

快来发表一下你的评论吧 !