MIPI-I3C总线接口简述

描述

写在前面

访问MIPI Allliance官方网站时,发现早在2013年MIPI联盟就已建立了“MIPI I3C Working Group”,后来在2018年10月发布了I3C规范v1.0版,目前已经更新到了2021年6月的v1.1.1版。作者本人虽然在实际项目上并无I3C的应用,但出于对新事物的好奇,决定写下本篇文章。本文内容多源于MIPI Allliance官方网站、论坛、博客等,因此,它仅作为碎片化知识的整理、记录,重点分享下I3C的主要特点以及与I2C的关系。

I3C简介

I3C,全称Improved Inter-Integrated Circuit,顾名思义,它是I2C(Inter-Integrated Circuit)的横向升级版,可向下兼容。

众所周知,I2C在上世纪80年代由Philips公司推出,当初是为了简化计算机各芯片之间的数据通信方式而产生,经过数十年的发展,速度从最初的100Kbps提升到3.4Mbps(超高速模式5Mbps不常用)。I2C的应用在控制系统中已经非常广泛了,作为1种同步串行总线,相比板上其它设备间通信接口,它具有总线结构简单(2线,OD输出,SCL/SDA)、一主多从、低功耗、高可靠性等特点。

推出I3C,并非为了替代I2C总线,而是一脉相承,它主要解决了I2C现存的问题,在低成本的产品中,I2C依然是高性价比的选择。

在I2C中,这些局限性包括每个从设备拥有一个7位的固定地址,在挂载多设备时可能存在 I2C总线设备地址冲突,I2C还有不带内中断或目标设备复位(需要额外的导线/引脚)、较低的数据速率等缺陷。在SPI中,一些主要局限包括每个器件有一个芯片选择引脚但需要四条通信线路,以及由于缺少明确定义的标准(如数据位宽)而存在许多不同的实现方式(如CPOL/ CPHA四种工作模式)。

借用NXP网站的描述:I3C“在标准CMOS I/O上,它支持10Mbps的最低数据速率,具有更高性能的高数据速率(HDR)模式的选项,与现有选项相比,性能和功耗效率大幅提升。它还提供多主机支持、动态寻址、命令代码兼容性和高级电源管理功能(如睡眠模式)的统一方法。”总结成一句话:它非常适合应用于高速、多主机、多从机(传感器)等应用场景。I3C总线的速度提高了,功耗降低了,效率提升了,在需要更精简、高性能、高速度、可扩展和具有成本效益的通信应用中,I3C应运而生。

应用场景

物联网(IoT)行业、移动设备、汽车系统、服务器、工业设备等。

面向传感器应用:用于需要精简连接和多传感器管理的场景,统一碎片化的传感器接口。

希望提高通信速度和效率、同时需要简化总线接口的应用场景。

I3C主要特性

I3C接口特性如下:

1. 速度:SDR模式(单边沿采样)基础速率12.5Mbps(最低10Mbps),HDR模式(双边沿采样)理论最大速率39.5Mbps(实际有效传输速率在33.3Mbps左右)。

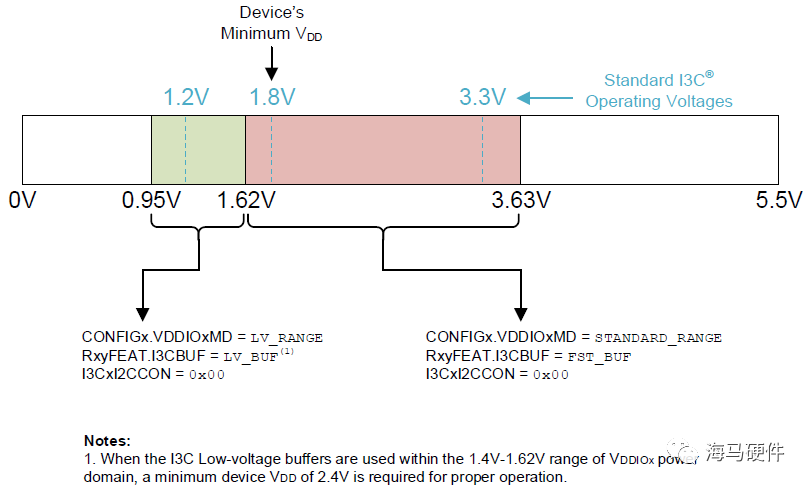

2. 功耗:最低支持1.2V电平(支持1.8V/3.3V,不支持5V)。在同样的电平标准下,整体功耗远小于I2C。

3. 总线结构:两线(SDA/SCL)串行接口,开漏/推挽可灵活切换,支持多主多点功能(Multi-Controller and Multi-drop capabilities)。

4. 热加入机制(Hot-Join):I3C协议支持热加入机制,以允许从设备在已配置后加入I3C总线。

5. 动态地址(transaction ):支持,从设备地址由当前的主控制器(Active Controller)初始化后分配,通常在上电后完成。

6. 中断机制(In-Band Interrupt):支持内中断,从设备通过I3C总线产生中断并通知主控制器,节省1根INT线。

7. 向下兼容I2C:在基础模式中兼容I2C总线。

Ø I3C特性介绍

1. 传输速率

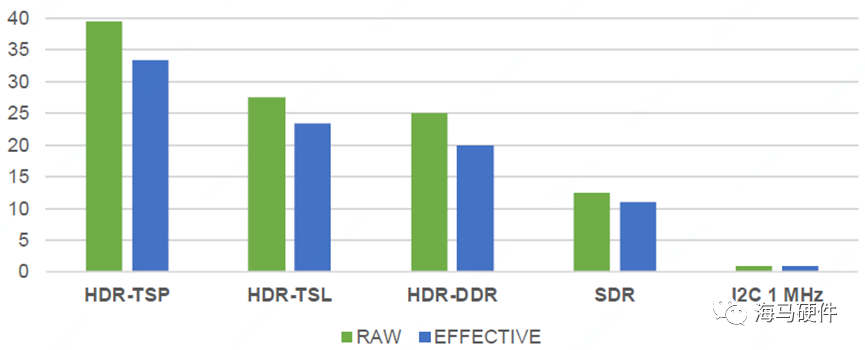

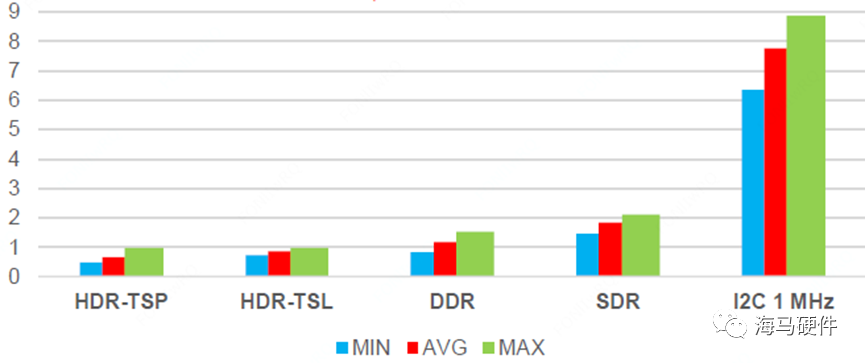

I3C的理论传输速率相较I2C提升了12.5 倍至 125 倍。如下图所示,I3C支持多种速率的工作模式,其中,

SDR 模式:12.5Mbit/s,Single Data Rate Mode,I3C的默认模式。

HDR-DDR模式:25Mbit/s,High Data Rate Mode,Dual Data Rate Mode。

HDR-TSL模式:30 Mbit/s,Ternary Symbol Legacy-inclusive-Bus。

HDR-TSP模式:39.5 Mbit/s,Ternary Symbol for Pure Bus (no I2CDevices)。

值得说明的是,MIPI联盟定义了I3C复杂的协议规范,但HDR-TSP模式和HDR-TSL模式并不被包含在I3C的基础结构(I3C Basic),作者的理解是,若要实现这两种HDR模式,需要专门的IP,而且对主从设备工况的要求也更严苛。因此作者将I3C HDR和I3C Basic理解为两个概念,它们拥有不同的总线架构、时序、协议规范。相比完善、高灵活度和高效的I3C接口,I3C Basic是一个降低了性能、低复杂度的版本,适用于板内设备连接应用,比如传感器和内存接口。I3C Basic满足开发者和普通用户组织的设计与应用。个人理解,从普通应用层面来说,I3C最大仅支持25Mbps速率(HDR-DDR模式)。

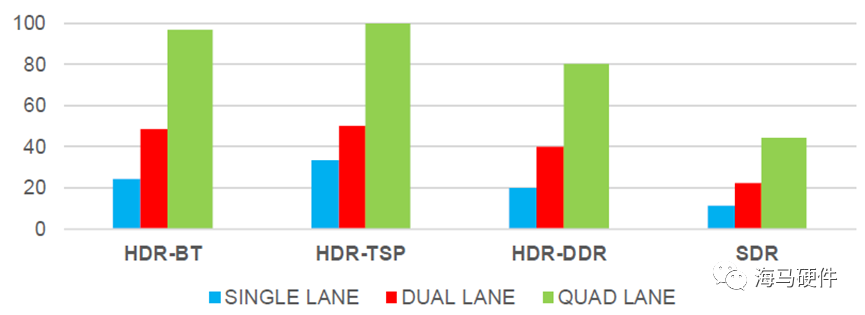

另外,上面提到的I3C速率指的是单通道模式下的理论和实际速率,如下图所示,I3C还有多通道模式(Multi-Lane,HDR-BT)。多通道指的是使用多根SDA数据线,如双通道(HDR-BT DUAL)、四通道模式(HDR-BT QUAD)。在HDR-BT(HDR Bulk Transport)四通道模式中,最高速率可以达到100Mbps(实际速率约97Mbps,即12MB/s),它是SDR模式的8倍。HDR-BT支持SDR、HDR-DDR、HDR-TSP。同样地,多通道HDR-TSP和SDR并不被包含在I3C Basic版本中。

实现I3C高性能/高效率通信(HDR模式),需满足以下条件:

在布局上,从设备(Targets)靠近主设备(Controller),且走线无延迟;

每根线上的最大漏电流:4μA;

驱动端(主/从)的内部等效电阻:90Ω;

总线的主时钟频率:12.5MHz;

总线工作在1.8V电平;

总线上拉电阻取值:2833Ω;

高低电平宽度保持一致(Equal probability for 1 and 0 on data transmission,猜测是要求在保证可靠的建立保持时间基础上,提高传输效率)。

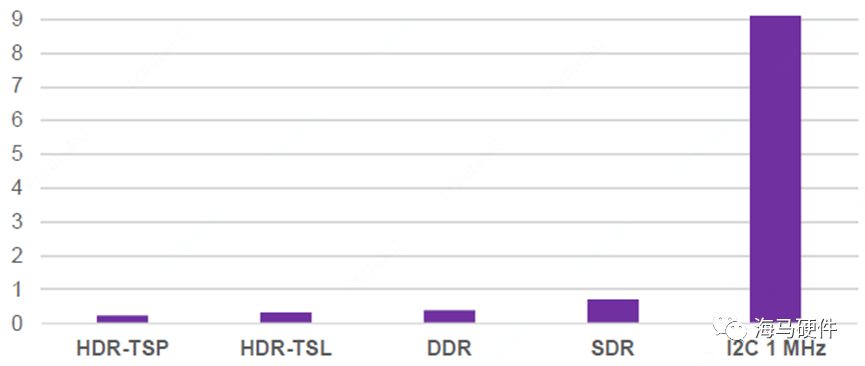

在传输效率上,同样传输1kB的数据量,I3C消耗的时间(ms)远小于I2C。

2. 功耗

1) 功耗对比

在SDR模式下,同样传输1kB的数据量,单通道I3C的功耗要小于单通道I2C约6mJ,降低约70%(从柱状图来看)。I3C也有睡眠模式(暂未详细了解)。

2) DC特性

这里主要介绍下I3C支持的电平标准。

I3C支持1.2V、1.8V和3.3V电平标准(CMOS,阈值30%/70%),它甚至支持更低电平(如1.0V)。I3C在5V的CMOS电平标准上表现并不突出,但如果有足够的驱动强度,且/或降低传输速度的情况下,可扩展支持5V(直译过来很绕)。

当工作在推挽(Push-Pull/Totem-Pole)模式时,SDA信号可以达到更高的速度,此时总线电容须不大于50pF。在1.0V的标称工作电压支持100pF容性负载,以用于新用途,如DDR5中的串行状态检测(SPD),由于速度提升,可扩展从设备的数量,提高了系统的启动速度。

有关DC详细参数见Specificationfor I3C Basic.pdf 中的“I3C Electrical Specifications”章节。

3. 总线结构

I3C有2种总线结构,分别是开漏和推挽。保留开漏结构是为了兼容I2C的低速应用,而I3C在SDR/HDR高速模式中使用了推挽方式,它的驱动能力更强,但需要控制器针对性的设置。

I3C有个很重要的特点,即规范上定义了I3C两种工作模式,分别是同步时序控制模式和异步时序控制模式(AsyncMode 0-3)(这里作者还不理解,后续再研究),异步时序控制模式指的是主机和从机工作的时钟源、时钟频率、时钟精度不同。

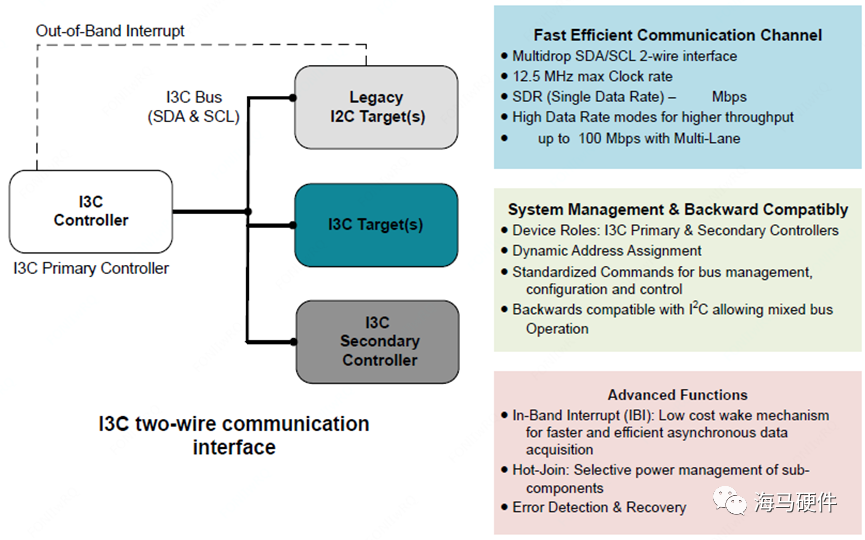

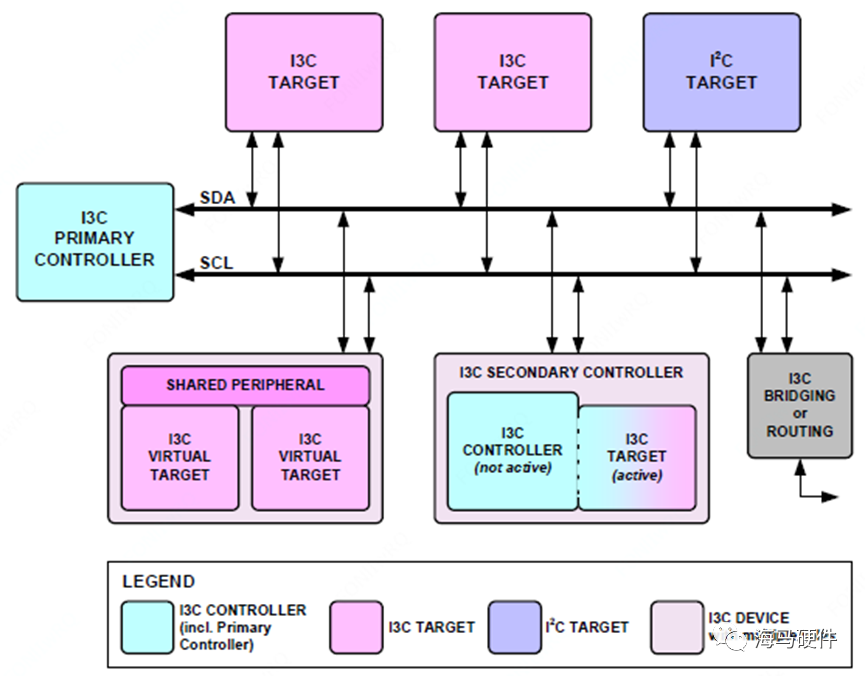

总线上挂载的各个设备连接关系如下图所示。这里先来个名词解释:

I3C PrimaryController:主控制器,可以支持或不支持HDR模式。

I3C SecondaryController:辅控制器(第2控制器),可以支持或不支持HDR模式,可以作为主机。

I3C Target:I3C从设备(目标设备),可以支持或不支持HDR模式。

I2C Target:不支持HDR模式,指的是传统的I2C低速设备。

当所有设备共同挂载到1个I3C总线时,总线被命名为“混合快速总线(Mixed Fast Bus)”,若仅有I3C设备时,被成为“纯总线(Mixed Bus)”;还有1个“混合低速/受限总线(MixedSlow/Limited Bus)”。混合快速总线和混合低速/受限总线的主要区别就在于I2C设备是否存在50ns的尖峰滤波器(下文会提到)。

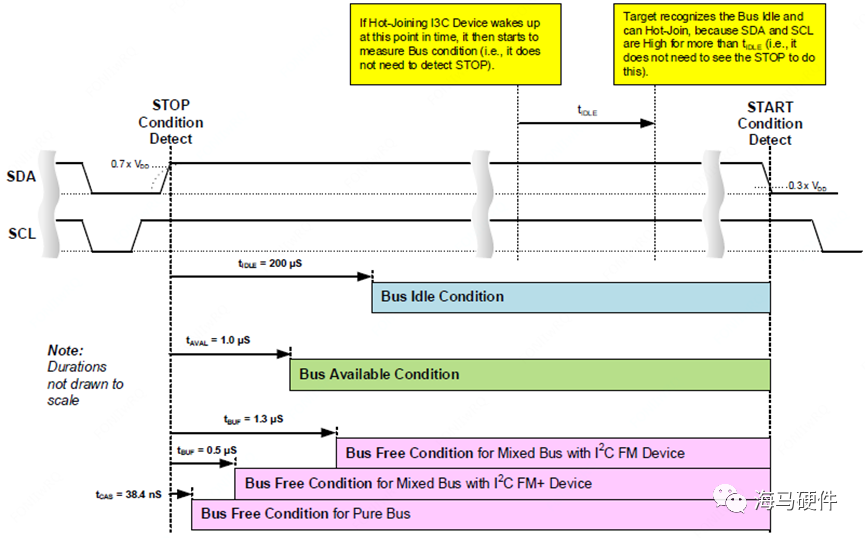

4. 热加入机制(Hot-Join)

在I3C 中,目标设备被允许加入已配置的总线,并由 I3C 控制器分配一个动态地址。凭借I3C 中的这种热加入功能,可以在运行期间开启和关闭总线上的某些器件,从而实现“分段式供电”设计,仅在需要时才使相关单元保持活动状态。在一些应用中,如果不希望或不可能让系统断电(例如在服务器或无线基站中),或必须正确设计热插拔功能(在背板或外部卡中)时,此特性将非常重要。

5. 动态地址

I3C有着一整套通用命令字的集合,可以通过这些命令字实现动态地址分配、检查当前总线状态、时间控制、IO扩展等等功能。I3C从设备地址由主设备仲裁,但并不是所有设备地址都可用,部分地址是I3C标准所保留的,用于后期拓展或者错误仲裁。

6. 中断机制

I3C无需增加外部中断线即可实现中断响应。

I3C带内中断,有地址仲裁特性(In-Band Interrupt,IBI),当从机产生中断,IBI向主机发送中断信息、地址和其它信息。若有多个从机中断,较低的地址具有较高的优先级(具有较低值地址和较高优先级、带内中断的从机对控制器的处理请求要比具有较高值地址和较低优先级的从站更快<直译过来很绕>,原文:Targets with lower valueAddresses and higher Priority Levels have their In-Band Interrupts andController Role Requests processed sooner than Targets with higher valueAddresses and lower Priority Levels)。地址仲裁特性对热插拔、动态地址分配以及多主机申请同样有效。

7. 向下兼容I2C

I3C与I2C总线数量(2根,SDA/SCL)相同,在同一组I3C总线上可以同时挂载I2C设备(工作速率不同);

I3C 总线支持传统 的I2C 通讯,I3C通信使用推挽结构,I2C通信使用开漏结构;

I3C支持动态地址分配,也同时支持传统 I2C 设备的静态寻址;

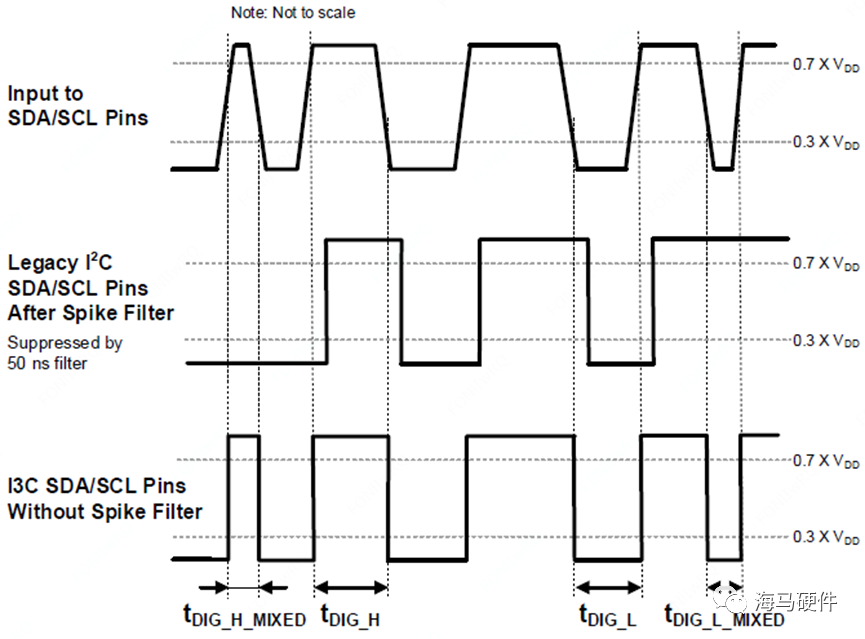

如下图所示,I3C总线可以将时钟速度更改为允许速度范围内的任何频率。相比之下,当传统I2C设备挂载到混合快速总线中,为了不引起传统I2C器件参与到总线进来,I2C需要拥有50ns Spike Filters,也就是说,必须确保总线上的SCL高电平周期比Spike滤波器短(SCL时钟频率大于12.5MHz),每个传统I2C 从机的SCL线需要配有 50ns 尖峰滤波器,目的是忽略掉下图的“DIG_H_MIXED”高电平段(脉宽范围32~45ns),以防止Legacy I2C器件受到干扰(作者的理解是,这一段是I3C SDR/HDR模式的最小脉宽,芯片内部增加滤波电路将其滤掉)。

I3C基本时序(SDR)

1. I3C通信流程概括

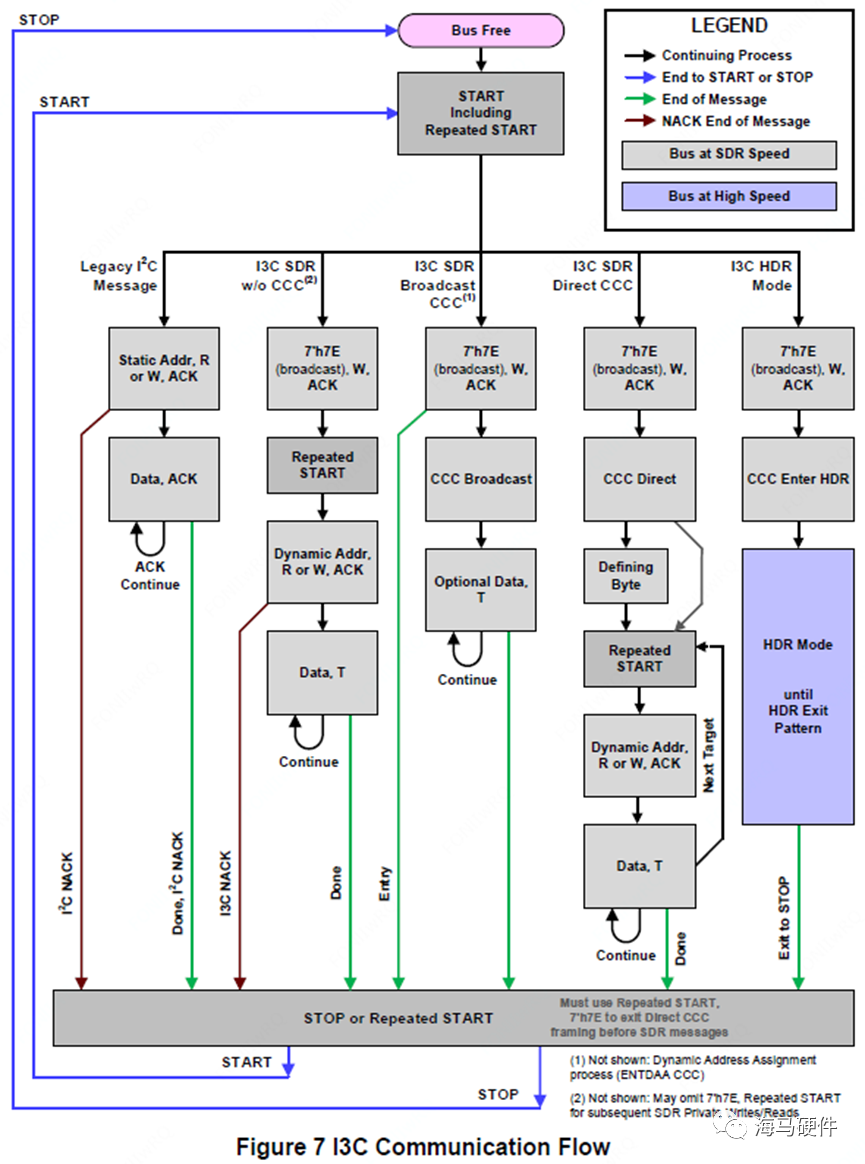

I3C支持多种通讯方式,先贴一张I3C通信总体流程图(4.1 I3C FundamentalPrinciples 章节):

由于还没去详细的研究时序,这里先简要的说明下:

首先,I3C完整的帧包含START、Header、Data、STOP,这个与I2C和其它总线接口都大同小异。在START之后,主机利用Header来寻址从机设备(静态地址、动态地址、广播地址、热加入地址)。Header允许总线仲裁,从机设备也可以将Header仲裁用于多种目的:内中断,热加入和辅助主设备功能(I3C总线只能有1个主控制器控制总线,总线上辅助主设备可通过某种机制使用来替代主控制器,也就是多主机机制)。

上图中的CCC(CommonCommand Code,通用命令代码)是全局支持的命令,可以直接传输到特定的I3C从设备,也可以同时传输到多个I3C从设备,它可以在同一条总线上执行多个命令。它是主从设备之间的一种通信机制(网上有人把CCC比喻成Linux的Shell指令),通常由主设备发给从设备,用于获取和设置从设备的功能、配置信息,它提高了主设备对从设备的管理能力。CCC也支持双向通信,用于确认主从双方的指令。CCC不适用于传统I2C接口。

在启动或重复启动之后,CCC的地址始终为7’h7E,而读写Rn/W位应始终为W。一旦分配了I3C从机,所有I3C从机都将识别7’h7E广播地址和它们自己的动态地址。 在分配I3C动态地址之前和之后,I3C主机均应发出CCC命令。CCC命令分为广播(Broadcast)写、直接(Direct)读/写、直接写、直接读取四类(具体有点复杂,详细了解CCC,需要再熟读5.1.9章节),广播命令码有255个,范围0x00 - 0x7F,上图中7’h7E是广播地址,直接命令码范围是0x80 - 0xFE。

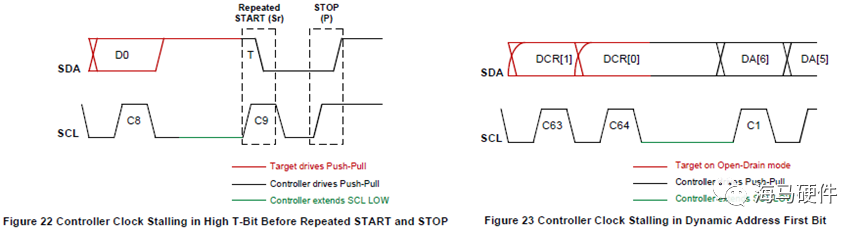

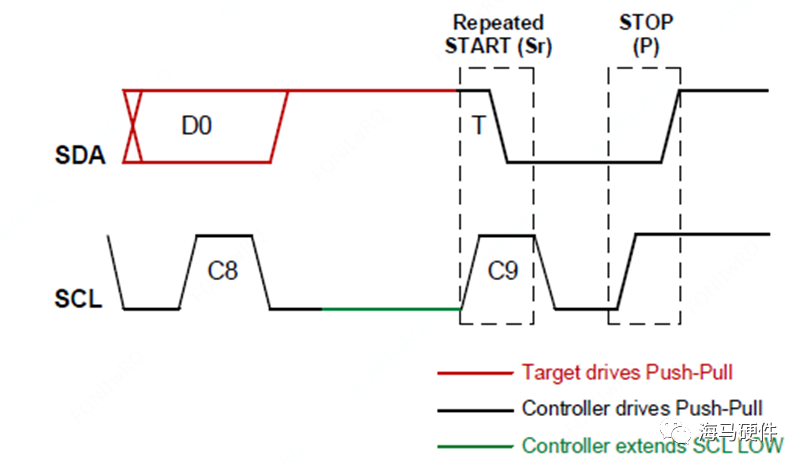

后面是数据的传输,数据按照SCL上升沿边沿(HDR模式是双边沿采样)进行采样。上图中,传统I2C是在数据传输完成后由接收方发送ACK或NACK(即框图中的DATA.ACK),而与传统I2C不同,在I3C SDR模式中提到了“Data. T”字样,即T Bit,它是Transition Bit(过渡位)的简称,作为ACK/NACK机制的替代方式而推出。值得说明的是,T Bit是第9位数据,它是作为奇偶校验存在的,即使I3C SDR没有ACK机制,但总线协议中有一些错误事项的标志位可以用来替代NACK事件的发生(此处存疑,待研究),CCC命令也定义了数据读写的最大长度,会提前通知目标设备(从机)。

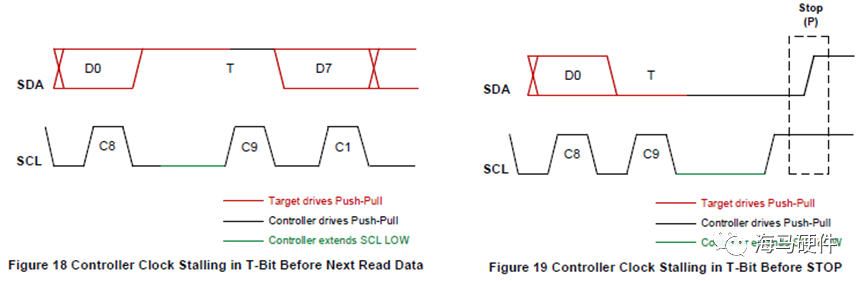

当主机(Controller)从从机(Target)中读取返回的数据,产生的T-Bit是最后1个数据位,不像I2C,从机无法控制其发送数据的数量,I3C的从机通过返回T-Bit来控制发送数据的数量,它还允许主机在必要时中止读取。

如下图所示,当从机返回T-Bit为0时,意味着要结束发送,反之返回T-Bit为1,意味着继续发送,并监控SDA线。如果SDA在下一个SCL的下降沿保持高电平,则继续发送下一组数据;如果SDA在下一个下降沿的边沿(重启)为低电平,则主机中止数据传输,且从机不继续发送,可以使用RSCIF标志位来监视这种情况(I3C有很多标志位用于检测总线状态,比如大家熟知的用于检测起始位的SCIF、结束中断标志PCIF、应答接收中断标志I2CACKIF、地址匹配标志SADRIF、动态地址匹配中断标志DADIF等)。

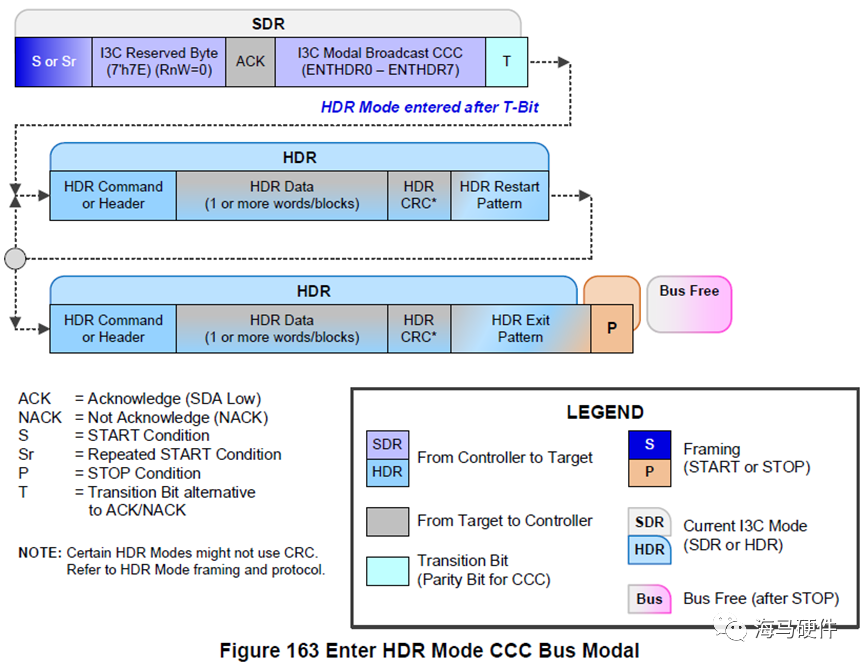

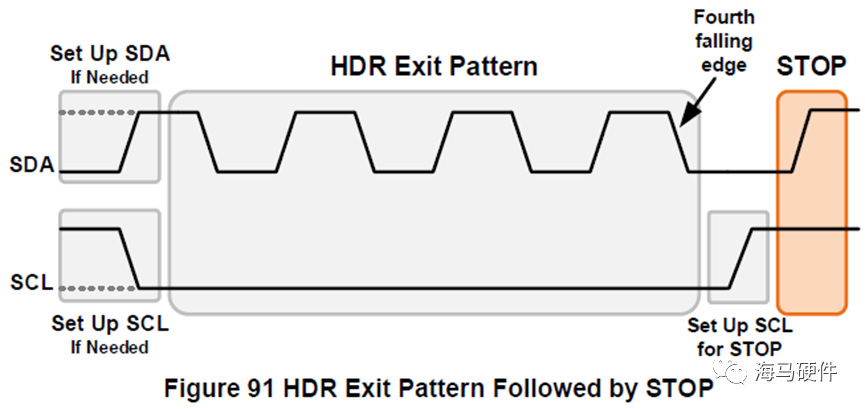

顺便提一下,HDR的机制很特殊,它的时序与传统I2C和SDR模式显著不同,比如若要从SDR进入或退出HDR模式,需要发送特定的序列。

最后,当一个序列的数据发完,会发出停止位,总线进入IDLE状态,随后,重启START,进入下一个周期。

2. I3C SDR基本时序

这里简要说明下I3C在SDR模式下的时序(HDR稍显复杂,比如HDR-DDR是双边沿采样、带CRC)。

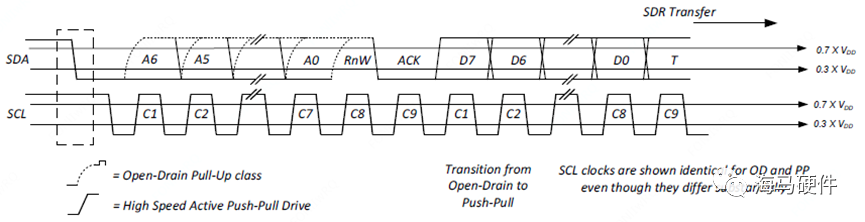

I3C SDR模式的时序与I2C总体上一致,二者的区别主要体现在时钟速率上,相比I2C,I3C对SCL/SDA的建立保持时间更加严格,I3C可降速支持I2C。

1、起始位与停止位:

I3C的START、STOP机制与I2C一致,即,在时钟边沿翻转为低电平之前和时钟边沿翻转为高电平之后,数据线分别产生下降沿和上升沿的跳变。

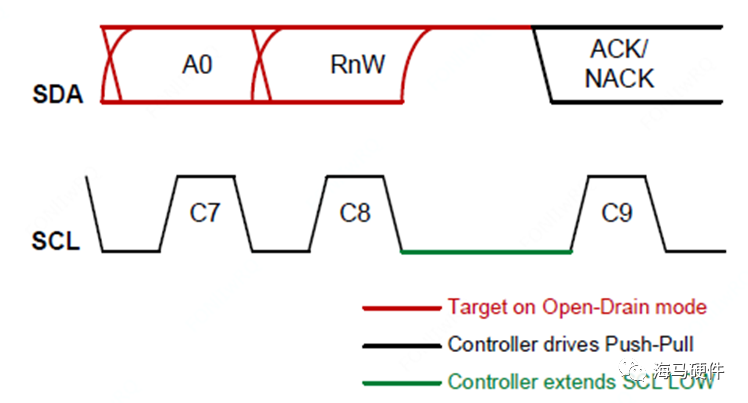

2、地址/读写/数据位(Legacy I2C/SDR):

3、应答位:与I2C类似,在第9位产生ACK/NACK或T Bit。

不同速率模式/总线结构(OD或Push-Pull)下的建立保持时间指标可参考文档Specification forI3C Basic.pdf中的“6.2 TimingSpecification”章节。

不同板载通信总线的对比

| 通信接口 | UART | I2C | SPI/QSPI | I3C |

| 通信机制 | 异步 | 同步 | 同步 | 同步 |

| 总线结构 | 2线,半双工 | 2线,半双工 | 4线,全双工 | 2线,半双工 |

|

理论最大 通信速率 |

10Mbps | 3.4Mbps | 60Mbps | 39.5Mbps |

| 主设备 | 单一 | 单一 | 单一 | 支持多个 |

| 从设备 | 点对点 | 多个 | 多个 | 多个 |

| 软中断 | 不支持 | 不支持 | 不支持 | 支持 |

| 热加入 | 不支持 | 不支持 | 不支持 | 支持 |

| 从设备地址 | 不支持 | 静态地址 | 静态地址 | 静态和动态地址 |

审核编辑:汤梓红

-

什么是I3C接口 I3C和SPI接口有什么区别2024-03-05 6013

-

意法半导体推出支持MIPI I3C的高精度数字电源监测器芯片2023-11-27 1800

-

I3C Introduction是什么意思2023-07-22 2044

-

关于MIPI I3C Sensor接口标准制定的介绍和应用2019-10-18 6225

-

基于MCS-51单片机I2C总线接口电路的设计2019-10-15 4384

-

符合最新MIPI I3C规范的DesignWare IP提供高带宽和可扩展性2019-08-07 5516

-

MIPI联盟公开其传感器接口规范MIPI I3C2018-06-30 5724

-

基于MIPI I3C规范从I2C无缝连接I3C的关键优点2017-11-16 21910

-

基于CPLD的I2C总线接口设计2011-02-12 1406

-

PCA9564 并行总线转I2C总线接口芯片简介2010-03-10 1626

-

I2C总线接口模块设计2009-11-02 803

-

基于S3C44B0X的I2C总线设计2009-08-19 782

-

用Verilog HDL实现I2C总线功能2009-06-20 7192

全部0条评论

快来发表一下你的评论吧 !