I2C总线学习笔记

描述

I2C在小P以前接触的设计中大多只用到400k的速率,EVB的设计中更经常发现实现不了就降速到100k。现在突然再看看I2C,发现原来还有更高的速率规范,最高都已经到5M了。

于是乎,小P又要把这儿挖一挖看一看,反正I2C以后也经常会用到,不也得懂个所以然。

一、整体介绍

I2C最早是由Philips公司,现NXP公司开发的一种双向两线总线协议。其由于仅需要两个引脚即可实现双向多设备具有巨大的优势。截止至小P写这篇推文时候,规范的最新版本已经是《UM10204 v7》了。

在不同的应用架构中,I2C可用于SMBus(System Management Bus)、PMBus(Power Management Bus)、IPMI(Intelligent Platform Management Interface)、DDC(Display Data Channel)和ATCA(Advanced Telecom Computing Architecture)。I2C往后的进一步演进MIPI I3C总线是可以向下兼容I2C(I3C全名叫Improved Inter-Integrated Circuit,强译那就是改良型I2C),I3C可以提供更高的速率和更低的功耗。MIPI I3C总线在后续如果有涉及到的时候,再展开进一步学习了。

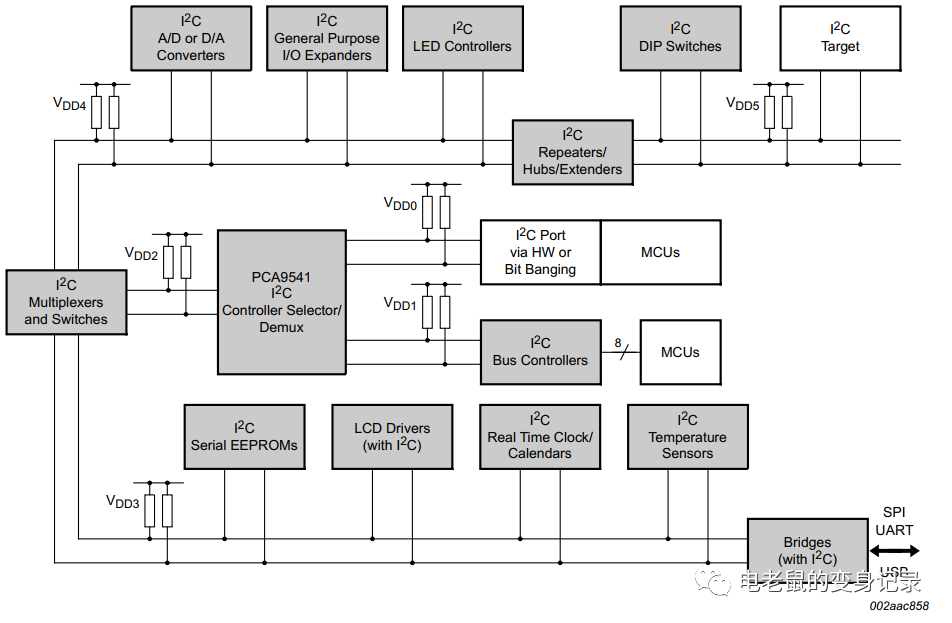

下图是个典型的I2C总线应用场景。

I2C总线有且仅有两个网络走线,串行数据线SDA和串行时钟线SCL。所有的I2C设备均是通过这两根走线进行互连通信,每个设备均以唯一的地址被识别。大多数I2C设备可以既作为发送端也可作为接收端,个别I2C设备如LCD驱动器等不需要发送数据的设备,可以只用作接收端。

由于I2C总线需要“线与”逻辑用于判断总线占用情况,因此SDA和SCL的接口必须使用外接上拉的OD驱动设计。

在只有单个I2C controller的应用场景中,如果SCL时钟线上没有会Stretch Clock的设备,那么controller的SCL输出可以使用推挽(Push-pull)电路。

PS.在V7的规范里,I2C原来master/slave的描述更新为controller/target,和MIPI I3C规范保持一致。

二、总线速率

I2C总线按速率分为以下的模式:

| 模式 | 速率 | 方向 |

|---|---|---|

| Standard-mode(Sm) | 100kbit/s | 双向 |

| Fast-mode(Fm) | 400kbit/s | 双向 |

| Fast-mode Plus(Fm+) | 1Mbit/s | 双向 |

| High-speed mode(Hs-mode) | 3.4Mbit/s | 双向 |

| Ultra Fast-mode(UFm) | 5Mbit/s | 单向 |

可以发现,3.4Mbps以下的速率,I2C总线的传输都是双向的,但是在UFm模式下变成单向传输。这种情况可以应用在控制器发送数据给LCD屏幕驱动,不需要回传数据的场景。

除了UFm模式以外,其他的模式均是和更低速率模式兼容的。

1、Fast-mode/ Standard-mode

(1)SDA和SCL的时序是适配的;

(2)SDA和SCL的INPUT为了消除毛刺,集成了施密特触发器(Schmitt trigger);

(3)SDA和SCL的OUTPUT包含下降沿的斜率控制。(其实就是OD门只可通过配置调整下管的驱动能力)

2、Fast-mode Plus

(1)总线拓扑与F/S-mode保持一致,速率向下兼容;

(2)Fm+设备可提供比F/S-mode更大的驱动电流,从而实现更长/更重负载的链路。

(3)当总线上仅有Fm+设备时,更强的驱动能力和更大的上升/下降容忍度,使得可以通过降速实现更重负载电容链路应用。最小的LOW和HIGH电平时间需要满足Fm+要求,上升时间不超过1us和下降时间不超过300ns。通过权衡总线速度和负载电容,可以提升最大负载电容的承受能力约10倍。

3、High-speed mode

(1)总线拓扑与F/S-mode、Fm+保持一致,速率向下兼容;

(2)为了实现3.4MBbps的通信速率,SCLH的OUTPUT使用了OD下拉+电流源上拉的组合电路,SDAH与其他保持一致;仅在Hs-mode模式下,仅有一个controller的电流源上拉会被使用;

(3)在Hs-mode的多控制器系统中,仲裁和时钟同步不会使用,这能加速位处理的能力;

(4)Hs-mode controller发出的SCL波形高低电平时间比是1:2,进而减轻了建立/保持的要求;

(5)Hs-mode controller可以在内部集成一个bridge。在Hs-mode传输时将F/S-mode设备的SDA、SCL和Hs-mode设备的SDAH(high-speed serial data)、SCLH(high-speed serial clock)断开。通过这种方式可以减小SDAH和SCLH总线上的负载电容,从而提高上升时间和下降时间;这个在下面的图示可以非常直观清晰的看到;

(6)SDAH和SCLH的INPUT集成了施密特触发器;

(7)SDAH和SCLH的OUTPUT包含下降沿的斜率控制。

当总线电容>100pF时,Rp可以被替换为外部电流源上拉,从而提高上升时间满足要求。

Rs电阻作为可选项,用于保护IO接口不被过高毛刺打坏,并且可以优化过冲震荡。

4、Ultra Fast-mode

针对UFm,不过多展开学习了。需要注意的是,UFm模式下的I2C,USDA和USCL均是采用的Push-pull输出,最高可达到5Mbps。

三、BIT/BYTE

接下来我们着重看下I2C的一些细节点,

首先就是I2C信号的采样方式。I2C的数据有效性要求SDA数据线在SCL时钟线高电平必须是稳定的(也就是在SCL高电平采样,不是边沿采样),SDA数据线的电平翻转仅允许在SCL时钟线低电平时,如下图。

然后就是I2C总线的数据传输的开始和结束特征,这个很简单。就是在SCL时钟线高电平时,SDA数据线下降表示开始,SDA数据线上升表示结束,如下图。S condition和P condition仅由控制器(也就是原master)发出,当S condition发出后,总线则被占用。在P condition发出一定时间间隔后,总线会被认为释放。

再接着是I2C的byte格式,这里有很有趣的几个点,这个就是OD门“线与”逻辑的有趣应用了。详细的图示可以看底下的图:

1、SDA数据线上的byte必须是8位长,并且开头一定是一个MSB(Most Significant Bit,这可不是你们以为哔哔)。当transmitter发送完一个8位的byte后,会将SDA数据线释放到高电平。然后receiver完整接收到这个8位byte后,将会在下一个(第9个)时钟周期高电平来之前,将SDA数据线拉低到低电平(ACK信号)。通过这个方式告诉transmitter我接收到数据了。如果没有成功接收到数据,或是数据不识别,那么在第9个时钟周期高电平时,receiver需要释放SDA数据线为高电平(NACK)。Controller若接收到NACK,则可以发出STOP condition结束数据传输或repeated START condition进行新的数据传输。

2、当target设备正在忙,没空接收数据时,target可以将SCL时钟线拉低,也就是我们说的hold住SCL。这种情况下,controller会进入等待模式。当target忙完了,就可以释放SCL时钟线,然后才会进行下一个byte的数据发送和接收。

I2C的数据传输是基于地址的,所以完整的一个I2C数据传输是包含7个地址位,1个读写位,再接着数据位和ACK位,如下图。在S(START condition)后面紧接着的就是7位Addr和1位RW。

值得注意的是,由于Hs-mode下的SCLH的高低电平周期是1:2,所以Hs-mode的传输和F/S- mode有些许差异,下图可以体现。

其实在学习I2C的时候,会有一个很容易迷惑的点,就是controller和target的关系,还有就是transmitter和receiver的关系。规范中对于这些的定义是如下

如果还是梳理不清楚,那么接下来的这段讲解,应该可以进一步帮助理解

1、Controller-transmitter发送数据给targer-receiver。数据传输的方向不需要变化,target-receiver在接收到每个byte时需要反馈ACK。

2、Controller读取target的数据,先由controller-tranmitter发送地址和读位,当target-receiver反馈ACK后,随即调整方向。controller-tranmitter变为controller-receiver,target-receiver变为target-tranmitter。第一个ACK信号由target在接收到地址后产生,后续的ACK均由controller产生。STOP condition(P)是在controller发出一个not-acknowledge(NACK)后,由controller发出STOP condition(P)。

3、还有一种混合格式(Combined format),在一次传输过程中,地址没有变化,仅是传输方向有变化。那么只需要重发一次repeated START condition(Sr)和同样的target地址,但是读写位翻转。在controller-receiver发送repeated START condition前,会发送NACK。

为了支持更多的设备可以同时挂在I2C总线上,7-bit地址扩展到了10-bit地址。7-bit/10-bit设备可以同时挂在一个I2C总线上。他们的区别就是,10-bit地址需要占用两个byte才能完成地址的传输。

第一个byte规定为1111 0XXR/W

第二个byte则定为XXXX XXXX

这10个X组成了10-bit地址,R/W决定了读写方向。

写方向与7-bit地址的模式类似,在完成两个地址byte发送后,发送8位数据。

读方向则和7-bit地址的Combined format有点类似,在完成两个地址byte发送后,通过repeated START condition(Sr),再发送一次一个byte地址后(读写位需要配置为1 Read),开始反向读取数据。这个时候不需要发第二个byte的地址,因为匹配的target设备会记忆其被定位。若读写位配置为0 Write,则需要继续发送第二个byte的地址去进行配对。

Hs-mode和F/S-mode的传输格式也有少许区别

四、电气约束和时序约束(疯狂的贴图时间)

1、S-/F-/Fm+设备约束

设备需要满足其最高速率,但是通过时钟同步,stretch SCL的低电平的方式,可以实现降速。

2、Hs-mode设备约束

一般意义上的START condition(S)在HS-mode中不存在,而是以repeated START condition(Sr)开头。地址位、读写位、ACK位及数据位的时序都是一样的,但是第一个SCLH的上升时间很特殊地放宽了。由于ACK后的第一个SCLH,上升沿是靠外部上拉电阻提供的驱动能力(第一个SCLH的时候,内部上拉电流源未开通工作)。

通过内部依次产生的100ns高电平和200ns低电平,Hs-mode controller满足外部3.4MHz的时序要求(包含上升/下降时间)。因此,Hs-mode controller可以采用10MHz基频或倍频来产生SCLH信号。

对于Hs-mode来说,时序要求也与总线上负载电容相关。当总线负载电容小于100pF时,总线可能可以运行在最高3.4Mbps速率下。当负载电容持续增大时,比特率会开始逐步降低。当总线负载电容等于400pF时,则能达到的最高速率应该是1.7Mbps。总线负载电容在100-400pF之间的,则时序参数需要线性的插值。

SDAH和SCLH的上升/下降时间与其在传输线上的最大传播时间一致,以防止末端开路反射。

I2C的链路时序计算一般风险较低。按照3.4MHz计算,一个周期大概是300ns。假定PCB的板材是FR4,DK 4.5,这样换算下来那么1ns大概是5.57inch走线的时延。且SDA的电平翻转动作是在SCLH低电平期间,也就是200ns这段,可以等效约1000多inch,已经远远超出可能的应用场景了。

这般梳理下来,小P觉得I2C的基本应用,配合做SI分析已经是足够了。如果说后面遇到需要进一步学习的时候,再补充了。

-

i2c总线ppt(I2C总线器件应用)2008-08-13 1359

-

I2C总线器件的C51读写程序2009-03-25 1037

-

i2c总线的特点2009-08-05 2649

-

I2C总线规范与I2C器件C51读写程序2009-08-22 1092

-

什么是i2c总线2007-11-05 4105

-

并口模拟I2C总线的设计2008-09-11 4652

-

基于CPLD的I2C总线接口设计2011-02-12 1400

-

基于51的I2c总线2016-01-13 1639

-

i2c2016-05-17 1060

-

基于I2C接口隔离的应用笔记2017-09-21 1033

-

I2C通信协议应该如何学习2020-04-28 2018

-

i2c总线用来做什么_i2c总线数据传输过程2020-11-24 9073

-

I2C总线的基本通信总结2021-08-26 20286

-

ESP32 之 ESP-IDF 教学(六)——I2C数据总线(I²C)2021-12-28 1964

-

I2C串行总线协议是什么?I2C总线有哪些优点?2023-09-12 3256

全部0条评论

快来发表一下你的评论吧 !