pcb板晶体不起振的原因分析

PCB设计

描述

照例,先抛出来一道面试题:“PCB板上的晶体不起振,可能是什么原因?”。这个问题比较常规,笔试题中标的概率比较高,实际使用时也可能会碰到这类问题。如何回答,10秒时间自己先思考下。

(-R) 是什么?

要回答这个问题,我觉得有必要先搞清楚什么是晶体的负性阻抗。

负性阻抗,英文:Negative Resistance;简写:-R;单位:Ω。在网上搜了下,找到如下描述。

负性阻抗是指从石英晶体共振子的二个端子往振荡线路看过去,所得到振荡线路在振荡频率时的阻抗特性值。-- 源自网络

还有一种解释,是从Murata网站看到的。

负性阻抗是指用阻抗表示的振荡电路的信号放大能力。--村 田

这两个定义,看起来都比较偏学术,不太通俗。我个人倾向于Murata的解释。大家知道大概意思就行了,不必纠结,重点是下面的内容。

(-R) 能做什么?

上面的定义,你可以不理解不清楚,但是下面这个你必须搞清楚弄明白。

敲黑板,这才是重点!!!

负性阻抗(-R)用于表征振荡裕量,即从振荡到振荡停止的裕量。

负性阻抗(-R)不是晶体的内部参数, 而是PCB电路的实测值,是晶体在PCB线路设计时的一个重要参数,可用于判断晶体振荡电路的稳定性。

如果在PCB上测出来的负性阻抗偏小,则表示该晶体振荡器的线路设计起振裕量不足,设计不合理。

(-R) 测量方法及步骤

说完负性阻抗(-R)的作用,再说下它的测量方法。

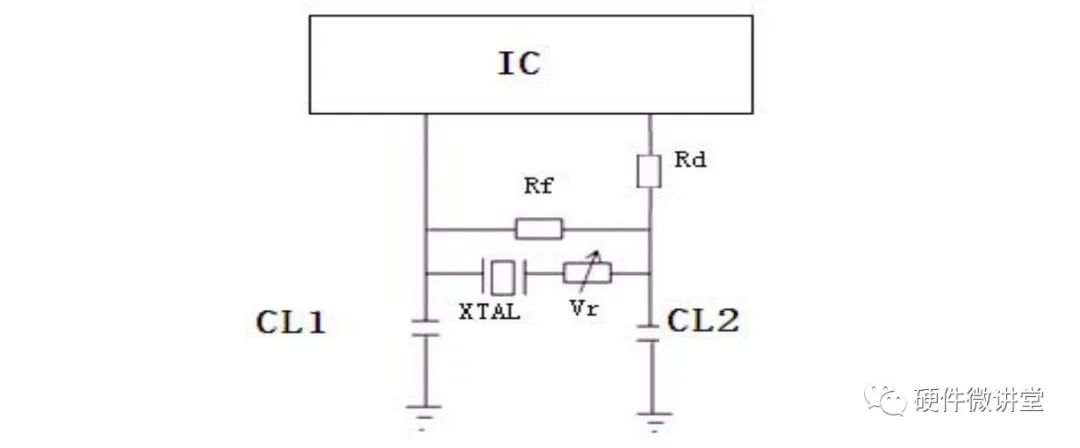

上图为负性阻抗测试的示意图。图中,Xtal是晶体,Rf是负反馈电阻,Rd是限流电阻,CL1/CL2是外部匹配电容,Vr是可调电阻。

负性阻抗|-R|的测试步骤:

①将可调电阻Vr与晶体串联接入回路,如上图。正常情况下,晶体振荡电路是不需要Vr的。Vr是我们为了测试|-R|,刻意添加进去的。

②调节可变电阻Vr,使回路起振或停振。当回路刚停振时,测试Vr的阻值;

③通过公式|-R|=RL+Vr,计算得到负性阻抗值。

特别说明:RL是晶体加负载电容的谐振阻抗,不是ESR。网上看有些文章,直接写|-R|=ESR+Vr,这是不对的,不要被误导。

(-R) 阻值定量分析

根据上面的测量,此时已经得出负性阻抗(-R)的阻值。

既然负性阻抗(-R)偏小表示晶体起振裕量不足,那(-R)阻值多少才算是一个合理值呢?

现在我们从定性分析已经进阶到定量分析,继续往下看。

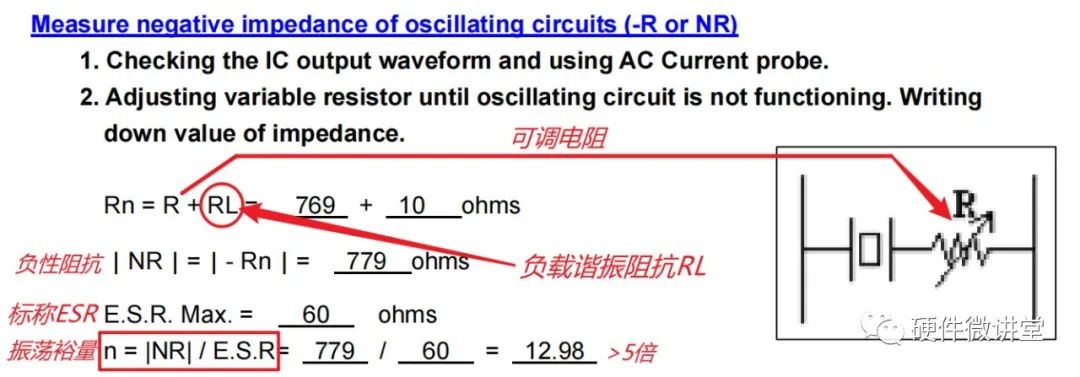

至少是规格书标称ESR的5倍,才合适!阻值越大,振荡裕量越高,说明振荡越稳定。

实际案例

上面讲的一大堆,都是理论知识。如果仅仅这样就结束本篇文章,那太不符合硬件微讲堂贴近实战的秉性,更体现不出来专业性。

上图是某品牌的晶体匹配测试报告中负性阻抗(-R)和振荡裕量计算部分。

可以看出:可调电阻R实测值为769Ω,RL为10Ω,则负性阻抗|-R|=779Ω。而该晶体标称的ESR(max)=60Ω,则振荡裕量(倍率)=|-R|/ESR=12.98倍,大于要求的5倍,满足起振要求。

晶体不起振的原因…

再回到文章开头提到的面试题“PCB板上的晶体不起振,可能是什么原因?”,负性阻抗偏小,振荡裕量不够,就是一个可能性比较大的原因。但这并不是唯一的原因,还有其他原因么?

当然有,其他原因有哪些,欢迎你在留言区补充。

晶体不起振,如何调整?

这也是一个不错的问题,我说2种方法:

方法①:减小外部匹配电容CL1/CL2,以增大负性阻抗;

方法②:更换标称值ESR更小的晶体,以增大振荡裕量;

编辑:黄飞

-

晶振没坏但不起振 PCB板上的晶体不起振为啥?2023-07-19 1259

-

晶振不起振的原因2012-06-10 31662

-

单片机晶振不起振的原因分享!2019-09-25 2796

-

单片机晶振不起振的原因有哪些2021-11-25 2320

-

晶振起振_单片机晶振不起振原因及解决方法2018-01-12 10891

-

基于stm32的8m晶振不起振的原因解析2018-01-26 32240

-

32768晶振不起振原因及解决办法2018-03-02 14903

-

单片机晶振不起振的40个原因分析2018-10-12 44401

-

单片机晶振不起振有哪些原因如何解决这个问题2018-12-31 9748

-

单片机晶振不起振具体原因分析与解决方案2019-09-27 8806

-

晶振不起振的原因有哪些2019-09-28 27405

-

引起单片机晶振不起振的原因有哪些呢?2023-10-13 3087

-

10个晶振不起振的原因分析2024-06-13 2525

全部0条评论

快来发表一下你的评论吧 !