基于Xilinx FPGA的嵌入式系统设计

描述

点击上方蓝字关注我们

1 概述

1.1 FPGA的特点及其发展趋势

嵌入式系统是一个面向应用、技术密集、资金密集、高度分散、不可垄断的产业,随着各个领域应用需求的多样化,嵌入式设计技术和芯片技术也经历着一次又一次的革新。虽然ASIC的成本很低,但设计周期长、投入费用高、风险较大,而可编程逻辑器件(Programmable Logical Device)设计灵活、功能强大,尤其是高密度现场可编程逻辑器件(Field Programmable Gate Array)其设计性能已完全能够与ASIC媲美,而且由于FPGA的逐步普及,其性能价格比已足以与ASIC抗衡。因此,FPGA在嵌入式系统设计领域已占据着越来越重要的地位。

FPGA的基本结构由以下几个部分构成:

·可编程逻辑功能模块CLB(Configurable Logic Blocks)

·可编程输入输出模块IOB(Input/Output Blocks)

·可编程内部互连资源PI(Programmable Interconnection)

随着工艺的进步和应用系统需求,一般在FPGA中还包含以下可选资源:

·存储器资源(Block RAM和Select RAM)

·数字时钟管理单元(分频/倍频、数字延迟)

·I/O多电平标准兼容(Select I/O)

·算数运算单元(乘法器、加法器)

·特殊功能模块(MAC等硬IP核)

·微处理器(PPC405等硬处理器)

以FPGA为核心的PLD产品是近几年集成电路中发展得最快的产品。随着FPGA性能的高速发展和设计人员自身能力的提高,FPGA将进一步扩大可编程芯片的领地,将复杂专用芯片挤向高端和超复杂应用。目前FPGA的发展趋势主要体现在以下几个方面:

·向更高密度、更大容量的千万门系统级方向迈进

·向低成本、低电压、微功耗、微封装和绿色化发展

·IP资源复用理念将得到普遍认同并成为主要设计方式

·MCU、DSP、MPU等嵌入式处理器IP将成为FPGA应用的核心

随着处理器以IP的形式嵌入到FPGA中,ASIC和FPGA之间的界限将越来越模糊,未来的某些电路版上可能只有这两部分电路:模拟部分(包括电源)和一块FPGA芯片,最多还有一些大容量的存储器。Xilinx等公司最新一代FPGA:Spartan II/E、Virtex II Pro及其相关IP Core的推出,使我们有理由相信,可编程片上系统(System on Programmable Chip)的时代已经离我们不远了。

1.2可编程片上系统(SOPC)的基本特征

可编程片上系统(SOPC)是一种特殊的嵌入式系统:首先它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

SOPC结合了SOC和FPGA各自的优点,一般具备以下基本特征:

·至少包含一个嵌入式处理器内核

·具有小容量片内高速RAM资源

·丰富的IP Core资源可供选择

·足够的片上可编程逻辑资源

·处理器调试接口和FPGA编程接口

·可能包含部分可编程模拟电路

·单芯片、低功耗、微封装

SOPC设计技术实际上涵盖了嵌入式系统设计技术的全部内容,除了以处理器和实时多任务操作系统(RTOS)为中心的软件设计技术、以PCB和信号完整性分析为基础的高速电路设计技术以外,SOPC还涉及目前以引起普遍关注的软硬件协同设计技术。由于SOPC的主要逻辑设计是在可编程逻辑器件内部进行,而BGA封装已被广泛应用在微封装领域中,传统的调试设备,如:逻辑分析仪和数字示波器,已很难进行直接测试分析,因此,必将对以仿真技术为基础的软硬件协同设计技术提出更高的要求。同时,新的调试技术也已不断涌现出来,如Xilinx公司的片内逻辑分析仪Chip Scope ILA就是一种价廉物美的片内实时调试工具。

2 IP资源复用理念与IP Core设计

2.1 IP资源复用理念

由于芯片设计的复杂性和产品面市时间对于保证终端市场的成功率至关重要,设计师不断寻求缩短设计周期的方法,以及更有效的设计方式。随着我们步入系统级芯片时代,利用IP内核和可编程逻辑进行设计复用显得日趋重要。

IP资源复用(IP Reuse)是指在集成电路设计过程中,通过继承、共享或购买所需的智力产权内核,然后再利用EDA工具进行设计、综合和验证,从而加速流片设计过程,降低开发风险。IP Reuse已逐渐成为现代集成电路设计的重要手段,在日新月异的各种应用需求面前,超大规模集成电路设计时代正步入一个IP整合的时代。

IP Reuse不仅仅应用于专用集成电路设计,对基于FPGA的嵌入式系统设计领域而言,更是具有举足轻重的地位。FPGA在采用IP内核方面走在了市场的前面,其原因有以下几个方面:

·FPGA具有极高的灵活性和面市时间短的特点,这使得多项设计迭代可以在数小时而不是数周内完成

·由于FPGA密度达到了百万门甚至是千万门,越来越多的设计师倾向于使用IP内核保持和提高产品的产量

·可编程逻辑价格低廉,可以作为切实可行的生产工具以及最佳原型设计,而且不许要昂贵的EDA设计工具,大大降低了设计门槛

2.2 IP Core设计方法:编码风格与项目模板

IP Core是IP Reuse的载体和核心内容,基于应用需求、规范协议和行业标准的不同,IP Core的内容也是千差万别的。但是,为了使IP Core易于访问和易于集成,其设计必须遵循一定的规范和准则。

在IP Core的开发方面,许多开放性的团体都付出了巨大的努力来推动各种IP Core的开发和IP Reuse理念的推广,其中比较著名的是Open Cores开发组织(http://www.opencores.org)。他们不仅开发了许多开放源代码的IP Core,涵盖了处理器IP、处理器外设控制器IP、算术运算单元IP、DSP算法IP等方面,而且编写了详细的IP Core编码风格和项目模板,并倡导了一种总线标准wishbone,用于规范各种IP Core的接口标准。国内开放性团体IP Core开发小组(http://www.IPcore.com.cn)也在IP Core开发和IP Reuse理念的推广和普及方面进行了不懈的努力。

编码风格(Coding Style)是基于HDL的IP Core源码编写的指导性文档,其可读性直接关系到IP Core的易于访问和易于集成性。编码风格一般包含几个方面的约定:文件头和版本说明、联机注释、命名规则、可综合编码等。

项目模板则规定了完成一个IP Core设计包含的主要内容及所需提供的文档,项目模板内容及其文档直接关系到IP Core的易于集成特性,一个IP Core必须是完整的、经过全面验证的,才能顺利地集成到应用项目中去。项目模板一般包含几个方面的内容:项目定义、接口说明、系统结构和模块、设计文档说明、测试验证报告、约束和实现、版本说明、试用评价以及参考文献等。

编码风格和项目模板详细文档的英文版和中文版可分别从上述两个网站获得。

2.3 IP Core验证:仿真、测试与评估板

IP Core设计在完成编码阶段以后,对其功能的测试验证是一项非常重要的内容,因为这直接关系到IP Core资源的可用性。仅仅通过功能仿真、时序仿真和测试向量验证的IP Core是不完备的,它必须通过实际系统的验证。国际上各大公司通常采用的办法是评估板验证,也即构建一个与实际系统IP Core应用一致的硬件环境,通过下载FPGA配置使其具备相应的逻辑功能,并进行实物仿真。

另外,由于IP Core的许可成本较高,用户也通常希望在购买IP Core之前,对其功能进行充分的验证以确定是否适合于目标系统,从而降低投资风险,(当然,内核和源代码的知识产权是加了保护措施的),Xilinx公司的Sing Once和Altera公司的Open Core均提供了这样的平台。

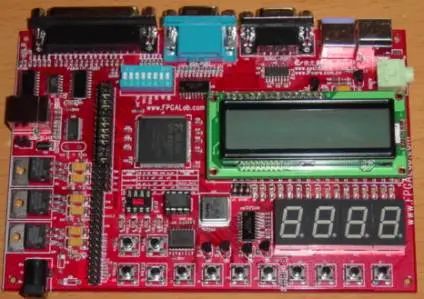

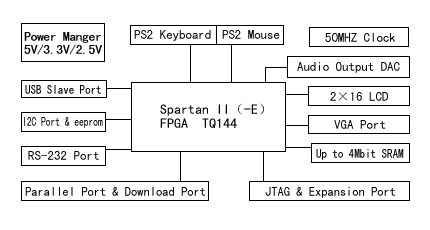

Xilinx公司和Altera公司均提供了许多用于评估IP Core的FPGA评估板,如USB、MAC、IEEE1394等等。许多第三方设计中心,如Insight,还开发了用于SOPC系统集成的Virtex II MicroBlaze评估板和Virtex II Pro PPC405评估板等等。Xilinx FPGA的国内专业设计公司长沙依元素科技(http://www.eestd.com)还开发了用于测评各类基本IP Core以及学习培训用途的数字刀剑?系列 (DigitalSword?Series Kit)评估板,如图1所示,该系列评估板提供了VGA、LCD、音频、键盘鼠标、串口、并口、USB Slave、I2C等电平接口,并提供了标准扩展总线以及丰富的子板功能模块支持。

图1(a) 数字刀剑 系列之火龙刀

图1(b) 数字刀剑?系列FPGA评估板结构框图

3 基于Xilinx FPGA的嵌入式系统设计

3.1 FPGA基本开发流程与开发工具

FPGA基本开发流程主要包括设计输入(Design Entry);设计仿真(Simulation);设计综合(Synthesize);布局布线(Place & Route);配置(Configuration)五个主要步骤。

设计输入主要有原理图输入和HDL输入两种方式,一般开发商都同时支持两种输入方式。有些熟悉硬件设计的工程师开始喜欢利用原理图进行设计,这种方法非常直观,但基于可移植性和规范化方面的考虑,绝大部分深入FPGA设计和ASIC设计的工程师最终都将统一到HDL平台上来。

设计仿真包含功能仿真和时序仿真两项主要内容,功能仿真忽略了综合和布局布线导致的时延等因素,仅仅从逻辑上进行仿真,这对设计思路的验证是有帮助的,但必须通过时序仿真作进一步验证,发现并修正时序问题。

设计综合将HDL语言生成用于布局布线的网表和相应的约束。综合效果直接导致设计的性能和逻辑门的利用效率,因此,许多可编程逻辑器件开发商都支持第三方综合和仿真工具,著名的有:Synplicity、Synopsys和ModelSim等。

布局布线工具利用综合生成的网表,在FPGA内部进行布局布线,并生成可用于配置的比特流文件。布局布线工具与可编程逻辑器件工艺及其布线资源密切相关,一般由可编程逻辑器件开发商直接提供。

随着可编程逻辑器件容量的不断增大和设计性能要求的不断提高,对传统的FPGA开发工具提出了挑战。以Xilinx公司为例,应IP Core开发和集成的需要,开发了IP Core使用工具Core Generator和IP Core包装工具IP Capture;提供了模块化设计工具Modular Design用于超大规模设计的团队项目开发;用片内逻辑分析仪ChipScope ILA进行片内逻辑调试;Xpower则用于设计功耗分析并得出相应的解决方案;还有System Generator结合Simulink甚至可以简单地实现数字信号处理模型(如FIR滤波器和FFT等)的FPGA硬件实现。此外,一些有争议的设计工具,如基于C语言的FPGA开发工具DK1等为超大容量FPGA设计和复杂逻辑设计提供了值得尝试的途径。

3.2 处理器IP Core:Micro Blaze与PPC405

将处理器IP Core嵌入到可编程逻辑器件是基于FPGA的嵌入式系统设计的前提条件,目前,国内外许多单位已成功的将51单片机、ARM和PPC等处理器内核嵌入各种可编程逻辑器件并进行了应用系统的设计,其中最著名的要数Xilinx公司的Micro Blaze和Altera公司的Nois了。Xilinx从Pico Blaze到Micro Blaze,再到PPC405,完成了从8位单片机到32位微处理器的逐步完善和性能提升。

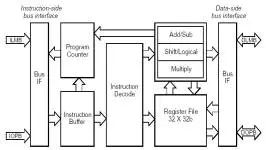

Micro Blaze 是一个专门为Xilinx FPGA优化的RISC嵌入式软处理器,符合IBM Core Connect标准,能够与PPC405系统无缝连接,Micro Blaze软处理器内核的结构如图2所示,

图2 Micro Blaze IP Core结构框图

它具备以下基本特征:

·32个32bit通用寄存器

·硬件乘法器(仅限Virtex II系列)

·32bit地址总线和32bit数据总线

·三操作数32bit指令字,两种寻址模式

·独立的片内程序32bit总线和数据总线

·片内总线遵循OPB(On-chip Peripheral Bus)标准

·通过LMB(Local Memory Bus)访问片内Block RAM

Micro Blaze是一个非常简化,但有具有较高性能的软处理器内核,他可以在性价比很高的Spartan II(-E)系列FPGA上实现,系统时钟频率为75MHZ,仅占用400个Slice资源,相当于10万门FPGA容量的三分之一,而10万门的Spartan II系列FPGA的批量目标市场价格仅为10美元左右,非常适合消费类嵌入式产品应用需求。

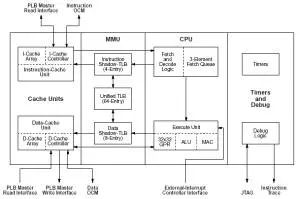

在Xilinx最新一代FPGA Virtex II Pro中,嵌入了IBM公司的PPC405 RISC结构硬处理器(如图3所示),

图3 PPC405 IP Core结构框图

该处理器内核具备以下基本特征:

·32位、Harvard结构,300MHZ以上工作频率

·支持IBM Core Connect总线标准

·符合PowerPC UISA标准

·低功耗:0.9mW/MHZ

·硬件乘法和除法单元

·32个32bit通用寄存器

·16KB双端口程序缓存

·16KB双端口数据缓存

·内存管理单元(MMU)支持

·独立的调试和跟踪接口

PPC405硬处理器内核性能上与现有的EPPC Core完全一致,含有PPC405 Core 的Virtex II Pro系列FPGA还附加了Gbit收发器和18×18硬件乘法器以及庞大的可编程逻辑资源,非常适合于通信、图像信号处理以及复杂应用系统的设计,并提供了更加灵活的设计模式。

3.3 基于Micro Blaze和PPC405 Core的SOPC软硬件开发

基于嵌入式处理器内核的SOPC系统开发是一个软硬件协同设计的过程,一方面,它极大地提高了系统设计的灵活性和快速的设计迭代周期,使整个开发过程变得更加可控;另一方面,一些新的调试和设计问题,如逻辑分析仪和数字示波器的接入等,对调试设备和调试手段提出了更高的要求,为了尽可能避免问题的产生,要求有更好的设计工具和集成开发环境,保证IP Core资源的可用性和设计实现的一致性,让设计工程师从烦琐的内部时序调试中解放出来。

Xilinx提供了针对Micro Blaze Core应用系统开发的集成开发环境MDK,该开发环境包含了用于硬件描述和系统生成的Platform Generator、用于软件设计和编译的Micro Blaze IDE,GDB调试可通过FPGA配置JTAG接口进行,无需任何附加的调试硬件,配合Foundation ISE4.2和FPGA目标板即可进行全功能开发,MDK还包含了UART、GPIO、Watchdog、Timer/Counter、EMC和中断控制等基本处理器外设库,用户可以添加兼容OPB总线标准的任意IP Core。Insight和依元素科技均提供了功能全面的Micro Blaze Core评估工具。

PPC405 Core是一个高性能的处理器内核,它具有独立于FPGA JTAG的调试端口和更加复杂的调试功能,我们甚至可以将基于PPC405 Core的SOPC调试直观地理解为基于IBM PPC405处理器和大容量FPGA的单板机调试,只不过这个单板机无需进行传统的PCB设计和调试,设计迭代过程全部在计算机上进行。PPC405 Core的软件集成开发环境支持传统的IBM PPC405开发环境,Xilinx提供了相应的系统集成开发环境和GNU软件开发工具包支持。第三方软件开发商Wind River和Montvisa已分别宣布其VxWorks和HardHat Linux实时操作系统(RTOS)及其集成开发环境支持Virtex II Pro 系列FPGA,Insight和Avnet已开始销售含有Virtex II Pro FPGA的高端评估板。依元素科技也推出了用于开发PowerPC系列处理器的GNU集成开发工具和利刃?系列调试工具,以及含有PowerPC处理器的原型评估板。

4 基于Internet可重配置逻辑(IRL)

4.1 IRL技术的基本特征与应用

Internet Reconfigurable Logic (IRL)是Xilinx倡导的一种新的FPGA设计理念,其核心是通过Internet对远程设备的硬件设计和软件程序进行升级、重构、调试和监控,这种设计理念伴随着嵌入式Internet技术的蓬勃发展必将对嵌入式设备的设计模式产生深远的影响。

IRL包括三个方面的基本要素:

·含有配置bit流或应用程序的主机

·含有配置功能的目标系统

·Internet或远程访问介质

在Internet环境下,可通过Web Browser访问远程目标机,通过HTTP、FTP协议、Java Applet和CGI等功能实现数据、文件传输和交互控制功能。在某些特殊环境下,远程访问介质可以是PSTN、无线网络或其它特殊媒介,这在某些工业控制场合以及军事应用中是常见的。

IRL技术可以应用于许多场合,诸如:在部分功能没有完成全面测试之前就可以先将产品投放市场;故障设备的远程维护;远程修复产品使用过程中发现的Bug;对已售出的产品升级新的功能;对新出现的标准和协议予以支持等等。总而言之,采用IRL技术将带给我们的产品三个明显的优势:缩短产品上市时间;减少产品维护费用;延长产品生命周期。

4.2 IRL技术的设计实现

在基于Web Browser的条件下,主机端的应用程序将达到最简化,主机端无需安装任何特殊应用程序就可完成对远程设备的操作,这种简化对用户而言是必要的。这样,目标机的设计就是IRL技术实现的全部内容。

一般而言,目标机端IRL模块应实现以下功能:

·以太网或Modem接入

·TCP/IP或TCP/IP+PPP协议栈

·Http Web Server

·支持CGI、ASP或Java Script

·FPGA配置时序,至少支持JTAG配置模式

·足够的存储空间和配置故障恢复功能

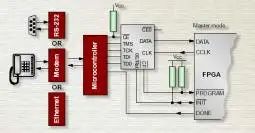

在嵌入式Internet技术和处理器的支持下,这些功能的实现已经不是技术上的瓶颈了,图4给出了依元素科技也开发的IRL评估模块原理框图,

图4 基于Rabbit2000的IRL模块原理框图

该这种实现方式是一种基于单片机或专用处理器的IRL实现方式。Avnet推出了基于PowerPC和PMC总线的高端IRL技术评估板。

在本文研究的SOPC设计技术的基础上,FPGA甚至能够通过内部嵌入式处理器内核(如Micro Blaze和PPC405)及其软件支持,实现对自身的重构和升级。

5 结束语

随着可编程逻辑器件工艺的不断进步和开发工具的不断增强,FPAG将更加广泛的应用在各个领域,FPGA的将在更广泛的范围普及,成本和价格将不再成为我们拒绝在设计中采用FPGA的理由。我们有理由相信,SOPC、IRL等设计理念将会对我们的设计方式产生新的变革,也必将给每一位嵌入式工程师带来有益的思路和更加宽广的创意空间。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:基于Xilinx FPGA的嵌入式系统设计

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- FPGA

-

嵌入式fpga是什么意思2024-03-15 3918

-

fpga是嵌入式吗2024-03-14 5787

-

FPGA实现嵌入式系统2021-07-30 1392

-

基于Xilinx FPGA的嵌入式系统该怎样去设计?2021-04-30 1285

-

FPGA是嵌入式系统设计的理想选择2018-07-30 2458

-

基于FPGA嵌入式系统的智能小车全面解析2018-06-05 10301

-

基于XILINX FPGA片上嵌入式系统的用户IP开发2017-12-08 5301

-

基于FPGA的嵌入式Linux操作系统解决方案2017-11-24 7142

-

基于Xilinx FPGA的嵌入式串行千兆以太网设计2017-11-23 4117

-

Xilinx FPGA上的嵌入式系统设计实例2017-10-31 3199

-

Xilinx FPGA 嵌入式系统程序引导和启动的流程2017-02-11 2900

-

基于Xilinx MicroBlaze的嵌入式I/O系统设计2011-05-14 1040

-

如何用FPGA实现嵌入式系统2009-04-02 8045

全部0条评论

快来发表一下你的评论吧 !