DSP教学实验箱:音频采集与播放实验

电子说

描述

一、实验目的

学习McASP管脚的使用方法,掌握音频采集播放的原理和过程,并实现音频的采集与播放。

二、实验原理

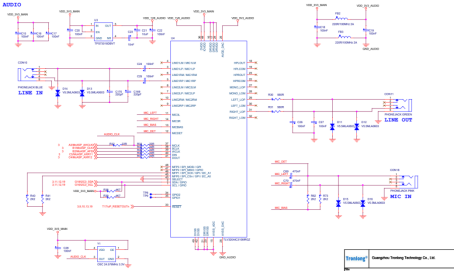

1、原理图

(1) 音频接口采用的是24.576MHz(读兆赫兹)晶振。

(2)实验板上共有3个音频端口,分别是LINE IN、MIC IN和LINE OUT。

(3)音频数据是通过I2C总线进行读写的。

(4)McASP(字母)的时钟来自于晶振时钟,分频后可得到帧同步信号和位同步信号。

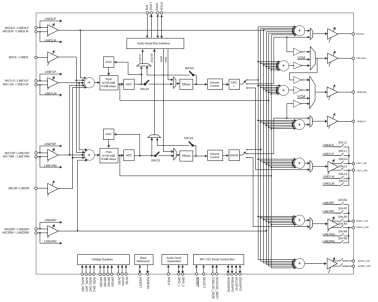

2、功能框图

(1)数据精度支持 16/20/24/32 bit 。

(2)支持速率 8kHz ~ 96kHz 。即采样率,定义了每秒从连续信号中提取并组成离散信号的采样个数,单位时间的点越多声音的信息也就越完善,当然也就更接近于真实。

(3)控制总线可选为 SPI 或 I2C。

(4)音频串行数据总线支持4种协议格式: I2S, 左对齐格式,右对齐格式,DSP格式。

(5)有可编程PLL 可以灵活产生时钟。

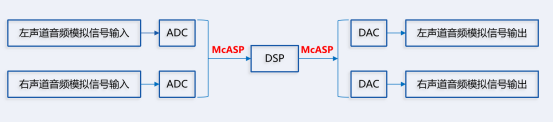

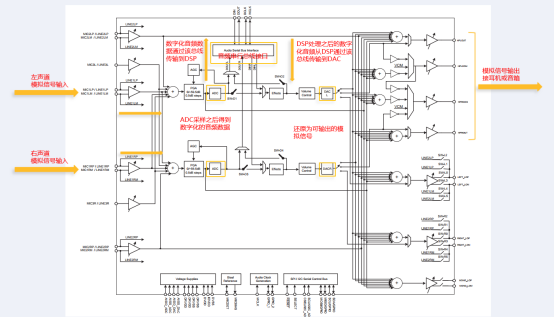

3、音频芯片功能框图

(1)在框图底部分别是供电部分、时钟产生部分、SPI或I2C串行总线控制部分。

(2)芯片通过左右声道采集输入的音频模拟信号。

(3)经过ADC采样后得到数字化的音频数据。

(4)数字化音频数据通过音频串行总线接口传输到DSP。

(5)DSP处理之后的数字化音频从DSP通过音频串行总线接口再传输到DAC。

(6)音频经过DAC还原为可输出的模拟信号。

(7)最后,通过耳机或者音箱输出音频模拟信号。

通过框图的讲解,我们可以总结出音频芯片的工作流程。音频模拟信号通过左右声道分别采样,经过ADC转换为数字信号后通过McASP传输到DSP,在DSP处理完成后再通过McASP传输到DAC,最后经过DAC转换为模拟信号后,分左右声道输出。

4、McASP(Multichannel Audio Serial Port) 通用音频串行端口

(1)McASP包括发送和接收部分,它们之间可以同步运行,也可以完全独立地使用各自的主时钟,位时钟和帧同步信号,并且可以使用具有不同位流格式的传输模式。

(2)McASP模块包括16个串行器,可以单独激活来进行发送或接收。另外, 所有的McASP引脚都可以被配置为通用输入输出(GPIO)引脚。

(3)McASP 传输模式 :突发传输模式 、时分复用TDM传输模式 和数字音频接口DIT传输模式。

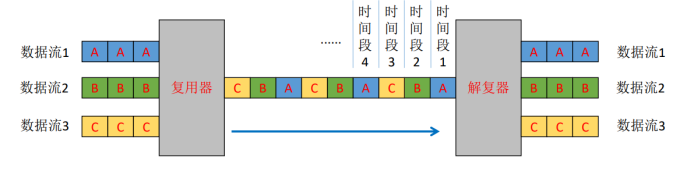

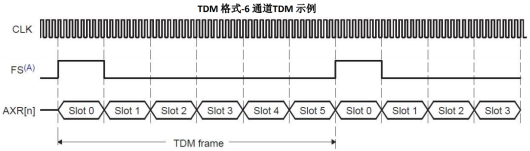

5、McASP传输模式--时分复用模式

TDM就是时分复用模式。时分复用是指一种通过不同信道或时隙中的交叉位脉冲,同时在同一个通信媒体上传输多个数字化数据、语音和视频信号等的技术。 使用这种技术,就允许两个以上的信号或者数据流在同一条通信线路上传输。每个信号 或数据流轮流占用物理通道。

(1) TDM 格式可以用于DSP芯片与一个或多个模-数转换器(ADC),数-模转换器(DAC)之间的数据传输。

(2) TDM格式包括三部分:时钟、数据和帧同步信号。

(3)一帧包括多个通道。每一个TDM帧是由帧同步信号来定义的(AFSX或AFSR)。

(4)数据传输是连续的,在单元之间没有延迟。

(5)系统中发送端和接收端每个单元的位数要一致,因为单元边界不是由帧同步信号决定的

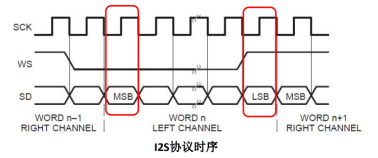

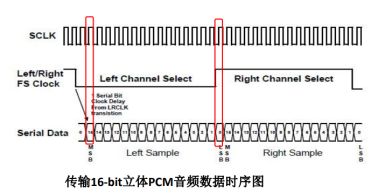

McASP 发送器和接收器支持多通道传输,通过TDM传输模式可以使用符合时分复用(TDM)格式的数据流。在这种传输模式下,兼容I2S协议的设备。I2S协议主要用于音频数据的传输。

数据的最高位与声道选择信号之间会有1个bit的延迟。一帧数据里包含两个数据单位,分别传输左声道和右声道的数据。

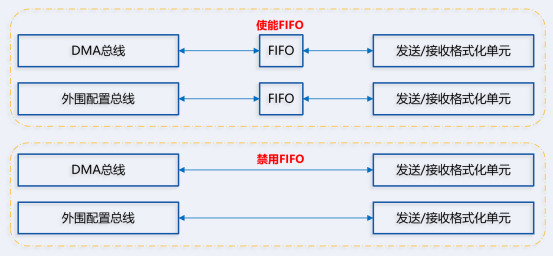

访问McASP的途径有两种,第一种是使能FIFO,第二种是禁用FIFO。两种途径都需要配置DMA总线和外配总线。

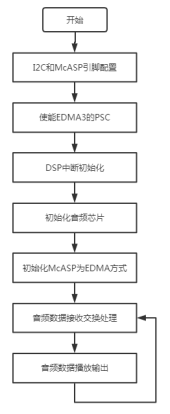

6、程序流程

程序流程设计中首先要进行I2C和McASP的管脚复用配置,接着使能EDMA3的PSC并初始化DSP中断,然后进行音频芯片的初始化,并将McASP初始化为EDMA方式。最后进行音频数据的接收交换处理并不断输出音频数据。

6、源码

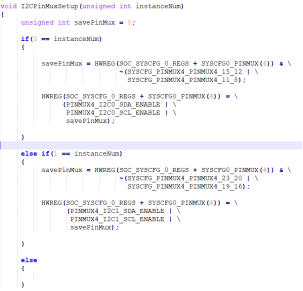

管脚复用源码

基于StarterWare控制外设时可调用对应的API接口,无需配置复杂的寄存器。I2C和McASP管脚复用配置的函数源码可以分别查看I2C.c和McASP.c。

DMA(Direct Memory Access)直接内存存取

(1)CPU把数据传送的源、目的、数据个数等信息交给DMA,让DMA控制数据传输,在此期间,CPU可以运行其他程序,等到DMA控制的数据传输完成,发送中断告诉CPU数据传输完成了,让CPU处理数据,因而提高了算法的速度。

(2)TI公司为TMS320C6748量身设计了增强版直接存储器访问控制器EDMA3。 EDMA3一共有32个通道,通道的优先级可选,可以实现数据传输的无缝链接,利用EDMA,可以实现片内存储器、片内外设以及外部存储器之间的数据传输。

(3)增强型内存直接访问控制器(EDMA3)是一种高性能,多通道,多线程 DMA 控制器,允许用户编程传输一维和多维大量数据 ,能够不依赖CPU 进行数据的搬移。

三、操作现象

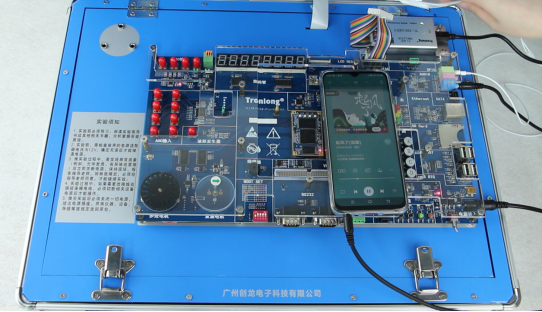

1、实验设备

本实验使用的硬件接口为LINE IN和LINE OUT接口,所需硬件为实验板、仿真器、电源、音频线、耳机和音乐播放器。本次操作是使用手机来播放音乐。

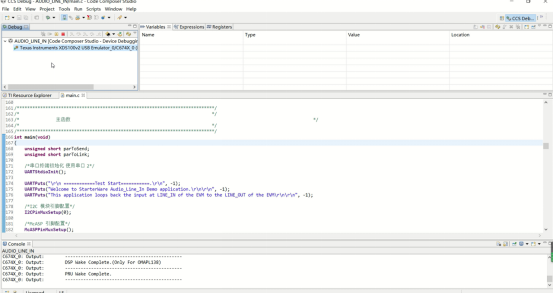

2、软件操作

导入工程,选择Demo文件夹下的对应工程

编译工程,生成可执行文件

将CCS连接开发板并加载程序

点击运行程序

通过耳机即可听到手机播放的音乐。

实验结束后,先点击黄色按钮暂停程序运行,再点击红色按钮退出CCS与实验板的连接,最后实验箱断电即可。

-

荆州学院联合创龙教仪建设DSP教学实验箱案例分享2024-09-12 13211

-

从理论到实践:DSP教学实验箱中的音频滤波实验案例精选2024-08-30 1367

-

双DSP C2000+C5000高性价比教学实验箱2024-04-26 1401

-

国产嵌入式DSP教学实验箱_操作教程:22-AD采集DA输出实验(采集输出正弦波)2024-03-06 5708

-

国产嵌入式教学实验箱_嵌入式教程_DSP教学实验箱:3-1 音频采集与播放实验2023-10-25 21530

-

嵌入式DSP教学实验箱_数字信号处理教程:3-5 AAC音频编码实验2023-09-05 1905

-

嵌入式教程_DSP教学实验箱:2-18 模数转换(AD)实验(采集波形)2023-08-21 22055

-

嵌入式教程_教学实验箱实验操作_音频处理:3-2 mp3音频编码实验2023-06-02 28408

-

DSP音频专用教学实验箱:TL5509-TEB规格书2023-05-29 702

-

ARM+DSP+FPGA高校教学实验箱:TL138F-TEB 创龙教仪2023-05-09 4918

-

可拆式DSP实验箱TL6748-TEB-A2015-11-04 3042

-

【UT4418申请】物联网教学实验箱2015-10-27 2727

-

光纤通信实验教学系统实验箱简介2010-10-25 773

-

EDA 教学实验箱的设计2009-12-05 935

全部0条评论

快来发表一下你的评论吧 !