各个元器件在EMC中的应用详解

EMC/EMI设计

描述

从这部分内容开始,我们着重分析各个元器件在EMC中的应用,通常包括电感,电容,磁珠,电阻和磁环。首当其充的是电容。

1.在EMC设计中,以上元器件特性都跟一个重要因素有关,频率,离开频率这个重要因素,谈电容,电感,磁珠等都是在“耍流氓”。

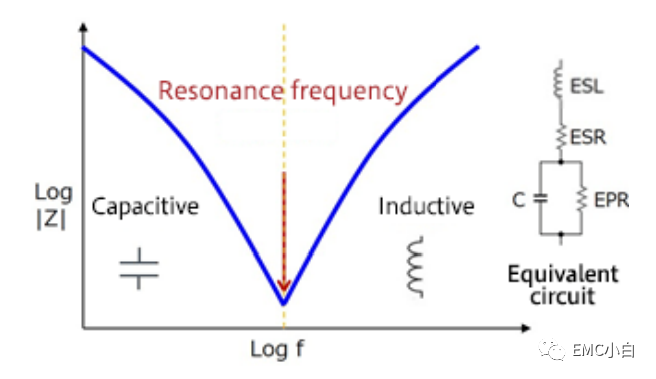

电容可以理解为寄生电感和电容的串联,当频率超过谐振频率时,容抗小于感抗,电路逐步呈现电感特性。谐振频率可通过以下公式计算。

f =1/(2π√C × ESL)

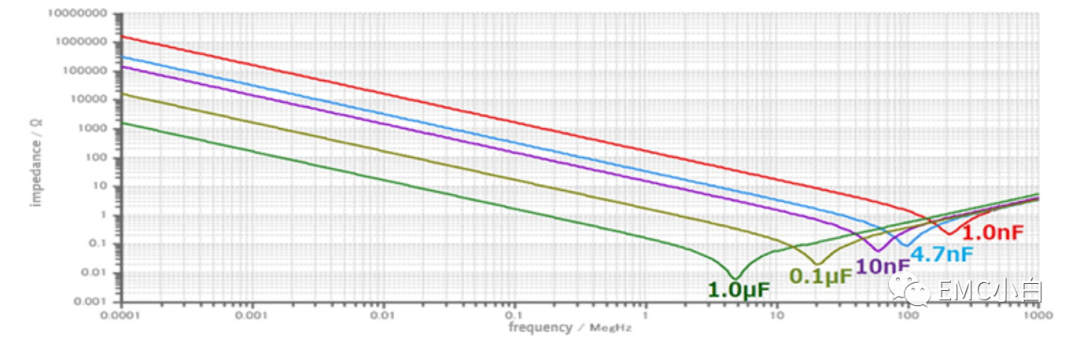

由于电容的阻抗特性,在选择电容进行EMC对策时,需要根据不同频率下的阻抗特性选择:

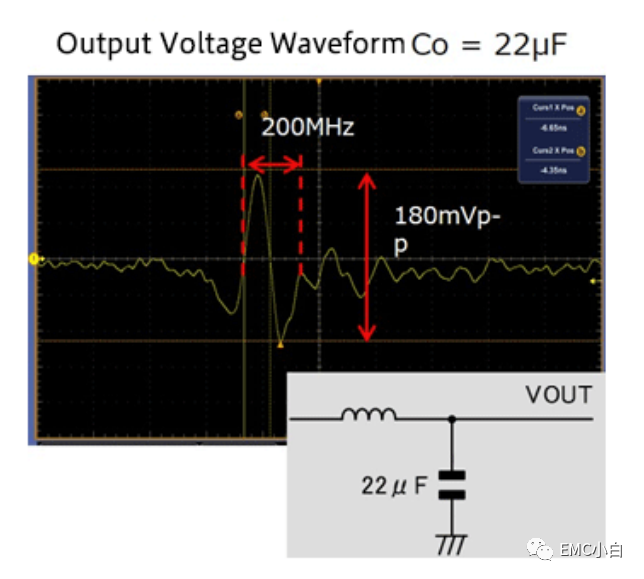

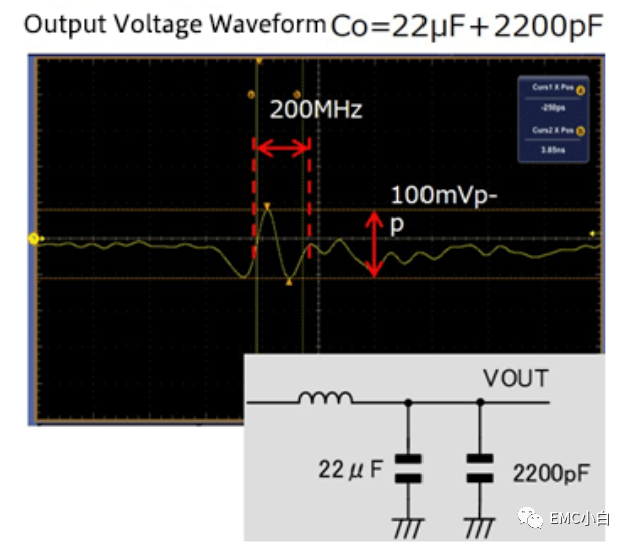

2.如果说电感主要通过降低di/dt,提升EMC性能的话,那么电容就是通过降低du/dt提升EMC的性能。下图是在DCDC电源中,通过在输出端增加电容降低噪声的幅值:

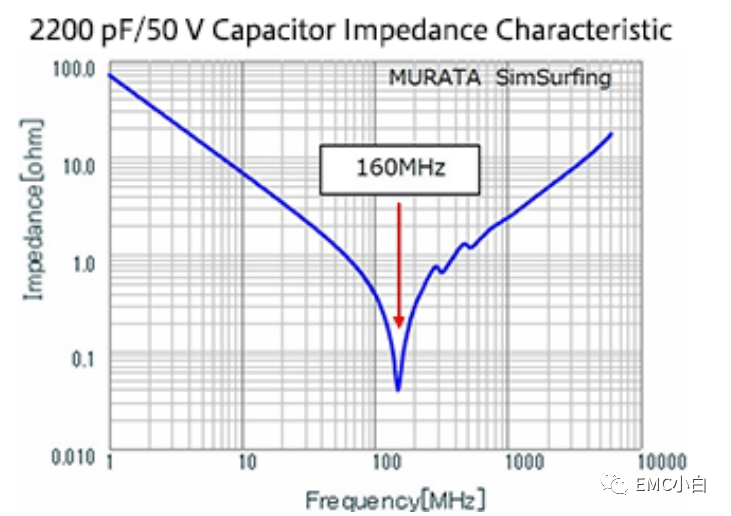

通常上图可以看出,当输出端增加一颗2200pf的电容时(2200pf电容的谐振频率在100MHz-200MHz之间),200MHz的峰峰值由180mv下降到100mv,通常前面EMC基础(二)的总结可知,由于容性耦合电压正比于jwUCR,当降低U时,可以降低容性耦合的影响。

这是通过增加电容降低目标噪声频率的阻抗,从而降低噪声幅值的方法,需要关注信号的频率,才能锁定选用什么容值的电容进行降噪处理,在这里,需要额外注意的是,不同厂家的电容特性也是不一样的,我们在选型时,需要特别注意翻看电容的阻抗特性曲线。

3.要想有效的使用去耦电容,除了根据不同频率选择合适的电容以外,还需要注意以下几点

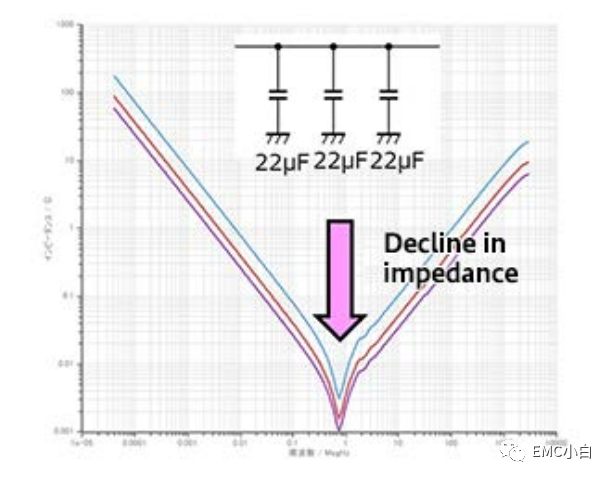

)多个相同容值的电容并联

当多个相同容值的电容并联时,可以将该频率的信号幅值降得更低

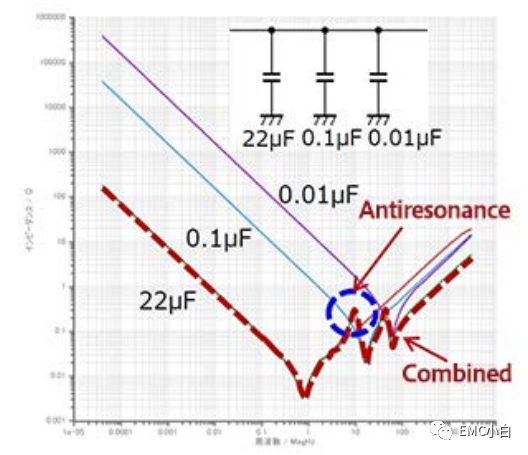

多个不同容值的电容并联

当需要对多个频率信号进行噪声处理时,就需要多个不同容值的电容并联,但这会带来新的问题,反谐振点:

从上图可以看出,由于22uf在超过谐振频率以后呈电感特性,跟0.1uf的电容形成了并联谐振,此时阻抗达到最高,这就说明所选择的电容,是根据目标降噪频率进行选型的。

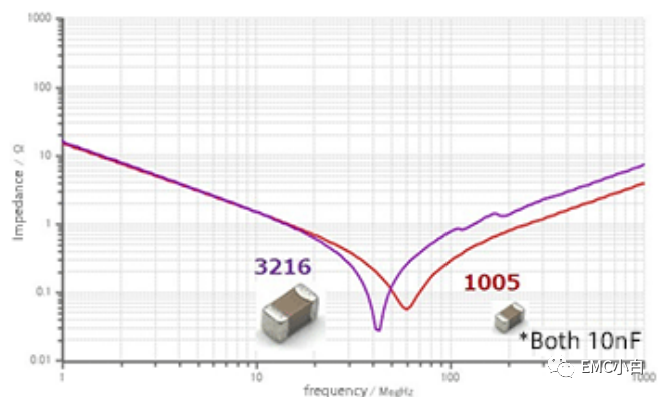

2.)降低寄生电感的影响

由于电容的选用,不仅仅针对其谐振频率点,也会应用其小于谐振频点的情况,这就要求电容的寄生电感越小越好,同样的情况下,封装越小,其ESL越小。

从上图可以看出,相同的容值下,3216的谐振频率点超前于1005的封装,这说明3216的寄生电感ESL更大。

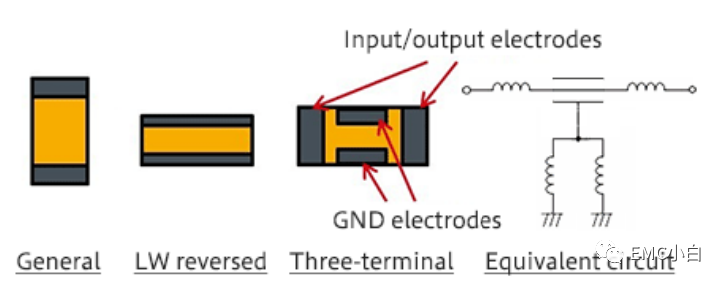

为了降低电容ESL的影响,村田和TDK等电容厂家也相继研发出了三端子电容,即ESL部分主要连接在串联电路上。

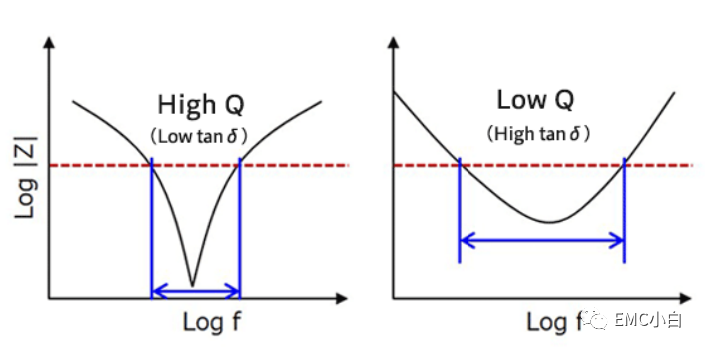

3.)Q值不同的电容

当Q值很高时,阻抗在特定的频率下,阻抗会很低,但是不在该频率范围时,阻抗上升的很厉害,而Q值相对较小的电容,在一定范围内都可以维持较低的阻抗,这样反而更加有利于EMC实验。

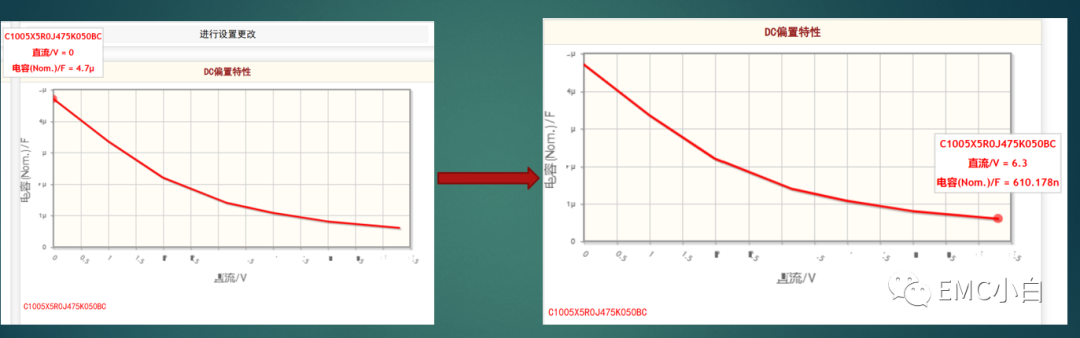

4.)不同温度,电压下的电容

陶瓷电容在高压和高温条件下,其电容容值会发生明显变化,这点我们需要特别注意,当电容容值发生变化了,其谐振频点也会发生变化,滤波的效果就达不到了。

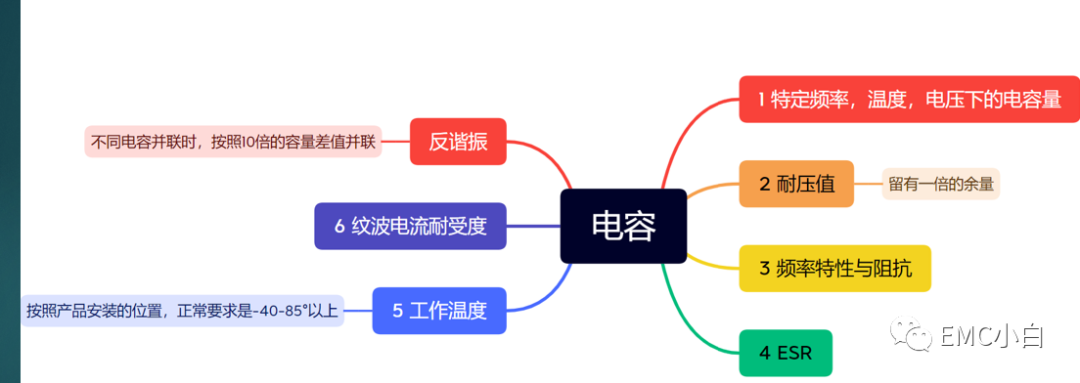

总结:电容选型时需要时刻关注以下几点:

备注:

后期准备录制EMC相关的视频,主要是从电容,电感,磁珠等元器件的选型开始,到EMC原理及相关实验介绍,再到EMC整改设计,最后介绍一些EMC整改实际案例,预计在8月下旬录制完成元器件选型部分,元器件选型的课件已经完成,加入EMC群的伙伴可以免费获取,欢迎大家多多支持,谢谢。

编辑:黄飞

-

电磁兼容(EMC)元器件的正确选型和应用技巧2011-11-23 4035

-

EMC设计元器件选择及电路设计很关键2018-04-15 10294

-

【必看】开关电源中每一个元器件的计算+51页图文详解2025-05-12 373

-

【招聘】EMC/元器件工程师-厦门-8.3更新2012-08-03 2782

-

钳位电路元器件功能详解2012-10-17 11636

-

Altium如何给复制的元器件组自动加后缀编号2019-10-10 6033

-

如何检测开关电源中的各个元器件?2021-03-10 1621

-

电子元器件基础知识详解2007-10-08 2141

-

EMC主要元器件工作原理与使用情况2012-08-09 4750

-

元器件在应用中的静电防护2017-10-17 1096

-

元器件各个安装孔间距详细图解2018-10-03 11169

-

不同元器件在EMC设计中的选择及应用技巧2019-05-17 2013

-

开关电源中的各个元器件是如何检验的?资料下载2021-03-29 957

-

EMC整改必用的元器件2022-11-08 2885

-

了解网络滤波器 EMI滤波器 EMC滤波器 在电子元器件中的分类关系2023-06-24 113672

全部0条评论

快来发表一下你的评论吧 !