Xilinx FPGA芯片内部时钟和复位信号使用方法

描述

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

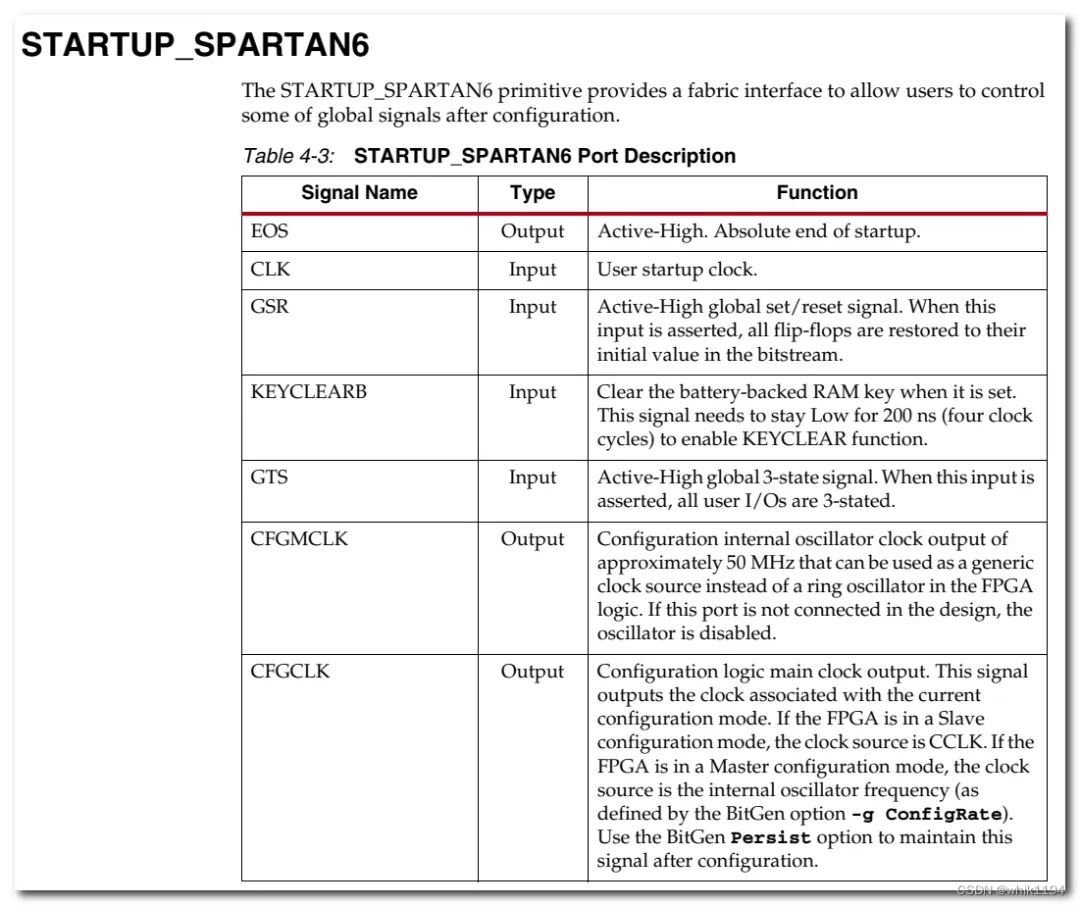

Spartan-6系列

wire clk_50m; wire rst_n; STARTUP_SPARTAN6 STARTUP_SPARTAN6_inst ( .CFGMCLK(clk_50m), // 1-bit output: Configuration internal oscillator clock output. .EOS(rst_n), // 1-bit output: Active high output signal indicates the End Of Configuration. );

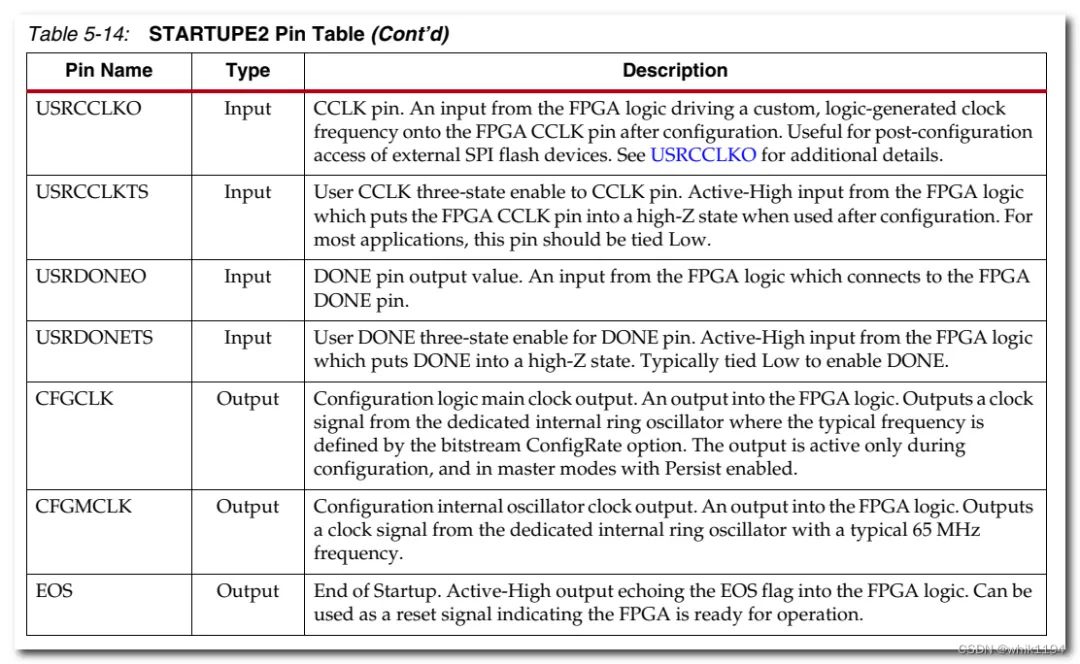

Artix-7(7系列)

wire clk_65m; wire rst_n; STARTUPE2 STARTUPE2_ut0( .CFGMCLK(clk_65m), // 1-bit output: Configuration internal oscillator clock output 65MHz. .EOS(rst_n) // 1-bit output: Active high output signal indicating the End Of Startup. );

分别可以参考文档:

UG380:Spartan-6 FPGA Configuration

UG470:7 Series FPGAs Configuration

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx FPGA的GTx的参考时钟2023-09-15 5473

-

复位信号是什么意思?复位信号的作用?详解Xilinx FPGA复位信号那些事2023-07-27 12732

-

Xilinx-DCM的使用方法技巧2021-09-28 1205

-

FPGA设计中常用的复位设计2021-06-30 3822

-

基于Xilinx FPGA的复位信号处理2020-12-25 3505

-

对于选择同步化的异步复位的方案2019-02-20 1655

-

Xilinx FPGA的同步复位和异步复位2018-07-13 7770

-

xilinx的Chipscope的使用方法2018-01-12 7818

-

Xilinx全局时钟的使用和DCM模块的使用2017-11-22 12846

-

xilinx原语使用方法2017-10-19 1368

-

xilinx 原语使用方法2017-10-17 1359

-

在FPGA开发中尽量避免全局复位的使用?(2)2017-02-11 1289

-

FPGA复位的可靠性设计方法2014-08-28 9540

-

Xilinx_FPGA_内部结构深入分析2012-08-02 2792

全部0条评论

快来发表一下你的评论吧 !