TC3xx芯片的Trap详解(二)之TC3xx芯片的产生

电子说

描述

前言

前面的文章<

问题1: 异常(Exception)和外部中断的区别?

问题2: 什么是NMI,如何产生NMI,NMI有什么用?

问题3: 除了NMI,用户如何主动制造异常?

问题4: 如何配置异常中断?

本文先详细介绍TC3xx芯片的产生,然后再回答上述问题:

参考文档:

1. Infineon-AURIX_TC3xx_Part1-UserManual-v02_00-EN

2. TriCoreTM TC1.6.2 core architecture manual

缩略词

| 简写 | 全称 |

| TCN | Trap Class Number |

| TIN | Trap Identification Number |

| TSR | Trap Service Router |

| NMI | Non-Maskable Interrupt |

| BTV | Base Trap Vector Table Pointer |

注:本公众号文章中使用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

1.TC3xx芯片Trap产生

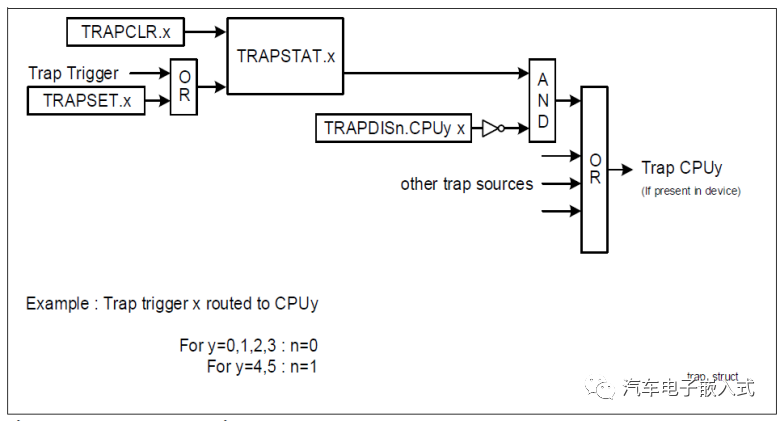

如图1所示,Trap请求(Trap Trigger)或者通过TRAPSET寄存器设置对应的trap bit都能置位对应的TRAPSTAT的状态bit. 寄存器TRAPDIS[0:1]位域确定哪些CPUs接收来自TRAPSTAT的trigger flag.默认状态下,Reset复位后所有的CPUs会接收Trap. TRAPSTAT寄存器中的trap flag可以通过写TRAPCLR寄存器的对应bit来清除。

Figure 1: CPU Trap Generation

1.1 Trap特点

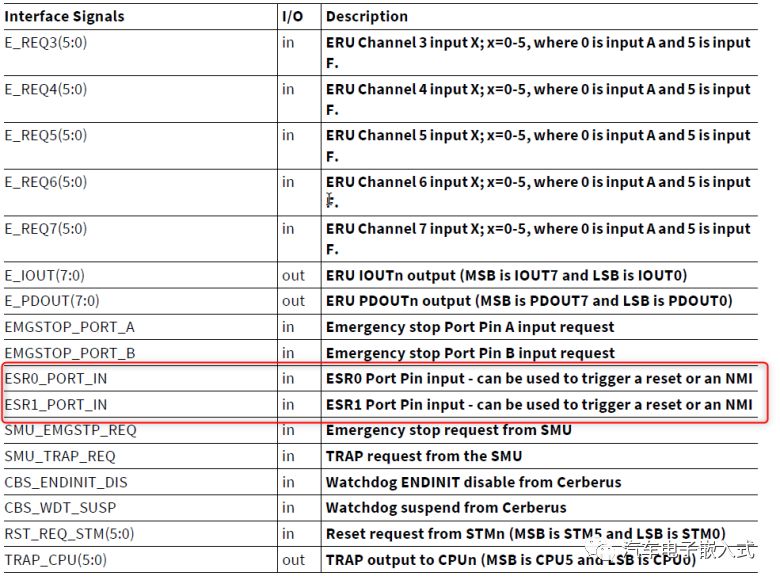

. 可以通过ESRx Pin脚触发Safety Alarm来触发CPU Traps.

. CPU Trap触发事件能够被TRAPSTAT状态寄存器捕获。

. 可以通过软件产生或者移除CPU Trap触发事件。

. 可以为单个 CPU 禁用或启用单个 CPU Trap触发事件。

Figure 2: Monitoring and Reset Pins

1.2 Trap处理

当启用(enable)Trap source并设置Trap状态标志时生成Trap时,建议在启用(enable) TRAPDISn 中的Trap source之前通过 TRAPCLR寄存器 清除Trap状态标志。 Trap状态标志可以在启用Trap source之前设置,只要启用Trap source,就会导致意外的 CPU 陷阱。 Trap处理例程结束时,应清除Trap状态标志。

1.3 Trap寄存器

主要有:

TRAPSTAT: Trap Status Register.

TRAPSET: Trap Set Register.

TRAPCLR: Trap Clear Register.

TRAPDIS0: Trap Disable Register 0.

TRAPDIS1: Trap Disable Register 1.

具体每个寄存器的位域作用参考芯片手册。

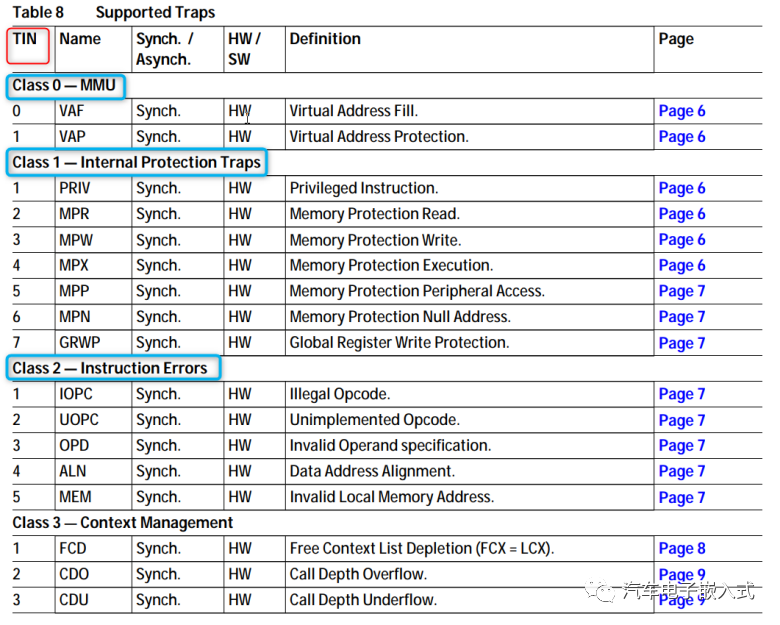

2.Vector OS对异常的处理

2.1 异常Exception和中断的关系

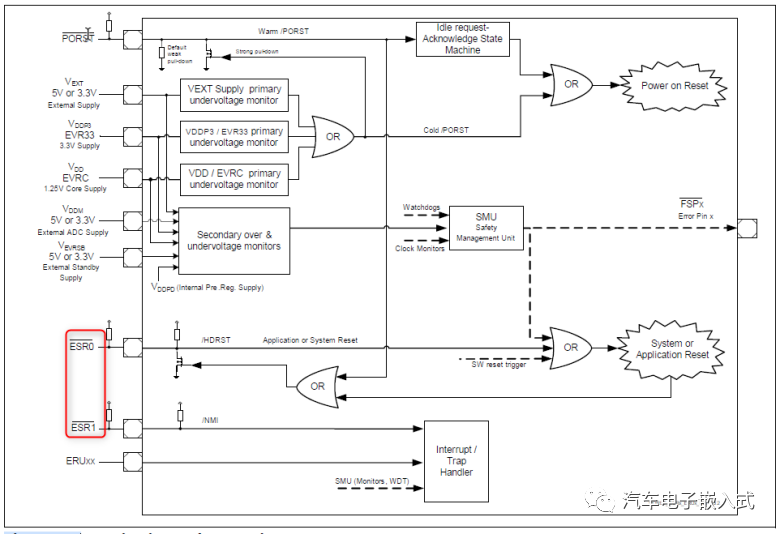

异常(Exception,Trap产生): BTV寄存器中保存了异常向量表(Exception Vector)的基地址,异常向量表中保存了所有用户配置和系统自带的异常护理程序(Exception Handlers)。系统产生Trap时(比如非法访问0地址)就会以 “中断抢占 “的方式调用对应的异常护理程序(Exception Handlers)。

中断(Interrupt,外部事件产生): BIV寄存器中保存了中断向量表(Interrupt Vector)的基地址。中断向量表中保存了所有用户配置和系统自带的中断护理程序(Interrupt Handlers)。系统产生外部(External)中断事件(比如配置了CAN的接收中断,收到CAN报文)时就会触发中断事件,系统就会调用对应的中断处理程序。

所以,严格意义上来讲,异常和中断没啥关系,只不过异常产生时会以“中断抢占“的方式调用异常处理程序,处理过程和外部事件触发的中断处理过程类似,都是抢占当前Task执行xxx handlers.

用户调用DisableAllInterrupts API可以禁用/屏蔽所有的中断,但是屏蔽不了Exception产生Trap,NMI(Non-Maskable Interrupt)实际上是一种Trap而不是ISR,只不过NMI Trap(Class 7)产生后一定会去调用Trap Handler/Exception Handler, 且过程也是“中断抢占“的形式,看上去就像”不可屏蔽的中断一样“。

2.2 Vector OS对异常处理

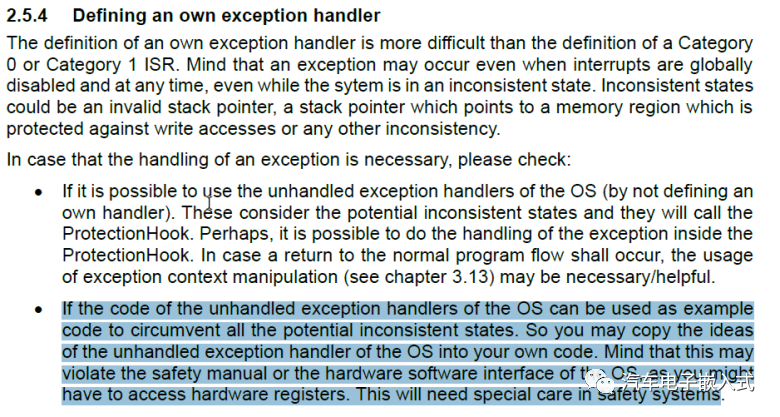

在<

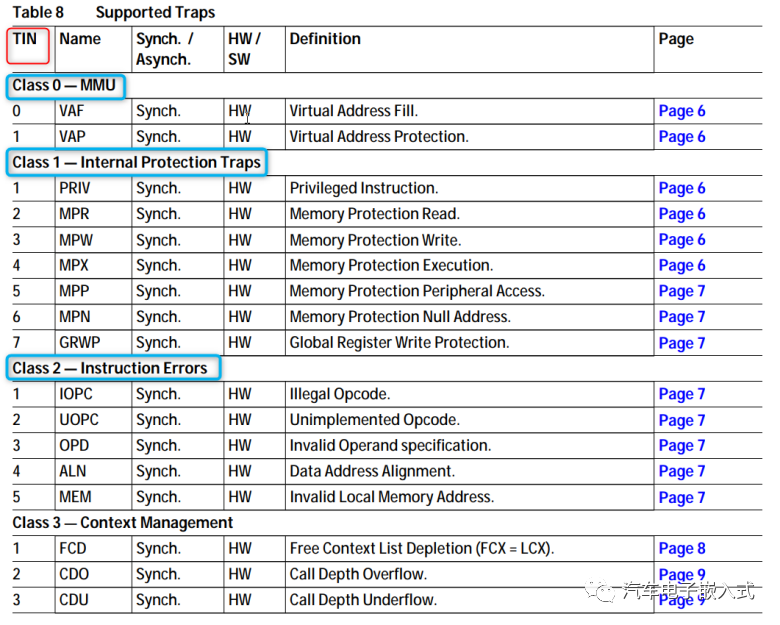

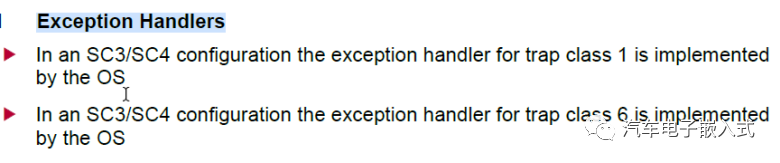

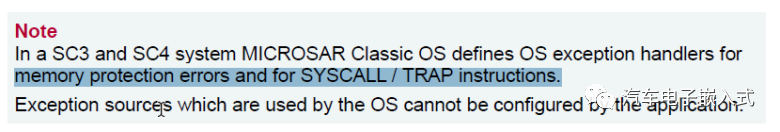

TC3xx的BTV寄存器保存了异常向量表的基地址。异常向量表里面保存了用户配置的异常处理程序,值得注意的是,Vector OS中以及实现了Class 1(memory protection errors) 和Class 6(SYSCALL / TRAP instructions) 的异常处理程序(exception handlers)。

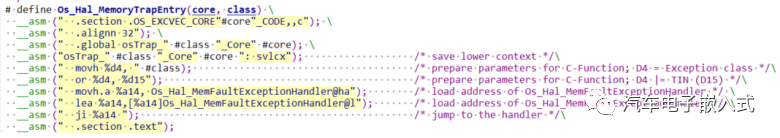

产生Class 1 Trap后OS会调用Os_Hal_MemoryTrapEntry:

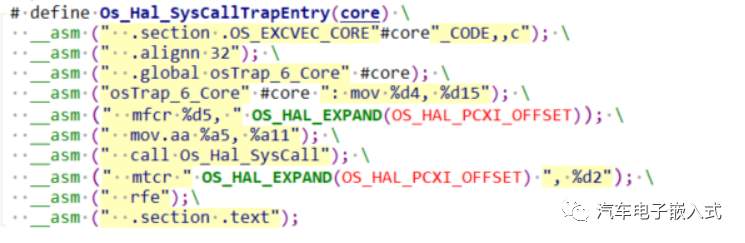

产生Class 6 Trap后OS会调用Os_Hal_SysCallTrapEntry:

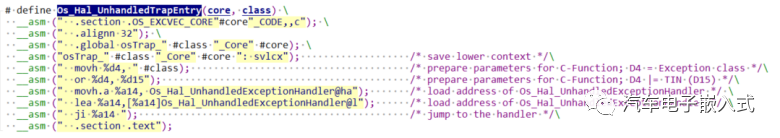

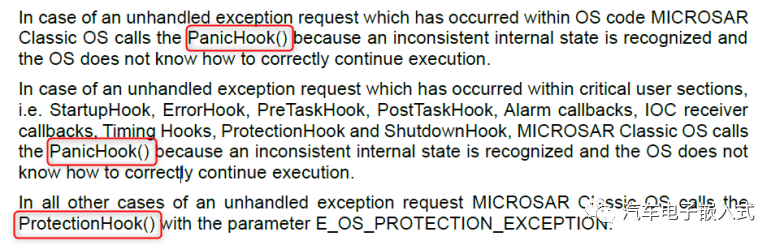

没有配置Handler的Trap产生后,OS就会调用Os_Hal_UnhandledTrapEntry,之后可能会调用PanicHooK()或者ProtectionHook():

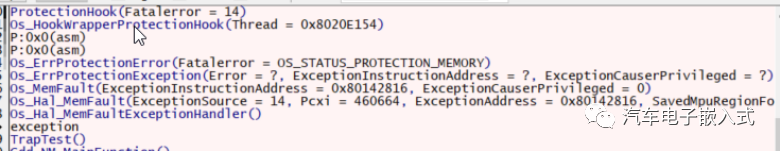

测试了一个Class 1 Trap,最后也会走到ProtectionHook:

对于非OS处理的Trap(非Class 1和Class 6)如果配置了自定义的Exception Handler, Trap产生后调用自定义的Exception Handler。

2.3 Infineon提供的关于Trap的接口

void Mcu_SetTrapRequest(const Mcu_TrapRequestType TrapRequestId);

void Mcu_ClearTrapRequest(const Mcu_TrapRequestType TrapRequestId);

typedef enum

{

MCU_TRAP_ESR0 = 0x0U, /* ESR0 trap request */

MCU_TRAP_ESR1 = 0x1U, /* ESR1 trap request */

MCU_TRAP_TRAP2 = 0x2U, /* TRAP2 trap request */

MCU_TRAP_SMU = 0x3U, /* SMU trap request */

MCU_TRAP_INVALID = 0x4U /* Invalid trap request */

} Mcu_TrapRequestType;

3.异常配置

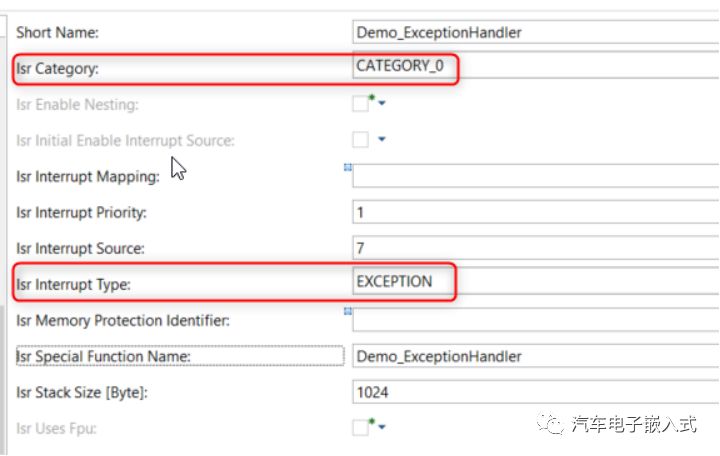

Exception Handler的配置基本和ISR一样,只有两个地方需要注意:

OsIsrInterruptType: 需要选EXCEPTION.

OsIsrCategory: 只能是CATEGORY_1 or CATEGORY_0.

4.NMI的作用

在第2章中我们知道NMI是Trap不是ISR。

如果我们不想通过外部IC触发NMI Trap: ESR1 Pin默认接到高电平(因为ESR1低电平有效默认触发NMI Trap)。

如果我们想使用NMI Trap: 比如把TLE35584 SBC的INT Pin脚接到ESR1,这样35584出现异常的时候,就能通过NMI_Handler快速的获取35584的错误状态。

5.总结

我们通过回答开头的几个问题来结束本文:

问题1:异常(Exception)和外部中断的区别?

答:参考2.1 异常Exception和中断的关系章节。

问题2:什么是NMI,如何产生NMI,NMI有什么用?

答:NMI是Class 7 Trap, 可以通过ESR1 Pin拉低触发NMI, NMI一般用来快速的捕获外部Exception.

问题3:除了NMI,用户如何主动制造异常?

答:可以通过调用Mcu_SetTrapRequest() API来设置Trap.

问题4:如何配置异常中断?

答:参考第3章节。

审核编辑:刘清

-

英飞凌AURIX™ TC3xx安全应用套件快速上手2025-12-19 154

-

两片TC3XX芯片之间的时钟同步可以实现吗?2025-08-04 1553

-

请问tc3xx如何配置多个dedicatedRxBuffersNumber?2025-04-21 2482

-

TC3xx的HSM中有没有单调计数器?2024-03-05 1420

-

深入解析TC3xx芯片中的SMU模块应用2024-03-01 3504

-

TC3xx系列是否支持RTC功能?2024-02-02 511

-

TC3xx系列怎么禁用trap?2024-01-31 637

-

TC3XX寄存器读写时间过长怎么解决?2024-01-25 631

-

英飞凌TC3xx系列安全管理单元的使用2023-12-07 4420

-

TC3xx芯片时钟系统的锁相环PLL详解2023-12-01 4671

-

TC3xx芯片的Endinit功能详解2023-11-27 4127

-

英飞凌TC3XX系列多核MCU学习笔记(1)2023-09-19 4660

-

TC3xx芯片DMU介绍2023-08-31 3635

-

AURIX™ TC3xx NVM是非易失性存储器学习笔记2023-06-19 12031

全部0条评论

快来发表一下你的评论吧 !