PCIe 5.0验证实战,经常遇到的那些问题?

电子说

描述

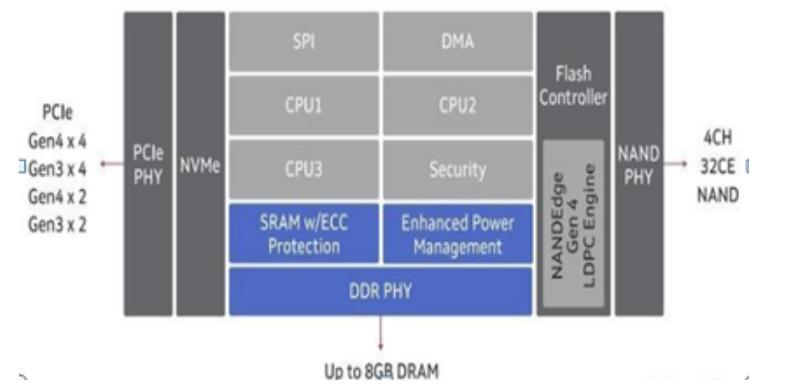

PCIe 5.0是当前最新的PCI Express规范,提供了更高的数据传输速率和更大的带宽。

PCIe是连接两个芯片的接口,负责两个芯片通信, 连接芯片的通路为高速SerDes, 称之为链路。PCIe确保通路正常-链路训练状态机。

PCIe在芯片内部是非常重要的一个大的模块,如果PCIe不能正常工作,那芯片则视为石头。

01 PCIe 5.0学习问答

Q :RC中几个端口,是否可以进行P2P间的验证?

解答 :看RC的具体实现,比如有些RC内部只有一个port也就不能进行p2p,之前做过这样的设计采用dual ip,这样就只有一个port,目前x86 RC内部port多,支持p2p,具体看下CPU Feature。

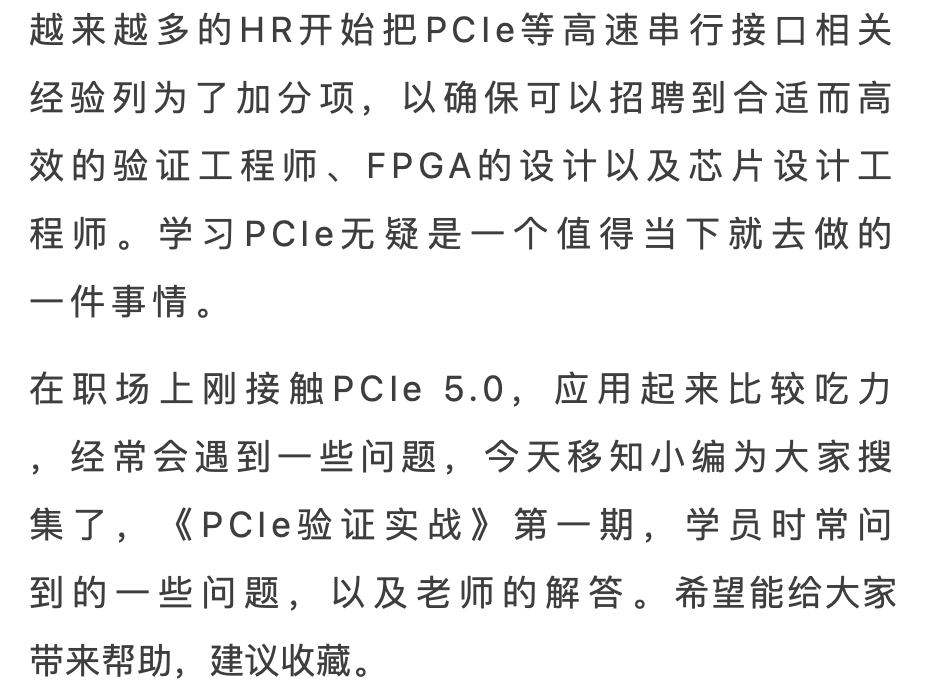

Q :PCIe链路训练均衡的问题;如何配置Synopsys的EP控制器的寄存器,使得在链路训练过程中修改HOST侧的PCIE PHY的TX preset值。GEN3_RELATED_OFF寄存器GEN3_EQ_CONTROL_OFF寄存器,通过配置EP的这两个寄存器配置是否可以实现,修改HOST侧的TX preset值。

解答 :

1-EQ流程,RX会根据CTLE/DTE评估的情况来调节对端设备的TX FFE。

2-源码分析,不能按照问题操作

3-需要仿真-doing

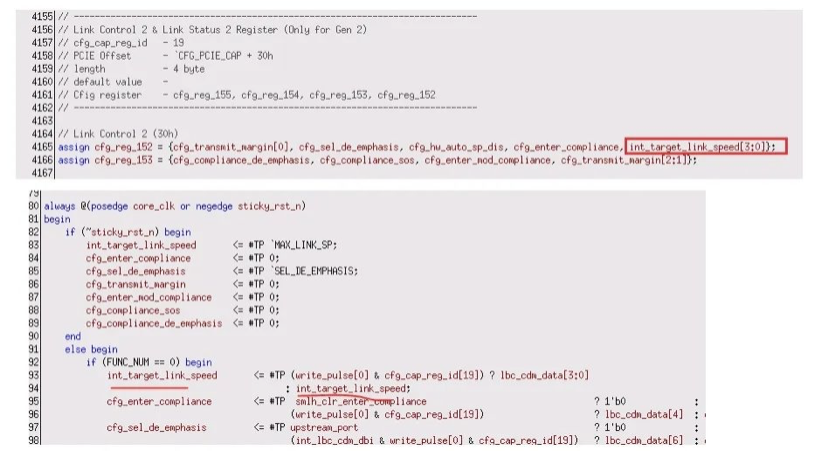

Q :EP在detect的时候TS1发出的 datarate只支持GEN1, 最终EP 和RC也training到GEN1 ,但此时发现 RC target speed 也切到GEN1 ,这个过程是哪一部分会修改到RC的target speed吗?

解答 :

1-bios到是有可能;我见过原型验证中有通过bios修改cpl timeout。

2-需要确认controller此寄存器会不会硬件自动修改,RTL代码确认不会修改。

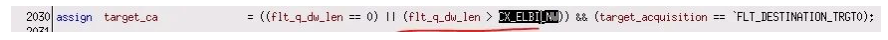

Q :cxl下rc remote访问EP的MEMBAR0下挂的ELBI接口空间支持2DW读?

解答 :

不支持,RTL代码返回CA

cxl文档里有一个ELBI2的方式,ELBI2将1K-DW(ELBI)扩展到512K-DW,这也是访问CCG Reg的方式。ELBI的空间太小,不满足要求。因此2dw的访问是ELBI2可以支持的,只是ELBI方式不支持。

Q :目标为16G,请问老师,LTSSM为什么跳过了5G,直接进入8G?

解答 :

到16G的训练流程就是2.5-8-16,pcie vip还提供了一种配置直接2-16.

6.0spce看到过这方面内容的描述。

Q :PCIE序的场景,需要列举

解答 :

读不超越写,请求依赖与响应因此响应不能依赖与请求,i响应包不能穿越P包(host读tag,ep写数据)。

-

硬盘开启PCIe 5.0时代2021-09-29 6648

-

PCB敷铜方面需要注意那些问题呢?2014-10-28 5213

-

请问在设计LED电源时需要考虑那些问题?2014-11-07 5554

-

请问pcb高频电路布线是需要注意那些问题?2019-03-29 1545

-

PCIe 5.0的接口设计有多难?2021-06-17 2296

-

本本内存升级 要注意那些问题?2010-01-26 949

-

51单片机进行串口通信时会遇到那些问题2019-04-12 1080

-

PCIe 5.0时代正式拉开序幕2021-02-05 4593

-

PCIe 5.0对互联芯片的性能验证要求2021-06-18 5823

-

什么是 PCIe 5.0? PCIe 5.0规范以及挑战2021-06-19 45735

-

microchip全新的PCIe 5.0交换芯片怎么样2022-01-04 5060

-

PCIE协议5.0完整版2022-09-13 1973

-

使用Synopsys VIP签署PCIe 5.0验证2023-05-26 3748

-

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?2023-11-18 6775

-

PCIe 5.0市场加速渗透,PCIe 6.0研发到来2025-01-27 7274

全部0条评论

快来发表一下你的评论吧 !