Arm使用PowerPro的输入限定方法

描述

随着 SoC 设计的复杂性与日俱增,SoC 的系统级功耗估算的重要性显著提高。系统级 RTL 功耗分析有助于在设计阶段的早期确定最坏情况下的系统功耗方案。RTL 功耗分析工具有助于分析大型设计的功耗,并且与门级分析相比,提供数据的速度要快得多。

.lib、FSDB/SAIF/STW/QWAVE

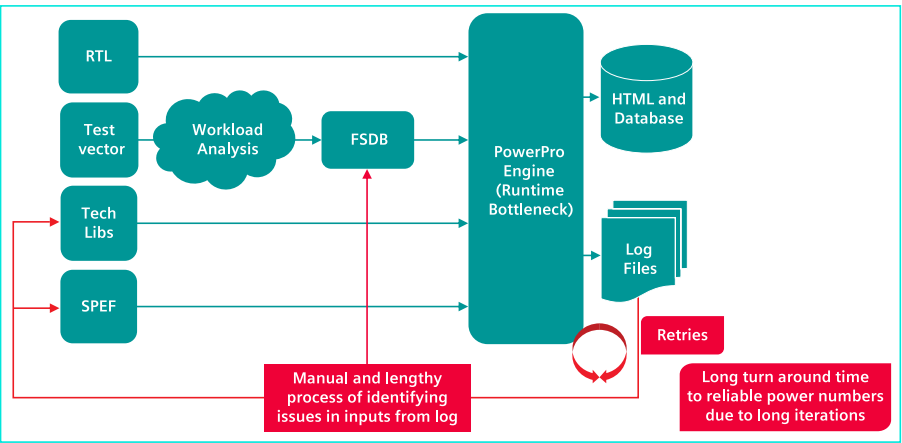

或SPEF等文件中的输入数据如果存在问题,则针对大型系统的功耗估算可能造成严重的延迟(图 1)。用户可以插入检查点检查数据完整性来标记这些问题。这些检查点有助于在用户偏离目标太远之前提前捕捉并修复问题,并且可以尝试生成一次正确的功耗数据,从而节省浪费在失败的尝试上的大量时间。

图 1:旧方法

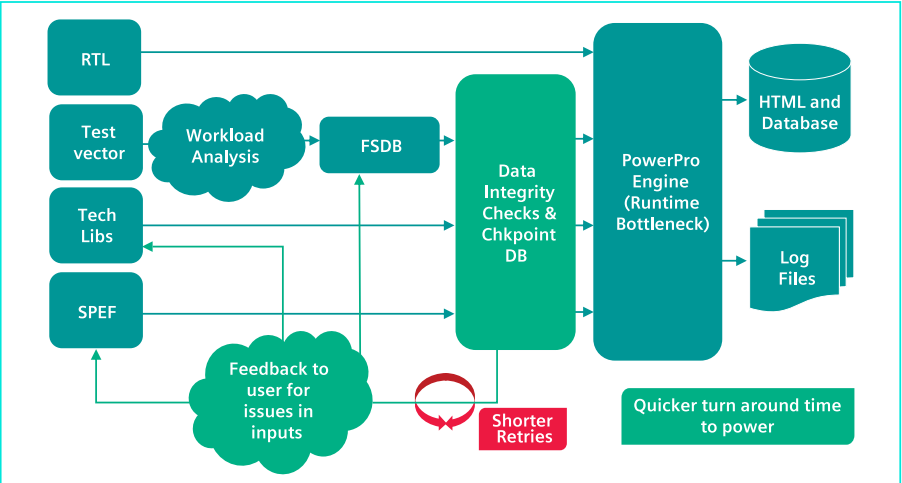

在设计构建和原型阶段拥有一种自动输入限定方法来执行各种数据完整性检查,这一点至关重要。这将确保在更快的迭代中,输入数据仍具有高保真度,并产生具有相关性的功耗数据。 西门子 EDA 的 PowerPro 解决方案为 RTL 设计人员提供了全面的功能集来实现低功耗设计。PowerPro 提供适用于 RTL 和门级设计的功耗估算、可在 RTL 开发期间快速查找功耗问题的早期功耗检查,以及可优化功耗设计的时钟和内存门控(图 2)。

图 2:新方法

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如果处理器的输入时钟频率超出了手册限定的范围,会导致什么样的结果?2024-03-25 522

-

PowerPro User 手册2023-03-31 440

-

学Qt,“大小限定”背后的思路和“坑”2023-02-02 2415

-

KeilC51与MDK-ARM并存方法2021-09-30 944

-

基于多新息和限定记忆的永磁同步电机参数2021-07-02 1000

-

空间限定零件列表2021-04-27 952

-

OPPO手环EVA限定版解析2020-07-15 3352

-

请问怎么把输入的直流或者交流限定在0到3v以便ad采集2019-04-08 1642

-

空间限定的集成FET的DC - DC转换器的介绍2018-06-24 4413

-

multisim简单的电路可以限定布单层PCB吗?2013-10-03 3584

-

ARM单片机开发调试方法2010-07-25 800

-

发射功率的限定2010-02-08 3943

-

基于ARM平台的MEMS输入设备的固件设计2010-01-20 819

-

AutoCAD中输入Φ的的常用方法2007-11-08 1780

全部0条评论

快来发表一下你的评论吧 !