DRAM的技术研发趋势

电子说

描述

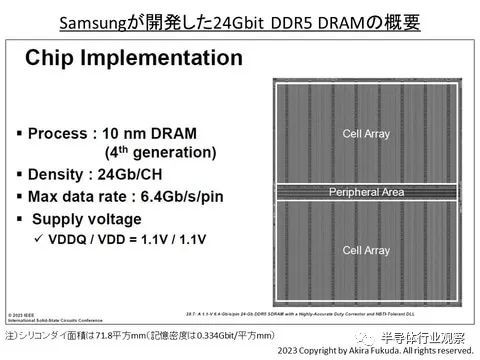

在2023年2月在国际学会ISSCC上,三星电子正是披露了公司研发的存储容量为24Gbit的DDR5 DRAM的概要(下图左)和硅芯片(下图右)。就在学会上发布的DRAM而言,该DRAM容量堪称最大。

自DRAM的生产技术世代进入10纳米代际(及20纳米代际以下)以来,已经过去五年。在这五年里,DRAM技术、产品情况皆出现了明显变化。虽然笔者一直在汇总一下DRAM的技术研发趋势,但其定位却发生了较大变化。本文中,笔者首先从2000年以来的DRAM技术开始回顾。

微缩化进步的牵引力不再是DRAM

业界普遍认为,在2000年之前,半导体生产技术的进步皆由DRAM的微缩化引领,甚至一度被誉为拉动工艺技术进步的“Process Driver(工艺牵引力)”。但是,进入2000年,情况却发生了变化。NAND闪存(当时的平面型存储半导体)的进步极大了带动了生产技术的微缩化发展。NAND闪存成为了微缩化加工的“牵引力主角”。

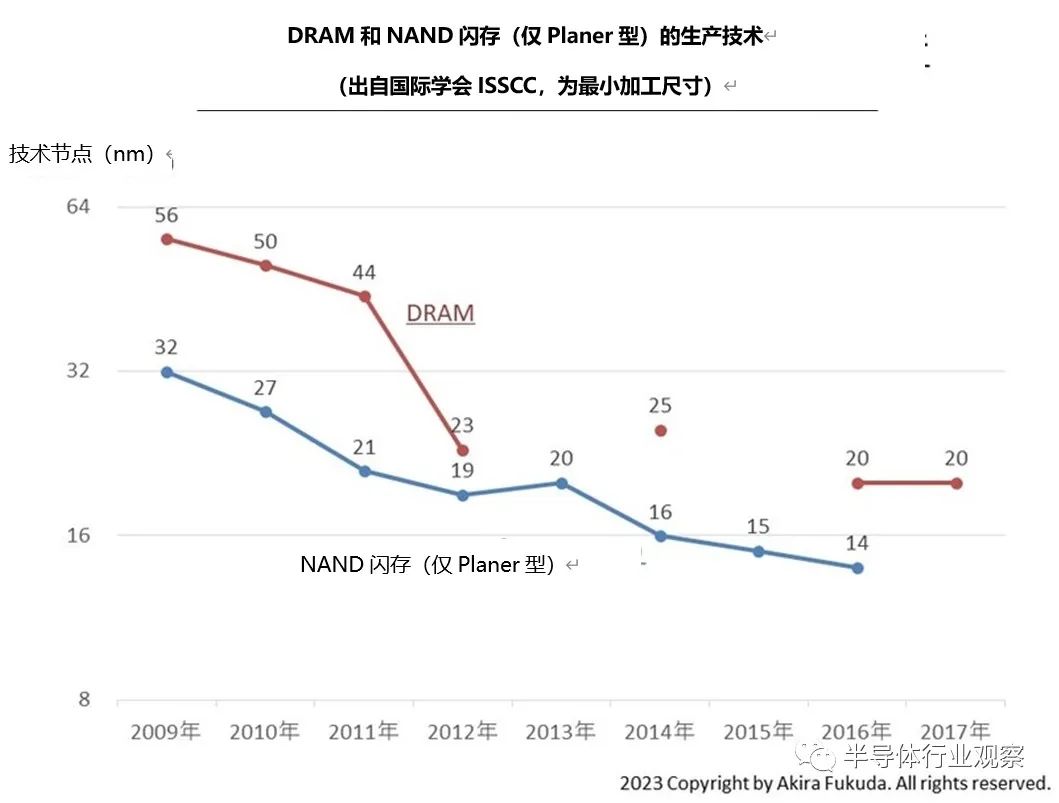

线路技术国际学会ISSCC(IEEE International Solid-State Circuits Conference,每年二月在美国旧金山举办会议)是全球半导体业界最知名单位,近期公布了其试做芯片的研发成果。2009年一2011年的技术节点(最小加工尺寸)如下,DRAM为56nm一44nm,NAND闪存(Planer型)为32nm一21nm。

DRAM和NAND闪存(仅Planer型)的技术节点(生产技术代际:2009年一2017年)。上图为笔者总结的国际学会ISSCC公布的试做芯片数据。(图片出自:pc.watch)

一度走在微缩化最前沿的NAND闪存在2015年达到极限,并放弃了加工尺寸的微缩化,改为3D堆叠。NAND闪存的微缩化几乎不再进步,2015年以后DRAM再次成为微缩化的主要驱动。

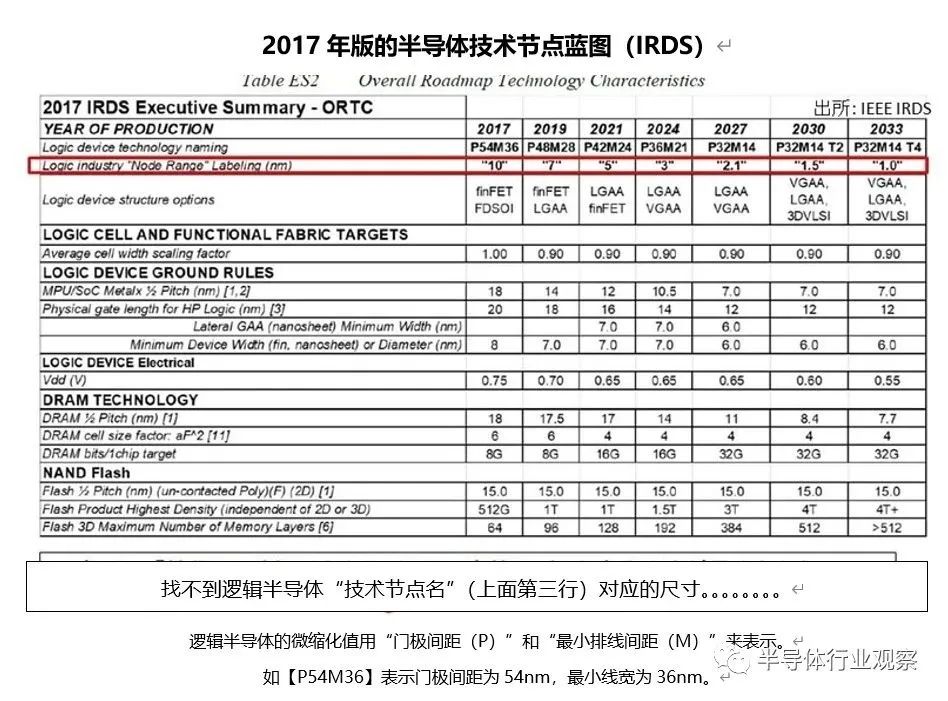

逻辑半导体的“技术节点名”与实际尺寸背离

2000年以前,主要由DRAM驱动整个半导体业界(存储半导体和逻辑半导体)的微缩化发展;但2015年一2024年DRAM却没有引领逻辑半导体微缩化发展。理由有以下两点。

其一,逻辑半导体晶体管的3D化。MOS FET结构从平面型改为3D FinFET,因此门极长度(Gate Length,或者是“沟道长度”,一直是半导体微缩化的指标)的定义将不再有意义。取而代之的是“标准单元(Standard Cell,逻辑半导体的最小单位)”的“门极间距(Gate Pitch)”和最小线宽(严密来讲,应该是二者的积)。当下最尖端逻辑半导体的“技术节点”5纳米、7纳米等数值,不过是一个标签符号,实际(硅芯片)是不存在的。

2017年版的半导体技术蓝图(IRDS)。从上至下为逻辑半导体、NAND、DRAM、NAND闪存(技术代际为笔者推测)。可以看出,找不到逻辑半导体技术节点(红框)对应的尺寸。(图片出自:pc.watch)

其二,逻辑半导体芯片·工艺技术与DRAM芯片·工艺技术的差异很大。在每一代逻辑半导体生产工艺中,晶体管的技术变化或大或小,如应变硅(Strained Silicon)、HKMG(高介电率金属门极)、FinFET、COAG(Contact Over Active Gate)等。此外,还已经研发了铜(Cu)排线、低介电率的绝缘层膜等,并全面投入应用于多层排线。

DRAM的技术节点反映了真实的物理尺寸

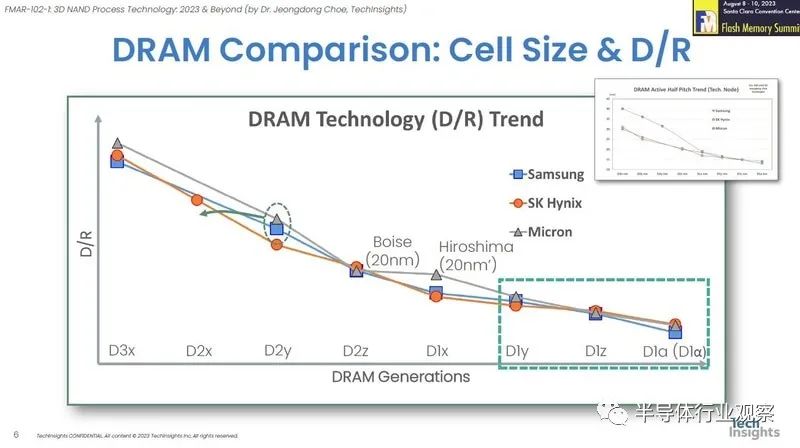

DRAM的技术节点名称与实际尺寸接近,且不同于逻辑半导体。DRAM的技术节点名称多以代码来表示,如30纳米代际为“D3z”、20纳米代际为“D2x”。

依据代码也不难推测出其技术节点,如“D2x”约为28纳米、“D2y”约为25纳米、“D2z”约为22纳米。虽然技术节点的代码依DRAM厂家不同而不同,但差异不大。

大型DRAM厂家的技术节点和设计规则(D/R)之间的关系。可以看出,大型DRAM厂家的技术节点名称和实际设计规则之间存在差异。出自TechInsights公司(一家提供半导体芯片解析服务的企业)于2023年8月在“闪存峰会”上公布的资料。(图片出自:pc.watch)

技术节点相当于尺寸的现象存在于存储单元阵列(Memory Cell Array)的“活跃区(Active Region,或有源区、主动区)”。“活跃区”排列准确,且间距(Pitch)的1/2(Half Pitch)即为技术节点名称。换句话说,“D1x”代际(18纳米代际、也被成为1Xnm)的DRAM硅芯片的单元晶体管以36nm间距排列。

从TechInsights公司于2018年12月的披露的数据来看,三家DRAM厂家的“D1x”代际(1Xnm、Half-pitch)的最小尺寸如下,三星电子为18纳米、SK海力士为17.5纳米、镁光科技为19纳米。三家差异不大。

DRAM芯片的基本架构

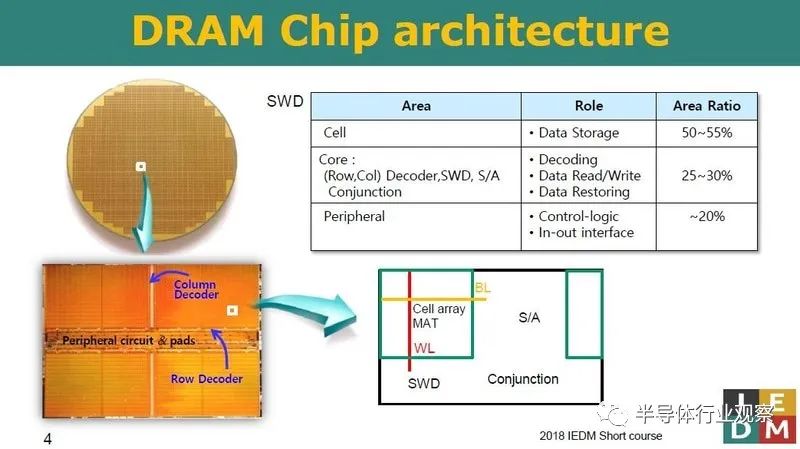

接下来笔者将介绍DRAM芯片的基本架构(Architecture)。在DRAM的制造工艺中,厂家会尽可能多地在硅晶圆上制作DRAM芯片。从硅晶圆上切出的一颗DRAM芯片通常分为“存储单元阵列区域(通常由偶数个Sub-array构成)”和“周边线路区域(Peripheral)”

“存储单元阵列”作为DRAM的存储区域,理论上应该是2维阵列形状(Matrix)。就如同象棋棋盘或者奥赛罗(Othello)黑白棋的棋盘一样,行和列的交叉点即为“存储单元(Memory Cell)”,由“行的编号”和“列的编号”锁定存储单元的范围。此处,行的编号为“行地址(Row Address)”、列的编号为“列地址(Column Address)”。

在存储单元阵列区域,又分为“存储单元”、“核(Core)”。存储单元用于存储信号,由一个晶体管(MOSFET)和一个电容(Capacitor,即Cell Capacitor)构成。核(Core)内线路如下,从存储单元阵列中选择所需存储单元,并读取、写入数据。且配有“字线解码器(Word Line Decoder,用于选择单元晶体管的门极(字线))”、“位线解码器(Bit Line Decoder,用于选择源极(位线))”、用于放大数据读取和写入信号的“Sense Amplifier”、用于连接各部分的排线等。

周边线路(Peripheral)由控制线路和输出线路构成。控制线路主要根据外部输入的指令、地址,让DRAM内部工作。输出/输入线路负责数据的输入(写入)、输出(读取)。

上图为DRAM的基本架构说明图。左上角为硅晶圆照片(推测实际直径尺寸为300mm)。左下角为DRAM的硅芯片照片。硅芯片中心左右两侧有周边线路、输出/输入Pad点、行解码器(Row Decoder),中央的上下部分有列解码器(Column Decoder)。上图右下角是存储单元阵列(Sub-array)的基本结构。红色字线(WL)和黄色位线(WL)的交叉点上有一个存储单元。字线的端部配与副字线驱动(SWD)相连、位线的端部与读出放大器(Sense Amplifier,简称为“SA”)相连。上图右上角为各部分占硅芯片的比例。存储单元占50一55%,核(解码器、驱动器、读出放大器、相互连接部分)占25一30%,周边线路(Peripheral,控制线路和输出线路)占20%左右。在2018年的国际学会IEDM的技术讲座上,三星电子公布了其相关资料,上图出自其资料。(图片出自:pc.watch)

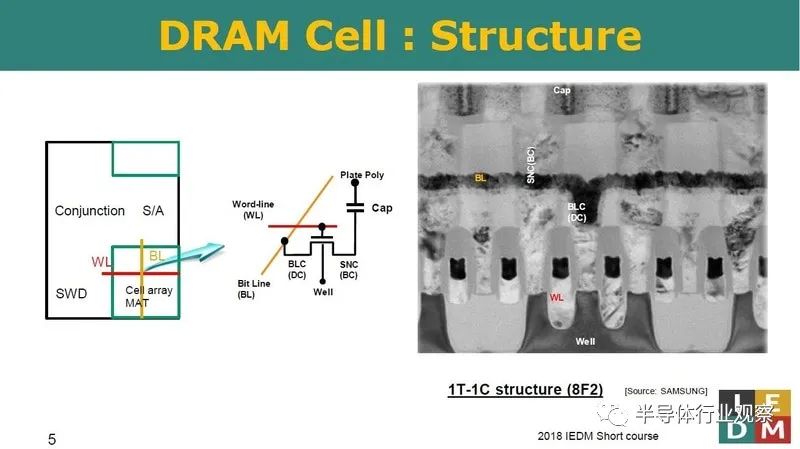

通过将电荷储存于电容,存储理论值

DRAM的存储单元由一个晶体管(简称为:“T”)和一个电容(简称为:“C”)构成。在存储半导体行业,普遍称之为“1T1C”。晶体管具有选择开关的作用,因此也被称为“选择晶体管”。读取/写入动作时,字线解码器和位线解码器选择的位线和字线的交叉点的“选择晶体管”成为“ON”状态。

存储单元的电容(在性能上与作为电子零部件的电容类似)主要存储电荷信号,也被称为“单元电容”。当电容存储一定容量的电荷后,存储单元的理论值为“高(或者1)”。相反,当存储的电荷不满时,存储单元的理论值为“低(或者0)”。

DRAM存储单元的线路事例(左图)、电子显微镜下观测到的存储单元断面图(右图)。左侧线路图下,选择晶体管(通常为n渠道MOSFET)的门极为字线(红色:WL)、源极为位线(黄色:WL)。选择晶体管的漏极(Drain)经由单元电容与平板(Plate)电极相连。在右侧的断面图中,红色部分(WL)为选择晶体管的门极(字线)、BLC为位线连接、SNC为存储节点连接(Storage Node Connect)。SNC上方与电容(照片中的Cap部分)相连。SNC文字左侧的黄色字“BL”为“位线”。(图片出自:pc.watch)

DRAM存储单元的基本动作和Refresh

在将数据写入DRAM时,利用解码器将指定位置的选择晶体管改为“ON状态”,同时,将读取的数据暂存于输入缓存区(Buffer),然后,利用读取放大器将数据转为电流、为单元电容充电。

充电后,随着电容的不断放电以及时间的流逝,写入的数据(电荷)会逐步消失。因此需要定期写入数据的动作。该动作被称为“Refresh”。2000年以前的DRAM而言,采用的是一个外接的存储控制器在适当的时间点实施“Refresh”。最近,大部分产品采用的是在产品内部实施“Refresh”。

读取数据时,把选择晶体管改为“ON”状态,单元电容的电荷以电流的形式流向“位线”。位线的电流利用读取放大器(S/A)以电压的形式增压,电压信号经由输出缓存区向外输出。

在读取工作中,需要注意的是单元电容的电荷可能会因为读取工作而丢失。读取放大器可以及时修复读取的数据(即重新写入)。

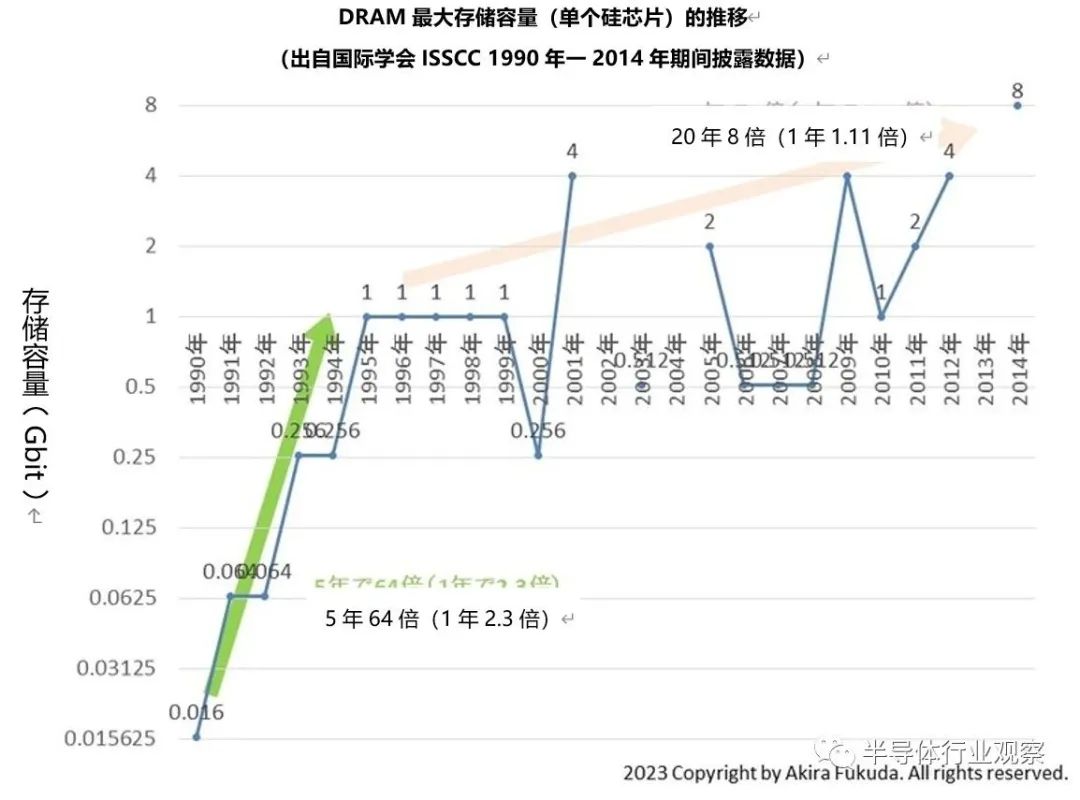

2000年后,DRAM存储容量增长不明显

2000年以前,尤其是上世纪70年代和80年代DRAM的存储容量增长极其明显。存储半导体行业曾有“三年四倍”的说法,即存储容量扩大了四倍的新一代DRAM会在三年后量产。主流用户虽然从20世纪70年代的Main-flame变成了80年代的Workstation和90年代的PC,但DRAM厂家并没有辜负“三年四倍”的惯例。

从国际学会ISSCC(每年二月份召开)上公布的硅芯片的概要来看DRAM的研发情况,如下,最初为最大存储容量,20世纪90年代初期,容量进步速度远超“三年四倍(甚至为1年1.59倍)”。1990年为16Mbit,在1995年为1Gbit,即“五年64倍(1年2.3倍)”。

然而,1995年以后,存储容量的增长就不再明显。1999年之前,一直保持着1Gbit的最大容量。后来,又徘徊于256Mbit和512Mbit、1Gbit、2Gbit、4Gbit。但却迟迟没有进入新一代的4Gbit。2014年和2016年公布了8Gbit的硅芯片,可以说终于从1Gbit进步了1.5个代际。其实,进步速度为“20年8倍”(1年1.11倍),可以说是DRAM研发历史上容量进步最慢的一次。

DRAM最大存储容量(单个硅芯片)(1990年一2014年)。此图为笔者汇总自国际学会ISSCC披露的数据。可以看出,1996年~2012年期间,容量进步不明显(年度扩大率为1.11倍)。(图片出自:pc.watch)

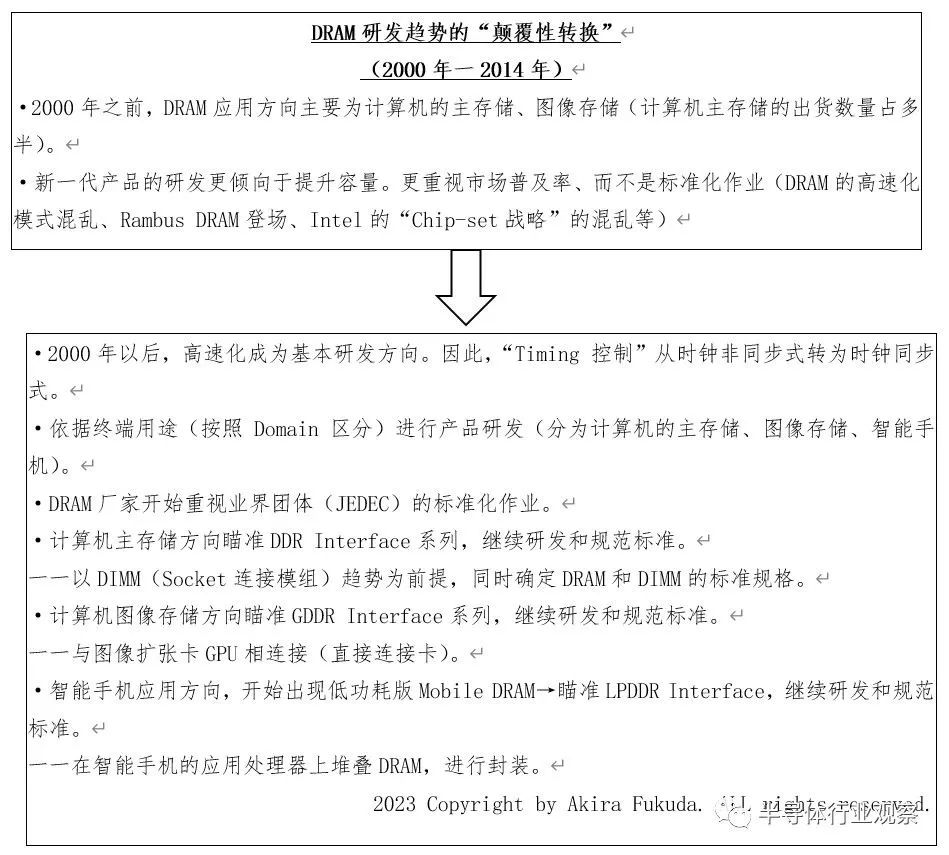

DRAM研发的“颠覆性转换”

1995年~2014年期间的20年中,DRAM研发又发生了什么呢?粗略来讲,研发方向发生了很大变化。甚至可以说是“颠覆性转换(Paradigm Shift)”,即DRAM的研发方不再是扩大容量,而是提升速度。

DRAM数据传输速度(单个输入/输出Pin)的推移表(2000年一2012年)。笔者汇总自国际学会ISSCC披露的数据。上述三个系列的年度容量扩大速度均超多1.11倍。(图片出自:pc.watch)

为了提升存储速度,采用“时钟(Clock)同步”的方式控制动作时间。最初,为了与传统的DRAM(Clock-less式非同步DRAM)区分,称之为“SDRAM(S:Synchronous)”。如今,大家看到“DRAM”一般就默认为“同步式”(或者不去刻意区分同步还是非同步)。严格来讲,DRAM(如DDR、LPDDR、GDDR等)应该被记为“SDRAM”,因此在企业的产品目录、学会论文中一般会记录为“SDRAM”。

可以看出,SDRAM的新一代标准式样是有意强调其速度之快而做成的。最初的SDRAM是以时钟速度输入/输出速度的。此时的时钟频率为133MHz。新一代SDRAM可以以两倍时钟速度输入/输出数据,即“DDR(Double Data Rate) SDRAM”。时钟频率高达200MHz,数据的输入/输出速度是时钟的两倍,即400MT/s的输入/输出Pin(此处T=Transfer,即传输次数,即一次传输接收/发送1bit,bit/秒)。

近年来,每一代DDR系列SDRAM的数据输入/输出速度都较前一代提升两倍。在国际学会ISSCC上公布的DDR系列SDRAM的数据传输速度如下,自2003年至2012年,9年内提升到4.4倍,即1.18倍/年。

Graphics DRAM(显存)也采用DDR,并积极提升传输速度,即G(Graphics)DDR、SGRAM(Synchronous Graphics RAM)。GDDR系列的SGRAM的传输速度正不断攀升。国际学会ISSCC上披露的GDDR系列SGRAM的数据传输速度如下,2004年至2010年期间的六年内,增长至4.4倍,即1.28倍/年。

随着智能手机的普及,开始研发低功耗版的SDRAM。最初被称为“Mobile DRAM”,后来基于“LP(Low Power)DDR SDRAM”的名称研发逐步步入正轨。2009年国际学会ISSCC上首次披露LPDDR系列的试做版硅芯片。当时的Hynix 半导体公司研发的1Gbit芯片的数据传输速度为1.066Gbps/pin。即在2012年之前,LPDDR系列的数据传输速度提升至1.5倍(1.14倍/年)。

DRAM研发方向出现“颠覆性转变”(2000年一2014年)。1995年一2004年(或至2014年)期间的10年(或20年)内,发生了诸多变化。(图片出自:pc.watch)

2000年以后的DRAM研发战略方向主要如下,高速化(通过导入时钟同步式的设计)、依据产品应用方向进行研发、依据应用方向确定封装(Packing 或Module)标准。NAND闪存是大容量的“主角”。2005年,在ISSCC上披露了NAND闪存存储密度超过DRAM的信息。可以说,如今已经步入了“NAND闪存容量大、DRAM速度高”的时代。

审核编辑:刘清

-

DRAM的范式转变历程2023-11-25 2820

-

关于DRAM市场趋势的“虚假谎言2023-11-08 1160

-

DRAM芯片2022年价格增长趋势.zip2023-01-13 414

-

DRAM发展趋势#硬声创作季电子学习 2022-11-20

-

DRAM原理 - 1.存储单元阵列#DRAMEE_Voky 2022-06-28

-

兆易创新DRAM芯片自主研发及产业化项目完成资金募集2020-08-17 3777

-

长鑫存储正在加速从DRAM的技术追赶者向技术引领者转变2019-09-26 4227

-

长鑫存储副总裁披露DRAM技术发展现状和未来趋势2019-09-20 8398

-

长鑫存储亮相闪存技术峰会 引领中国DRAM技术突破2019-09-19 819

-

DRAM技术或迎大转弯,三星、海力士搁置扩产项目2018-10-12 2812

-

展望2013:DRAM产业五大重点趋势预测2013-01-10 1459

全部0条评论

快来发表一下你的评论吧 !