测试平台的建立方法

描述

(1)DUT模型的建立

•① 164245模型:在Modelsim工具下用Verilog HDL语言[5],建立164245模型。164245是一个双8位双向电平转换器,有4个输入控制端:1DIR,1OE,2DIR,2OE;4组8位双向端口:1A,1B,2A,2B。端口列表如下:

input DIR_1,DIR_2,OE_1,OE_2;inout [0:7] a_1,a_2,b_1,b_2;reg [0:7]

bfa1,bfb1,bfa2,bfb2;//缓冲区

•② 缓冲器模型:建立一个8位缓冲器模型,用来做Test bench 与164245 之间的数据缓冲``

(2)Test bench的建立

依据器件功能,建立Test bench平台,用来输入仿真向量。 Test bench中变量定义:

reg dir1,dir2,oe1,oe2; //输入控制端

reg[0:7] a1,a2,b1,b2; //数据端

reg[0:7] A1_out[0:7]; //存储器,用来存储数据

reg[0:7] A2_out[0:7];reg[0:7] B1_out[0:7];reg[0:7] B2_out[0:7];

通过Test 图6 Test bench验证平台框图

图6 Test bench验证平台框图

(3)仿真和验证

通过Test bench 给予相应的测试激励进行仿真,得到预期的结果,实现了器件功能仿真,并获得了测试图形。图7和图8为部分仿真结果。

图7 仿真数据结果

图7 仿真数据结果

在JC-3165的*.MDC图形文件中,对输入引脚,用“1”和“0”表示高低电平;对输出引脚,用“H”和“L”表示高低电平;“X”则表示不关心状态。

由于在仿真时,输出也是“0”和“1”,因此在验证结果正确后,对输出结果进行了处理,分别将“0”和“1”转换为“L”和“H”,然后放到存储其中,最后生成*.MDC图形文件。

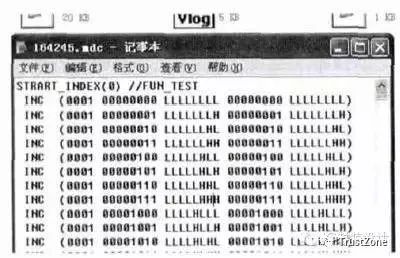

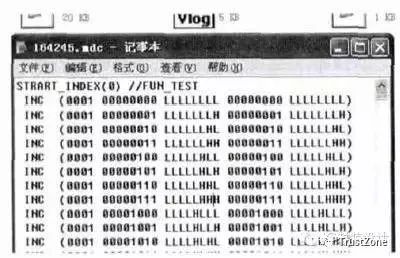

图8 生成的*.MDC文件

图8 生成的*.MDC文件

-

一种新的建立自动测试系统的方法2009-07-15 706

-

新型雷达数字电路便携式自动测试系统设计2009-11-28 742

-

一种变频器测试平台及变频器测试平台的调试方法2016-03-01 955

-

光立方制作步骤2016-03-15 1225

-

8×8×8光立方测试程序程序、原理图2016-11-23 2796

-

光立方制作方法2016-12-09 1483

-

基于MapXtreme的虚拟漫游2D导航地图建立方法研究_朱振和2017-03-18 912

-

基于雷达的杂波速度谱图的建立方法2017-11-18 4141

-

一种云平台可信性分析模型建立方法2018-01-13 870

-

ISE环境下基于Verilog代码的仿真测试pdf下载2018-02-24 1114

-

基于计算机模拟技术的太阳能光伏发电系统数学模型的建立方法2018-08-09 6738

-

华为推送会话的建立方法的优点2019-12-17 2793

全部0条评论

快来发表一下你的评论吧 !