ATE如何测试PLL

描述

两种方法: 时域和频域测试,如下:

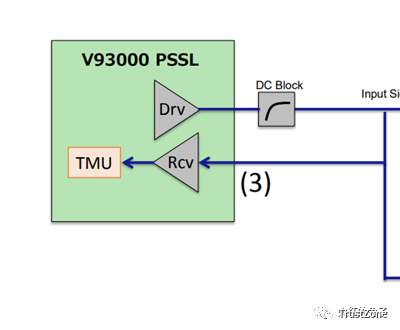

•方法1. ATE time measurement unit ( TMU)测试。(时域,需要额外的TMU license,因此常不采用。)

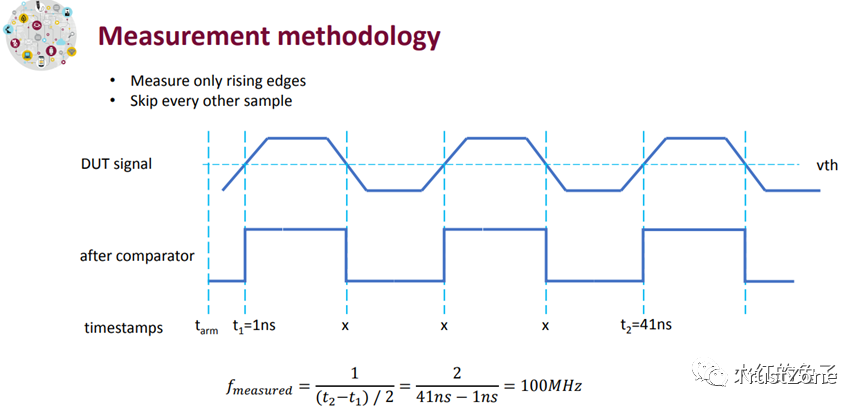

实施步骤:ATE 构造TMU TASK。TMU可以非常高精度地根据task设置trigger到上升沿的时刻,因此可以通过两个上升沿的差值计算出频率,支持多次采样,如下图所示:

•方法2. 构造采样向量,离散傅里叶公式计算频谱,频谱的最大和第2大频率转换即为待测信号频率。(频域)

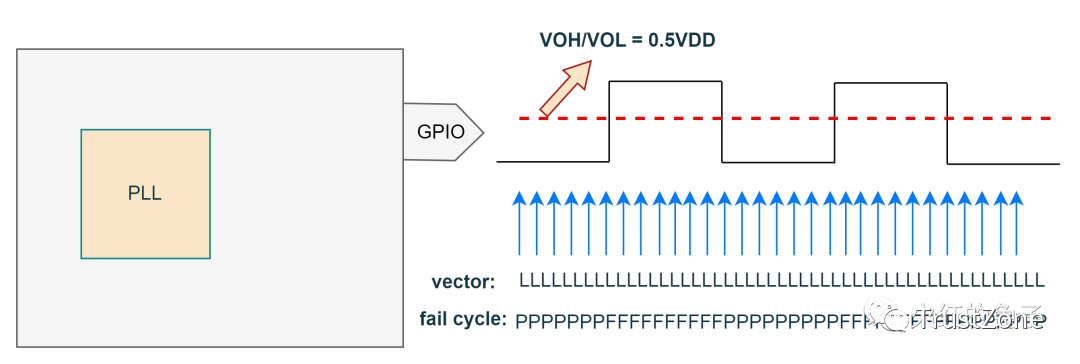

•a)预先构造一条全L的向量,假设叫做PLL_sample.

•b) 运行DFT PLL向量的测试项。运行后, 不复位的情况下DUT此时稳定输出时钟信号。

•c) 运行预先构造好的向量PLL_sample,收集fail cycle,也就是ATE的error

map。获得一串0/1组成的一维序列,如下图(点击可放大):

•d)。对获得一维序列进行汉明窗口卷积后,使用快速离散傅立叶变换获得频谱。通过频谱可以相当高精度的获得输出的频率,通过spec进行分bin。

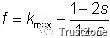

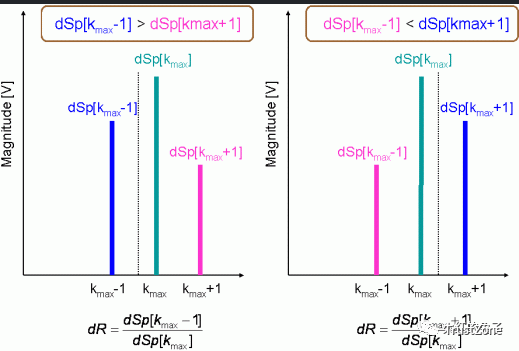

实际步骤:首先应用DSP_FFT与汉明窗口。然后搜索频谱第一大主频kmax 和第二大频,(kmax-1 或者kmax+1)。如图所示,第1大和第2大频率成为关键参数。

核心为两个公式:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

聊聊IC测试机(4)DFT PLL向量,ATE怎么用?2023-11-01 5100

-

如何使用ATE对CPLD进行测试???2013-02-17 2693

-

AMD(苏州)招聘ATE测试工程师和懂ATE测试的产品工程师。2015-03-10 5691

-

基于ATE的DSP测试方法2017-10-20 1398

-

ATE自动化测试系统是什么_ATE自动化测试系统介绍2018-05-23 33343

-

基于ATE的集成电路测试原理和方法综述2021-06-17 2299

-

DFT如何产生PLL 测试pattern2023-10-30 3694

-

ate测试系统是什么?为什么要选择ate电源测试系统?2023-11-07 3872

-

在ATE测试中,需要注意哪些事项呢?2023-11-09 1990

-

纳米软件带你了解ate测试及ate自动测试系统2023-11-24 2322

-

ATE自动测试设备怎么测试逆变器输出电压?2023-12-28 2383

-

芯片的出厂测试与ATE测试的实施方法2024-04-19 4934

-

ATE自动测试设备原理及特点介绍2024-07-09 4160

-

ATE测试系统如何构建?先搞懂这些总线技术2025-04-01 1272

-

ATE测试是什么?电源企业为什么必须上自动化测试?2026-03-24 328

全部0条评论

快来发表一下你的评论吧 !