二维材料给功率半导体带来了什么?

描述

重大进展

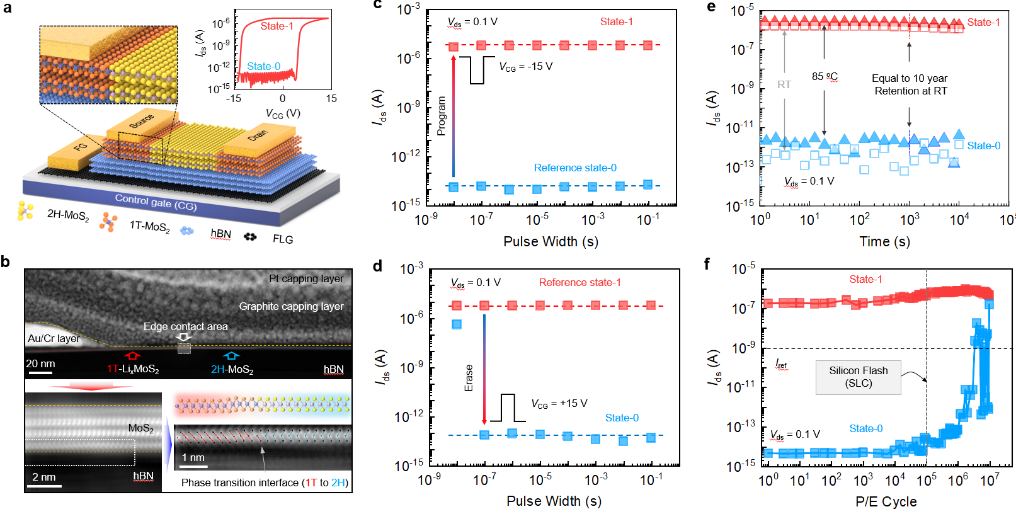

9月15日,华中科技大学材料成形与模具技术全国重点实验室的翟天佑教授团队宣布,其研发团队在二维高性能浮栅晶体管存储器方面取得重要进展。

图1 边缘接触式二维浮栅存储器的表征及其操作性能。(华中科技大学供图)

什么是浮栅晶体管

浮栅晶体管是一种特殊的MOS晶体管。作为一种电荷存储器,是构成当前大容量固态存储器发展的核心元器件。

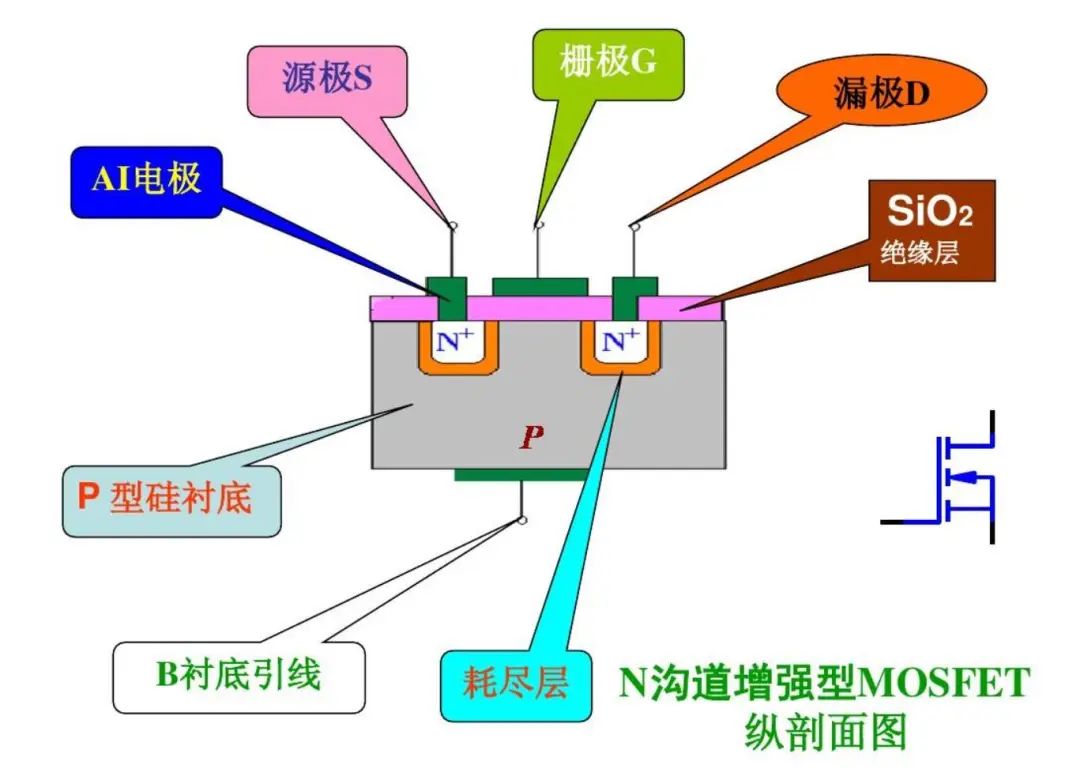

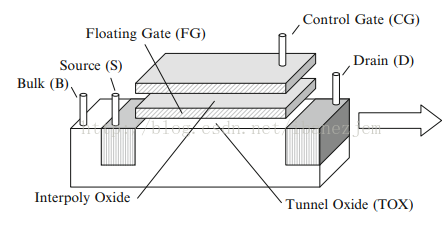

剖析它的结构会发现,晶体管由三个部分组成,源极(Source,电流入口)、漏极(Drain-电流的出口)、栅极(Gate-开关)。在晶体管中有两个多晶硅形成的栅极, 其中一个带有有电气连接的叫控制栅,也叫栅极; 另一个没有外引线, 完全被包裹在二氧化硅介质层里面的浮空控制栅叫做浮栅。

图2 N沟道增强型MOSFET纵剖面图

图3 浮栅结构图

华中科技大学研究所制备的新型二维浮栅晶体管提高了传统浮栅晶体管的擦写速度、循环寿命,存储性能更加优异,使其商用价值大幅上升。

浮栅晶体管与晶体管

浮栅晶体管隶属于晶体管。而晶体管(transistor),本名为半导体三极管(包括二极管、三极管、场效应管、晶闸管等,有时特指双极型器件),是内部含有两个PN结,外部通常为三个引出电极的固体半导体器件。它对电信号有放大和开关等作用,基于输入的电压来控制流出的电流。多用于检波、整流、放大、开关、稳压、信号调制和许多其它功能。是功率半导体的重要组成部分。

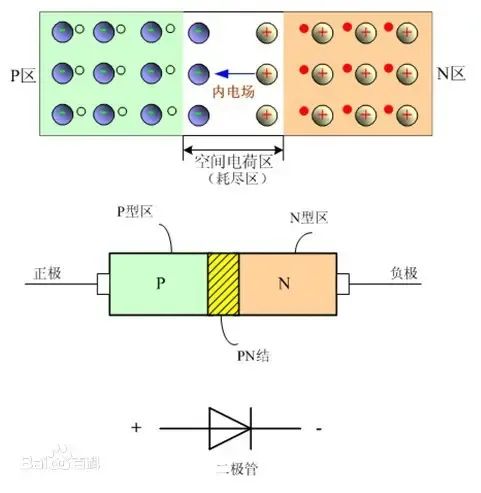

PN结原理

PN结(PN junction)是在一块本征半导体(纯净的,不含杂质的半导体)中,掺以不同的杂质,使其一边成为P型,另一边成为N型。随后将P型半导体与N型半导体制作在同一块半导体基片上,在P区和N区的交界面形成一个空间电荷区,叫做PN结。

图4 PN结工作原理示意图

晶体管的主要制作原料是半导体材料(即导电率介于导体和绝缘体之间的材料)。根据晶体管中PN结的材料、掺杂分布、 几何结构和偏置条件等基本特性的不同,可以生成很多种不同功能的晶体二极管。

传统晶体管材料有硅、锗、镓、砷等。但正如上文所说,不同晶体管的工作特性激发着原材料市场的不断更新改革。近年来,科学家们一直致力于晶体管原材料新的可能性的研究。这时,二维材料应运而生。

在纳米尺度上,二维材料电子传导性更高,正因如此,二维材料逐渐成为了下一代晶体管材料中替代硅的重要竞品材料。

二维材料——功率半导体的下一个“风口”

二维材料,全名为二维原子晶体材料。是指电子仅可在两个维度的纳米尺度(1-100nm) 上自由运动(平面运动)的材料,如纳米薄膜、超晶格、量子阱。其中包括石墨烯,氮化硼(BN)、二硫化钼(MoS2)、二硫化钨(WS2)、MXene材料。石墨烯是最主流的二维材料。具有单原子层厚,高载流子迁移率、线性能谱、强度高的特点,常被用于半导体科学研究。

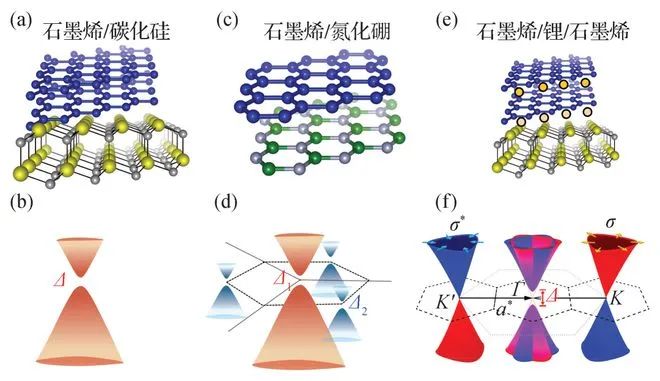

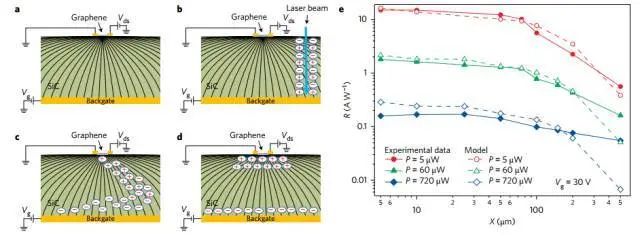

图5 石墨烯基光电晶体管原理图

需要了解的是,虽然材料本身性能优秀,但受限于商用制备过程中的制造成本,设备要求,以及在接触电阻、栅介质等方面的瓶颈,截止到目前,二维晶体管所能实现的性能比起传统硅基晶体管依然稍显逊色。

研究成果

1、由过渡金属二硫化物(TMD)的2D材料为基础制造简单功能晶体管

本项研究成果由麻省理工学院(MIT)团队开发。采用“非外延单晶生长”方法,在现有的工业硅晶圆上生长出纯净无缺陷的二维材料,并制造出更小的晶体管。本项成果有效提高了晶体管的导电性。

2、晶圆级硅基二维互补叠层晶体管

本项研究成果由复旦大学周鹏、包文中、万景团队合作开发。研究团队利用硅基集成电路的标准后端工艺,将二硫化钼(MoS2)三维堆叠在传统的硅基芯片上,形成p型硅-n型二硫化钼的异质互补CFET结构。此项成果大幅降低了叠层晶体管的制备工艺难度,提高了管体寿命。

3、10纳米超短沟道弹道二维硒化铟晶体管

本项研究成果由北京大学电子学院彭练矛院士、邱晨光研究员团联合开发。该晶体管的其实际性能已经超过英特尔商用系列中最先进的硅基晶体管。本次实验首次达成了n型二维半导体晶体管的性能理论极限现实化,并且证明了先进硅基技术性能劣于二维器件。

4、二维材料的硅微芯片集成技术

本项研究成果由沙特阿卜杜拉国王科技大学科学家开发。团队将二维绝缘材料(约6纳米厚的层六方氮化硼),集成到包含由互补金属—氧化物半导体技术制成的硅晶体管的微芯片内。本次实验大大提升了硅晶体管微芯片的集成密度和产品性能。

5、全彩色垂直堆叠μLED

本项研究成果由麻省理工学院的Jeehwan Kim开发。本项全彩色垂直堆叠μLED成果的最高阵列密度为5100像素每英寸,尺寸为4微米。是公开数据中的最高阵列密度和和最小尺寸。

总结

虽然短期内我们还不太可能看到二维材料在晶体管,乃至整个功率半导体市场上的商用化,但二维材料的理念其实已在功率半导体研发和生产中无孔不入。相信在解决了量产瓶颈后,二维材料会为功率半导体市场带来一场华丽蜕变。

审核编辑:刘清

-

世界首台非硅二维材料计算机问世 二维材料是什么?二维材料的核心特征解读2025-06-12 1313

-

二维材料 ALD 的晶圆级集成变化2024-06-24 1040

-

首次实现GHz频率的二维半导体环形振荡器电路2023-11-24 1680

-

12英寸二维半导体晶圆的批量制备完成2023-07-13 728

-

中国团队成功实现12英寸二维半导体晶圆批量制备技术2023-07-12 1233

-

我国突破12英寸二维半导体晶圆批量制备技术2023-07-10 2166

-

基于垂直架构的新型二维半导体/铁电多值存储器2022-11-28 1036

-

二维半导体晶体管实际沟道长度的极限2022-10-17 3936

-

单元素二维半导体材料及应用专刊2020-08-27 6511

-

二维材料家族包含了哪些材料?2020-06-05 14840

-

探讨二维材料在半导体和能源产业的应用2018-10-26 7039

-

二维材料模块的自组装实现,获得高质量半导体薄膜2018-06-28 2999

-

半导体所发表二维材料层数相关光学性质的综述论文2017-01-11 2138

-

低维半导体材料, 低维半导体材料是什么意思2010-03-04 5958

全部0条评论

快来发表一下你的评论吧 !