相位噪声到抖动的转换(上)

电子说

1.4w人已加入

描述

相位噪声和抖动是对时钟频谱纯度的两种表述形式,一个是频域一个是时域,从原理上来说,它们是等效的。

工程中以PLL为例,往往需要对PLL进行噪声建模,建模的目的是根据各模块的电压、电流、相位噪声及各模块(PFD、CP、LPF、VCO、PREDIV、FBDIV)到输出的传函得到时钟上的RJ抖动。

这里就涉及到电压、电流、相位噪声如何转换成时域抖动,电压、电流噪声到抖动的转换相对简单,本篇重点介绍相位噪声(如VCO、DIV)到抖动的转换。

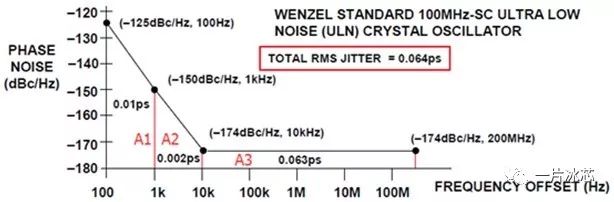

相位噪声转换到抖动的基本思想就是对相位噪声曲线进行积分。参考文献给出了相位噪声与抖动之间的转换关系如图1所示,其中A1~A4代表图形面积(可通过积分算出),fo为中心频率。

Fig1.Calculating Jitter from Phase Noise

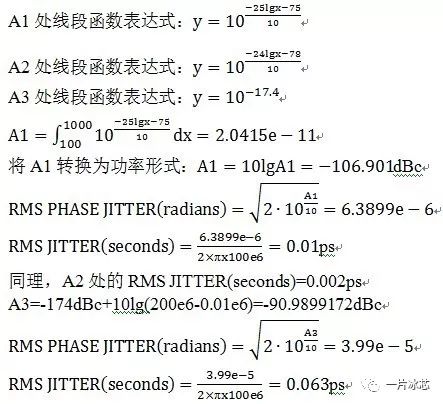

图1给出了计算抖动的公式,图2为参考文献中给出的A1~A3 RMS JITTER计算结果,下面给出具体计算方法。

Fig2. Jitter Calculationfor Low Noise 100-MHz Crystal Oscillator

A1在对数坐标下(100,-125)和(1000,-150)两点之间的斜率恒定,计算面积时用对数坐标是不合理的,因此转换后A1~A3处的函数表达式如下:

上述红色字体与图3计算结果一致!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

相位噪声到抖动的转换(下)2023-10-30 8073

-

怎样将相位噪声和抖动降至最低及其估算方法2009-10-13 3667

-

相位噪声的RMS抖动2018-10-10 8422

-

怎么将相位噪声转换为抖动?2019-08-13 5331

-

低相位噪声&抖动2020-06-10 3075

-

如何区分抖动和相位噪声?2021-03-11 1409

-

测量较低时钟频率的相位噪声和相位抖动2021-06-24 3757

-

时钟抖动(CLK)和相位噪声之间的转换2009-04-22 4897

-

相位噪声和抖动的概念及其估算方法2009-12-27 3297

-

MT-008: 将振荡器相位噪声转换为时间抖动2021-03-20 1206

-

将振荡器相位噪声转换为时间抖动2021-04-30 862

-

时钟抖动使随机抖动和相位噪声不再神秘2022-11-07 820

-

相位噪声与时间抖动有何关系?如何测试时间抖动?2024-01-31 2245

-

时钟抖动与相位噪声的关系2024-08-19 2763

-

相位、相位噪声与抖动:从原理到测量2025-08-15 4834

全部0条评论

快来发表一下你的评论吧 !