CWQ2P50型现场可编程门阵列电路

描述

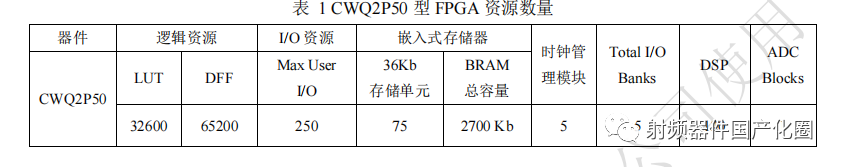

CWQ2P50是基于 SRAM 配置的高密度可编程逻辑阵列电路。其中,6输入查找表数量32,600个,嵌入式存储器容量为2,700Kbit,用户I/O数量250个,内置5个时钟管理模块,具有120个DSP数字信号处理模块,资源数量列如表 1 所示。

产品特点

CWQ2P50主要用于具备高级串行连接功能的高性能信号处理应用。

CWQ2P50具有以下特点:

基于可配置为分布式存储器的真实6输入查找表(LUT)技术的高级高性能FPGA逻辑;

强大的时钟管理块(CMT),结合了锁相环(PLL)和混合模式时钟管理器(MMCM) 模块,可实现高精度和低抖动;

具有内置FIFO逻辑的36Kb双端口Block RAM,用于片上数据缓冲;

具有25x18乘法器, 48位累加器和预加器的DSP slice,用于高性能滤波,包括优化的对称系数滤波;

灵活的配置选项,包括: SPI和并行 Flash接口; 专用的回读重配置逻辑,可支持多比特流;自动总线宽度检测功能;

对所有器件都有系统监控功能, 包括: 片上/片外热特性监控; 片上/片外电源监控; 通过 JTAG端口访问所有监控量;

采用境内28nm工艺设计加工,芯核电压0.9V;

采用高可靠军级塑封,采用Flip-Chip键合方式;

用户可配置的模拟接口(XADC),将双12位1MSPS模数转换器与片上温度传感器和电源传感器结合在一起;

多种配置选项, 包括对存储器的支持,具有HMAC / SHA-256身份验证的256位AES 加密以及内置的SEU检测和校正。

产品用途

CWQ2P50为可编程逻辑器件,内部集成了功能强大、并可以灵活配置组合的可编程资 源, 可实现输入输出接口、通用数字逻辑、存储器、数字信号处理、时钟管理等多种功能, 同时提供了丰富的专用时钟与布线资源, 适用于实现复杂、高速的数字逻辑电路,可广泛应用于通讯、信息处理、工业控制、数据中心、仪表测量、医疗仪器、人工智能、自动驾驶等领域,尤其适用于低功耗、小型化应用场景。

对应国外产品情况

主要性能指标、引脚与Xilinx公司FPGA产品 XC7S50 ( FGG484)对标。

-

翟爱豆豆

2024-05-24

0 回复 举报CWQ2P50是那家的FPGA呢? 收起回复

翟爱豆豆

2024-05-24

0 回复 举报CWQ2P50是那家的FPGA呢? 收起回复

-

现场可编程门阵列是什么2024-03-16 4202

-

CWQ2P690T型现场可编程门阵列电路产品概述2023-10-27 3121

-

FPGA-现场可编程门阵列2021-07-30 1249

-

XA6SLX25-3CSG324Q现场可编程门阵列2021-04-26 1527

-

XC7K325T-2FFG900I现场可编程门阵列2021-04-13 1176

-

现场可编程门阵列有哪些应用?2019-08-06 4097

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 1053

-

现场可编程门阵列2015-03-13 2350

-

现场可编程门阵列的供电原理及应用2010-03-17 1894

-

现场可编程门阵列的结构与设计2009-07-07 1960

全部0条评论

快来发表一下你的评论吧 !