相位噪声到抖动的转换(下)

电子说

描述

上期介绍了如何用Matlab计算相位噪声与抖动之间的转换,这期以具体案例来介绍相位噪声与抖动转换的几种常用工具。相位噪声转换到抖动的基本思想就是对相位噪声曲线进行积分。

换句话说,能实现相位噪声积分的工具都可以拿来进行噪声转换。下面以JitterLab、Excel、Spectre为例说明噪声转换的具体方法。

1. JitterLab积分

以SILICON LABS公司的Si5368芯片(该芯片可提供2kHz~945MHz的低噪

声时钟,常用作PLL的参考源)为例来说明JitterLab的使用方法。

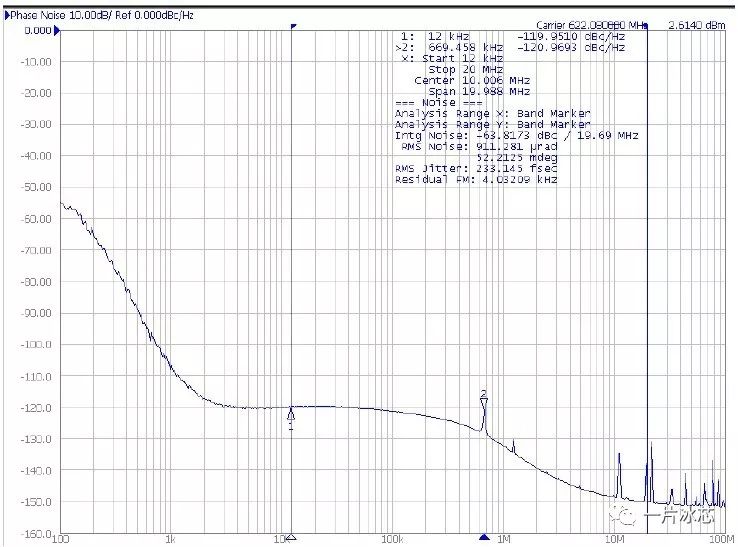

图1给出了Si5368芯片典型情况下的相位噪声曲线,曲线右上角给出了12kHz~20MHz的RMS Jitter为233.145fs @Carrier=622.08MHz。

Fig1. Si5368芯片的相位噪声曲线

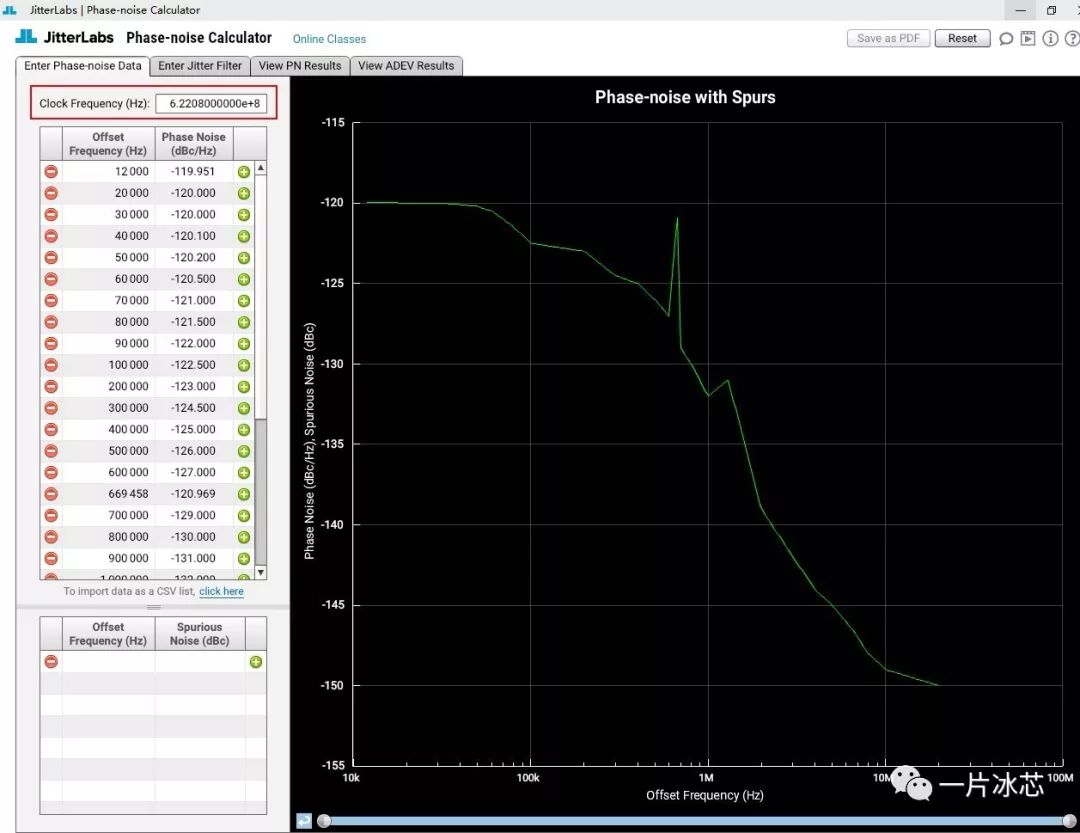

将12k~20MHz的点导入JitterLab(载波频率填622.08MHz),如图2所示:

Fig2. 12k~20MHz 导入JitterLab后的相噪曲线

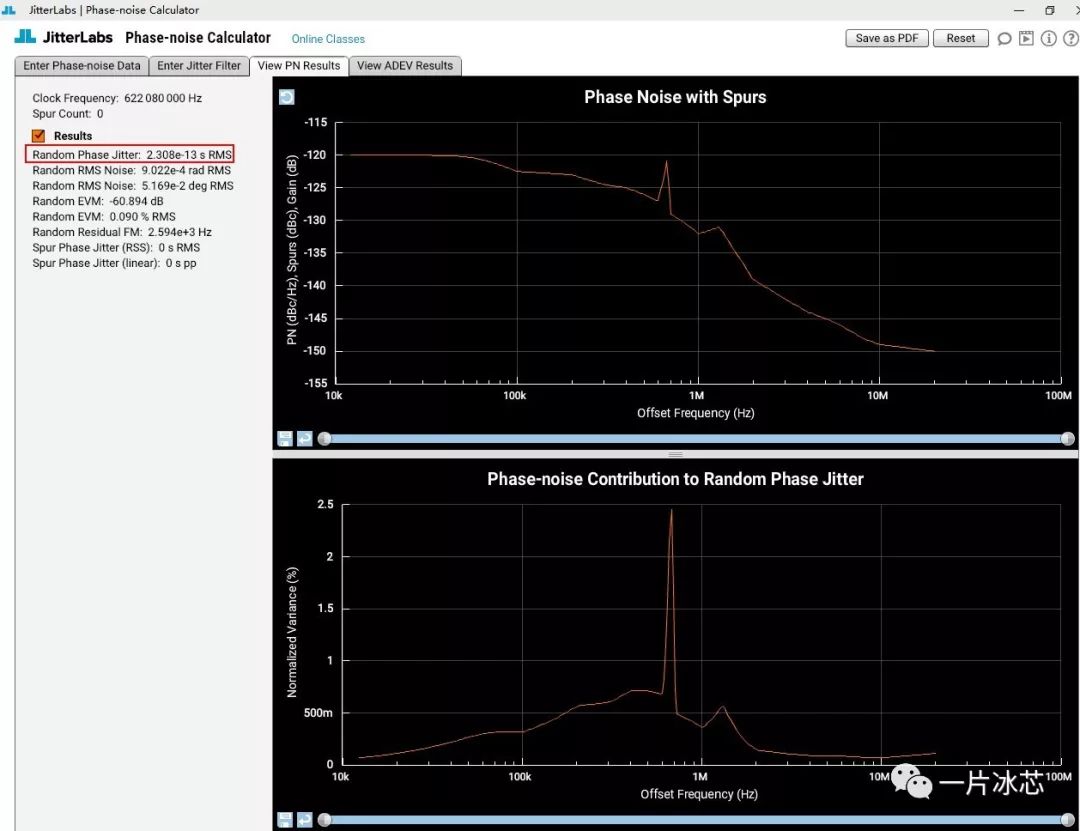

图3给出了RMS Jitter为231fs ,与Si5368 Spec中给出的一致,说明了JitterLab的准确性。图3 Phase-noiseContribution to Random Phase Jitter曲线表示12kHz~20MHz范围内各频率下的噪声贡献。

Fig3. 12k~20MHz 内JitterLab积分结果

2. Excel积分

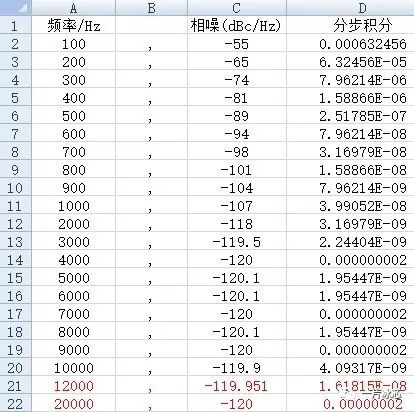

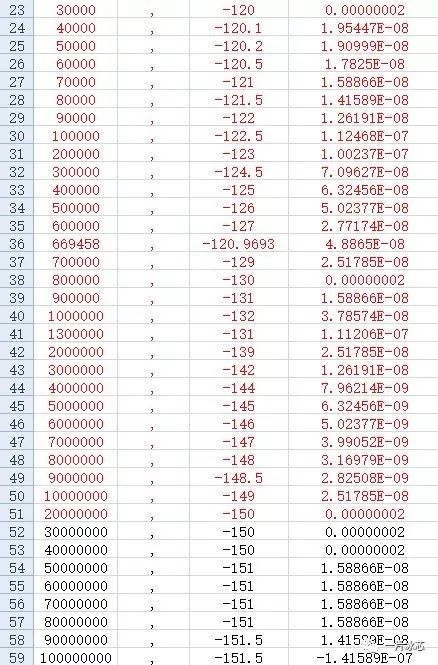

用Excel计算Si536812k~20MHz的RMSJitter之前应先用10 ^相位噪声^ ^/10^公式对相位噪声进行处理,得到电压噪声,然后再乘以Δf,再进行求和。图4中D21和D22中的公式分别为:2*(10^(C21/10)) (A22-A21)、2 (10^(C22/10))*(A23-A22),依次类推,直到D51(红色字体),乘2是转换成双边带。

Fig4. Si5368相噪数据及积分公式

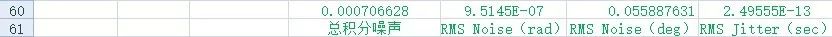

图5 E60中的表达式为(=SUM(D21:D51)),G60中的表达式为(=(SQRT(E60)/6.283185)*(1/622080000))。Excel得到的RMSJitter为250fs与Si5368的Spec及JitterLab计算结果一致。

Fig5. E60与G60表达式

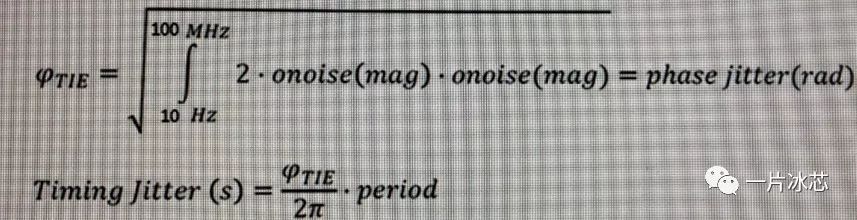

计算公式:

3. Spectre积分

Spectre计算Jitter的方法与Excel类似,都是采用第2节最后给出的Timing Jitter公式。仿真得到相位噪声通过dBc2V2=(10**(rfOutputNoise(“dBc/Hz”?result “pnoise”) / 10))公式将相位噪声转换成电压噪声(dBc/Hz到V ^2^ /Hz的转换)。得到电压噪声后用Rms_Jitter_Per_UI=(sqrt(integ(((getData(“out”?result “noise”)**2) * 2) 10 100000000 “ ”)) / 6.283185)公式得到每UI的RMSJitter,其中10100000000为积分区间。同理可得到:P2P_Jitter_Per_UI=((sqrt(integ(((getData(“out”?result “noise”)**2) * 2) 10 100000000 “ ”)) / 6.283185) *14)。

**4. **补充说明

1)以PLL为例计算输出时钟的RMSJitter步骤可分解为:①用veriloga或matlab建立PLL包含各模块噪声的行为级模型;②将相位噪声和电流噪声转换成电压噪声;③将各模块的电压噪声代入对应输入节点,然后进行noise仿真,得到时钟上的的RJ。

2)一般而言VCO和CP占噪声源的主导,但不要忽略refclk时钟上的噪声,因为refclk往往由外部芯片产生,噪声性能并不是很好(如Si5368),此外refclk上的噪声到输出端会放大N倍,N为反馈分频器的分频比,如果N很大,即使refclk上的噪声较好也不可忽略。

3)PLL的分类,环路稳定性、噪声建模,设计注意事项,片上电感的设计及仿真方法等专题会陆续展开。

-

怎样将相位噪声和抖动降至最低及其估算方法2009-10-13 3660

-

相位噪声的RMS抖动2018-10-10 8404

-

怎么将相位噪声转换为抖动?2019-08-13 5316

-

低相位噪声&抖动2020-06-10 3059

-

如何区分抖动和相位噪声?2021-03-11 1390

-

测量较低时钟频率的相位噪声和相位抖动2021-06-24 3728

-

时钟抖动(CLK)和相位噪声之间的转换2009-04-22 4870

-

MT-008: 将振荡器相位噪声转换为时间抖动2021-03-20 1169

-

将振荡器相位噪声转换为时间抖动2021-04-30 828

-

时钟抖动使随机抖动和相位噪声不再神秘2022-11-07 799

-

相噪是与哪种类型的抖动相对应?如何理解相位噪声与时间抖动的关系?2023-10-20 2434

-

相位噪声到抖动的转换(上)2023-10-30 4741

-

相位噪声与时间抖动有何关系?如何测试时间抖动?2024-01-31 2186

-

时钟抖动与相位噪声的关系2024-08-19 2683

-

相位、相位噪声与抖动:从原理到测量2025-08-15 4561

全部0条评论

快来发表一下你的评论吧 !