串并联阻抗的等效互换

电子说

描述

本期先补充学习一下本科课程中讲到的串并联阻抗的等效互换(虽然很简单,但重点是在工程中怎么用这个知识点),随后以LC-tank PLL中的电容阵列为例,介绍如何通过Spectre中的sp仿真,得到电容阵列的Y参数,并分离出等效并联电容(Cp)及并联电阻(Rp),进而精确评估LC振荡器的振荡频率。

**1. **串并联阻抗等效互换

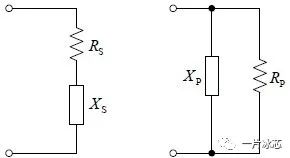

电阻R和电抗X的串并联形式如图1所示。

Fig1. 电阻R和电抗X的串联形式和并联形式

为了使电路在谐振频率附近能够相互等效,这两个电路的回路阻抗必须相等,即

上式中的虚部和实部分别相等,得

,

,

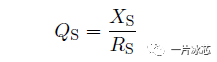

Xs与Xp的电抗特性保持不变,通常Xs和Xp都是电感或电容。考虑到串联电路的有效品质因子为

,

,

Rs与Rp的关系为

p与Xs的关系为

结论:串联电路转换为等效并联电路后,电抗Xp的性质与Xs相同,在Qs较高的情况下,其电抗X基本保持不变,而并联电路的电阻Rp比串联电路的电阻Rs增大了约Qs^2^倍。

**2. **应用背景

Xilinx在2018 ISSC会议上发表了一篇应用于RF-Data-Converter中的PLL,其10k~10MHz的积分噪声只有54fs,LC-VCO结构如图2所示。

Fig2. Xilinx 54fs PLL中的LC-VCO框图

Xilinx 54fs PLL Paper: A 7.4-to-14GHz PLL with 54fsrmsJitter in 16nm FinFET for Integrated RF-Data-Converter SoCs

电容阵列(Cap Array Unit)如图2所示,电容阵列权重为1:2:4:8:16:32。该电容阵列的好处是在Sel为低电平时使得M1管AB两点电位为高电平,保证M1管Drain Source到Psub的寄生Diode处于反偏状态,反偏时M1管的寄生电容较小,这样可以提高LC-VCO的振荡频率。

第三章介绍如何通过sp仿真得到电容阵列的Cp和Rp,进而准确算出LC-VCO的振荡频率。

3. Y参数仿真

在Cadence上搭建图2所示LC-VCO的电容阵列(近似),如图3所示:

Fig3. LC-VCO电容阵列

Y参数仿真的test bench如图4所示

Fig4. Y参数仿真test bench

sp仿真时Y参数或Z参数的表达式:

Y参数:Y(s)=1/Rp+X(s)

Z参数:Z(s)=Rs+1/X(s)

Cp公式:deriv((imag(ypm('sp 1 1)) / 2 / 3.1415926 ))

Rp公式:(1 / real(ypm('sp 1 1)))

Cs公式:deriv((1 / imag(zpm('sp 1 1)) / 2 / 3.1415926 ))

Rs公式:real(zpm('sp 1 1))

通过sp仿真,当V1等于1或0时可分别得到电容阵列的Rpon、Cpon和Rpoff、Cpoff(on代表开,off代表关),电容阵列后仿真结果如图5和图6所示

Fig5. 电容阵列Cpon和Rpon后仿结果

Fig6. 电容阵列Cpoff和Rpoff后仿结果

注:LC-VCO通常关心电感、可变电容、电容阵列的等效Rp和Cp而不是Rs和Cs,这样方便计算振荡频率,Rp往往会限制振荡器起振,Cp往往决定振荡频率,设计时应仔细考虑。

-

串、并联阻抗等效互换与抽头变换2011-04-13 1138

-

三极管等效、互换、自锁电路分享2023-02-02 4985

-

互感电感的串并联计算方法2023-03-03 34085

-

电阻串并联电路原理分析简述2011-09-26 5169

-

锂电池的等效阻抗及测量方法2018-01-29 12182

-

阻抗变换是不是等效变换?2018-10-16 3204

-

怎样去计算有互感电感串并联的等效电感2021-08-31 10458

-

RC串并联选频网络振荡电路2008-06-23 14726

-

串并联谐振电路的特性2010-02-06 3889

-

无源RLC网络和阻抗匹配(清华大学)2011-03-18 2104

-

串并联电路中的等效电阻计算公式2018-01-16 7008

-

串联、并联,还是串并联……LED连接和驱动方式如何选?2019-07-02 23578

-

串并联电路的标准画法2023-03-09 7175

-

LED灯串并联电阻的选择2023-05-01 8721

-

电容器的串并联特点2023-11-13 4867

全部0条评论

快来发表一下你的评论吧 !