如何做一个低抖动的PLL?PLL噪声优化

电子说

描述

1. RFSoC

Xilinx最新一代UltraScale+ FPGA ^[1]^ 将RF AD/DA、SerDes等系统完美集成在一颗芯片打造出了一个全方位的通信链,其中RFSoC可以支持5G无线网络,电缆访问远程物理节点和电子战/雷达系统,还可以应用于测试和测量,卫星通信,军用无线通等。

该RFSoC具有如下特性:

8个4GSPS 或16个2GSPS 12位ADC;

8-16个6.4GSPS 14位DAC。

RFSoC输入频率达到GHz且位数大于12位,架构上采时钟直接采样的方式,采样后的数据送到数字进行处理,这对采样时钟噪声性能提出了非常高的要求。2018年Xilinx发表在ISSCC会议上的关于PLL的paper ^[2]^ 正是应用于该RFSoC。

该PLL在6.25GHz频率下的RMS Jitter为54fs @ 10k~10MHz积分区间。论文核心内容仅有不到一面A4纸,每句话都值得我们细细品味。下面章节将结合该论文逐一展开PLL的噪声优化技术。

2. Xilinx****噪声优化技术

**2.1 PLL **参数

参考频率:500MHz;输出频率:7.414GHz;6.25GHz RMS Jitter:54fs @ 10kHz10MHz积分区间;工艺:16nm FinFET;功耗:45mW @ 12.5GHz;面积:0.35 mm^2^。

**2.2 **带内噪声的优化

PLL参考频率为500MHz,带宽可以做的很高,原则上50MHz以内都合理,但带宽过高对带内噪声是不利的,过低对VCO噪声不利,折中考虑,我个人猜测带宽应该在5~10MHz左右。文中也提到高带宽下要想做低噪声,带内噪声(如PFD/CP/FBCLK/REFCLK)必须要很低。

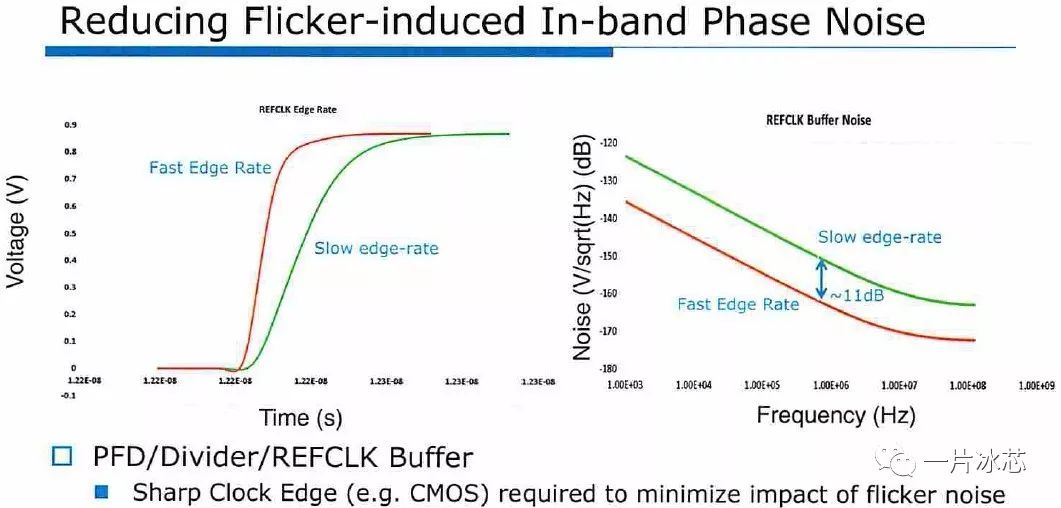

噪声来自电平翻转的不确定性,在阈值电压附近,停留的时间越短噪声越小。因此为了降低PFD和DIVIDER等CMOS电路的Jitter,需要尽量把上升/下降沿做shaper,如小于10ps;PFD消死区时间小于40ps。

Xilinx在2019年ISSCC上的报告 ^[3]^ 指出CMOS电路边沿做Sharp后噪声优化了11dB,如图1所示。

Fig1. 边沿sharp后对带内噪声的影响

2.3 CP****的噪声优化

CP电路输出级采用18个slices并联的方式,实现了大电流且电流可调,大的动态范围,降低了噪声;自偏置电流源使up/dn电流失配小于1%;CP镜像电流源尺寸为输出级slices的4倍,保证了较好的matching和jitter;PMOS电流镜栅源增加RC滤波,减小了输出噪声;输出级增加单位增益放大器,减小了动态电流失配;上下电流源采用stack结构提高了输出阻抗并降低了噪声。

2.4 LPF****的噪声优化

电阻热噪声与阻值成正比,因此在保证环路稳定的前提下滤波电阻应尽量小;电容漏电会引入spur,为减小漏电滤波电容采用MOM电容。

**2.5 **基准源的优化

LDO参考电压来自bandgap,为了减小bandgap和LDO本身引入的噪声,通路上增加了两个大的RC滤波,其中LDO功率管栅端滤波电阻(为减小面积该电阻由亚阈值管实现)高达几M Ohm,带宽小于10kHz。

2.6 LCVCO****的优化

16nm FinFET工艺中PMOS管的flicker noise远大于NMOS,为减小噪声,LCVCO有源器件采用全NMOS实现,与CP电路类似采用了stack结构,提高了输出阻抗,进一步减小了噪声。

电容阵列由MOM电容,一个NMOS开关(M1),两个stack结构的NMOS pull devices和一个反相器组成,如图2所示。该结构可保证电容阵列在on状态下A,B点拉低,off状态下A,B点拉高,提高了on/off状态下电容阵列的Q值,优化了LCVCO相位噪声。

温度补偿电压Vte经RC滤波接到varactor电容,减小了噪声,其中Vte具有正温度系数,用于补偿LCVCO高温下频带的下移。

电感的Q值越大,相位噪声越好,一般电感的Q值在13左右,这里电感Q 值要求大于17,有可能采用平面螺旋结构,因为平面螺旋结构Q值一般大于堆叠结构。电容阵列的引入,可使得tuningvaractor电容变小,提高了LCVCO的相位噪声。

Fig2. LCVCO及LDO电路

**2.7 **电源和地的隔离

前面介绍为了提高数字电路噪声性能,将数字边沿做的更shape,使得模拟电路更易受到干扰,电路设计时CP,LPF,VCO中的NMOS采用deepnwell器件,电源也要与数字电源分开,这三个模块采用LDO供电,这样模拟、数字电源和地完全隔离,减小模拟、数字电路衬底和电源的相互干扰。

2.8 layout****布局

电容阵列采用图2所示带有二进制权重且上下对称的局部布局方式;电感线圈周边插入电源到地的decap电容且LCVCO远离数字模块的整体布局方式。

**3. **其他噪声优化技术

文献[4]和[5]分别为Xilinx和Samsung近两年发表的paper,文献[4]给出的Sampling Phase Detector(SPD) PLL结构如图3所示。引入SPD前后测试结果如图4所示,可见采用SPD技术PLL在9GHz和18GHz频点下RMS Jitter分别提高了200fs和230fs @ 1kHz~100MHz积分区间。

Fig3. SPD PLL结构

Fig4. 引入SPD前后测试结果 @ 9GHz, 18GHz

文献[5]采用Digital-to-Time Convert(DTC)-basedsampling analog pll结构,该结构同样也采用了SPD技术,除此以外Samsung还采用了DTC增益校准,DCC校准,reference clock doubler,LMS算法,Sigma-Delta等技术,在6.33GHz频率下将 RMS Jitter做到了75fs @ 10kHz~10MHz积分区间,该PLL可用于最新的5G蜂窝移动通信。

Fig5. DTC-basedfractional-N pll

-

Texas Instruments PLL1707和PLL1708:低抖动多时钟发生器的卓越之选2026-02-10 389

-

德州仪器PLL1707和PLL1708:低抖动多时钟发生器的卓越之选2026-02-04 217

-

锁相环PLL的噪声分析与优化 锁相环PLL与相位噪声的关系2024-11-06 4875

-

PLL抖动对GSPS ADC SNR及性能优化的影响2024-09-20 475

-

如何评估分布式PLL系统的相位噪声?2023-11-06 1682

-

评估低抖动PLL时钟发生器的电源噪声抑制2023-03-08 2448

-

具有时钟分配的1.4GHz低相位噪声和低抖动PLL的演示板DC1795A2019-02-25 3228

-

PLL抖动及其对ECAN™技术通信的影响2018-04-24 1175

-

模拟PLL,模拟PLL是什么意思2010-03-23 2849

-

MAX3625B 抖动仅为0.36ps的PLL时钟发生器2010-03-01 1675

-

评估低抖动PLL时钟发生器的电源噪声抑制性能2009-09-18 1913

全部0条评论

快来发表一下你的评论吧 !