前端工程师应该知道的一些layout技能

电子说

描述

**1. **模拟与数字

数字电路中,可能会有上万个互联的反相器,而在模拟电路中却看不到上万个放大器。数字电路主要是优化芯片的尺寸、密度、时序,模拟电路主要目标不是芯片的尺寸,而是电路的性能、匹配程度、速度等。当然,模拟电路在某种程度上面积仍然是一个问题,但不再是压倒一切的问题,性能比尺寸更重要。

对于数字项目,到了一定程度,你可以躲到一个小房间去设计版图。然而,模拟项目中,需要后端工程师与电路设计者不断地交换意见,确保在所能选用的各种方案中,你的电路能达到最优性能 。

**2. **衬底耦合

现代CMOS工艺大都采用重掺杂的p+衬底来减小闩锁效应,但是,衬底的低电阻率会在电路中不同器件之间建立有害通路。所谓的“衬底耦合”效应已经成为当今混合信号IC的一个严重问题 。

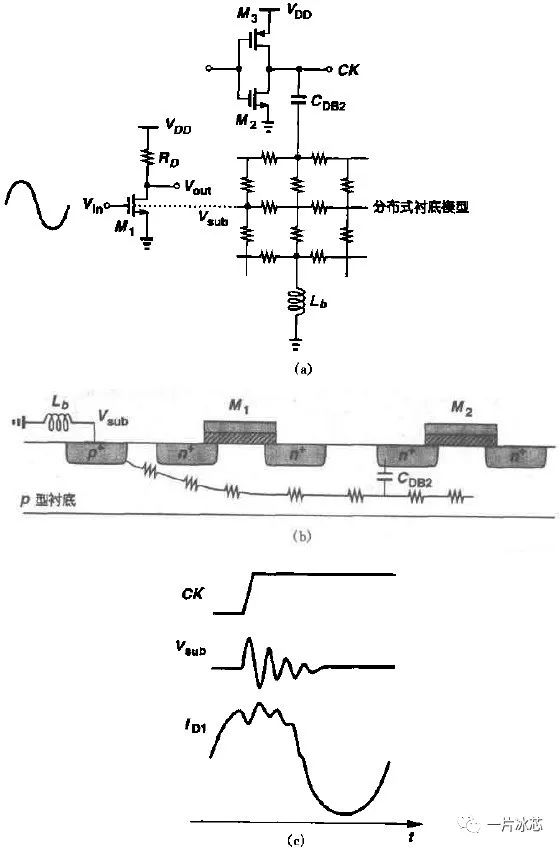

衬底耦合现象如图1所示,(a)为包含衬底耦合的混合信号电路,(b)为器件的剖面图,(c)为信号波形图。M1的漏电流取决于V in -V TH1 ,VTH1随衬底电压的变化而变化,因此CK的每次跃变都影响了模拟输出。

Fig1. 衬底耦合现象

为减小衬底耦合影响,可采用差分走线、增加保护环、阱隔离、拉大模拟数字模块距离、增加decap电容、划分电源和地平面等方法,具体方法见第3章。

**3. **常见问题

3.1 LDO IR Drop****问题

最近用某22nm工艺做了一个LDO,原理图及layout如图2所示,原理图标注的颜色与layout布局标注的颜色对应。ldo_out前仿值为950mV@ tt corner,后仿(网表为r+c+cc)发现掉到了900mV,那么是什么原因造成了这50mV的压降呢?为了解释这个问题我做了以下工作。

Fig2. LDO原理图及layout布局

首先我抽了一个c+cc的网表,仿真发现ldo_out也为950mV,说明是r的问题。这是底层功能模块,顶层电源网络还不够完整,因此我首先怀疑的是电源或地上的IR Drop,在r+c+cc的后仿网表中电源和地都呈分布式,我打出所有电源和地的波形,没有发现大的IR Drop,排除了电源地的问题。

我第二个怀疑的就是vref,因为vref是基准源过来的电压,距离LDO较远(近1000um),如果有小的IR Drop也会放大R2/R3+1倍到输出。查找layout中vref label的位置发现打在了图2右侧黑色实线的顶端,而EA输入端在黑色实线底端,黑色实线采用M6层金属,宽度为1um,长度为392um。

查找工艺文档发现各金属线的方块电阻如表1所示,可算出黑色实线的电阻为196Ω,R4=3.4kΩ,R2/R3=0.4,可得M6 IR Drop会导致ldo_out下降50mV,与仿真结果一致。实际layout中vref会加入电阻率较低的M9与M6并联且M9的宽度为4um,这样会解决IR Drop。将vref的lable移到靠近EA的输入端,再次仿真发现电压正常。

表1 各层金属线的方块电阻

3.2 LCVCO****电容阵列布局

图3给出了4种LCVCO电容阵列的布局,那么哪种布局比较合理呢?要回答这个问题,首先要知道电感与线圈面积成正比,即面积越大,磁通量越大,因此电感臂不同抽头处的感值不同(通过EM软件可以验证)。图中Ctrl<4:0>是用于控制电容阵列的开关,图3(d)多了一个译码电路,电容阵列开启个数均带有二进制权重。图3(b)和(c)区别在于小电容(Ctrl<0>控制端)在电感线圈远端还是近端,当电感较小时(如小于400pH),图3(b)的布局方式不合理,因为此时电感线圈到Ctrl<0>的距离最远,当只有Ctrl<0>打开时,电感最大,会减小频率覆盖范围,正如图3(c)的布局方式在参考文献[3]中可以提高频率覆盖范围(最大提高了46%)一样。

此外,图3(b)的布局方式由于小电容阵列Rs较大,等效Rp较小(相对大电容阵列),更容易引起起振问题。图3(c)和(d)区别不大,实际布局中图3(a)、(c)、(d)都有可能用到,但很少用图3(b)的布局方式,参考文献[4]就采用图3(a)所示的中心对称结构。

(a) (b) (c) (d)

Fig3 LCVCO电容阵列布局

**3.3 **隔离

**3.3.1 **电源地的隔离

图4给出了常见模数混合电路layout布局方式,模拟和数字电源往往要分开供电,即使无法分开也不要用底层金属互联,最好用顶层金属或PAD以starrouting^[5]^的方式连接,正如图4中的地线一样。对于噪声要求比较高的模拟电路NMOS需要用deep-nwell(图中绿线)与衬底隔离。

Fig4. 模数混合电路layout布局方式

3.3.2电容与shield****隔离

图5给出了电感的layout示意图 ^[6]^ ,电感往往出现在性能要求比较高的电路中,为了减小衬底干扰及涡流需要在电感下方加入shield,shield一般用M1或poly层实现。电感周边插满decap电容,用于减小数字模块的干扰。

Fig5. 电感隔离

3.4****邻近效应

要保证所有导线都远离电感,因为靠近电感的导线会影响电感量,电路设计人员的精妙设计可能会被这些导线破坏。许多经验法则指出了导线离电感的最小距离,有一些设计者认为要保证这个距离有5倍线宽 ^[7]^ ,如图6所示。

Fig6. 导线和电感距离

图7给出的SerDes架构中包含两个PLL,文献[8]指出两个PLL至少间隔100um,中间区域要填满decap电容并用guard ring隔离且不允许有任何数字电路,如PFD、CP等。

Fig7. SerDes架构

4.常用快捷键

·Shift+x(X)进入下一级视图 ·Shift+b(B)返回上一级视图

·Ctrl+f显示上层等级 ·Shift+f显示所有等级

·Shift+m(M)合并工具 ·Shift+k(K)清除所有标尺

·k标尺工具 ·Shift+s(S)查找/替换

·t查看版图尺层次 ·r绘制矩形

·s拉伸工具 ·o进插入过孔

-

硬件工程师跟layout工程师有什么区别?2011-10-20 31622

-

电子工程师的八大技能2014-10-25 3876

-

小程序来临,前端工程师的春天2016-09-28 3233

-

EMC工程师需要具备哪些技能?2019-05-30 2701

-

嵌入式工程师需要哪些关键技能呢2021-11-08 1798

-

电源工程师需要哪些知识2021-11-11 2242

-

FPGA工程师需要具备哪些技能?2023-11-09 2458

-

pcb layout工程师应该熟悉的几种模块2012-06-25 2748

-

硬件工程师应该知道的音频功放电路2017-11-27 1892

-

前端工程师的未来在哪2018-09-07 2946

-

一位前端工程师对前端的理解2018-09-25 4870

-

前端工程师的简历怎么写2018-10-09 17247

-

web前端工程师需要掌握的基础知识和技能2019-09-25 6052

-

一个优秀电子工程师必备的技能2020-08-07 8386

-

IC前端设计工程师2021-11-05 644

全部0条评论

快来发表一下你的评论吧 !