DC启动环境综合设置及实操

编程语言及工具

描述

启动环境设置

在启动DC之前,首先要配置DC启动环境,指定工艺库和综合库。

DC的启动配置文件.synopsys_dc.setup,配置了DC启动过程中要执行的库等信息。

.synopsys_dc.setup,这个文件名不能更改,必须是.synopsys_dc.setup,这个文件存在于3个位置:

synopsys的安装目录下,基本不需要动这个文件;$SYNOPSYS/admin/setup(/opt/Synopsys/dc/admin/setup/.synopsys_dc.setup)

用户目录下,基本不需要动这个文件;~user(/home/IC/.synopsys_dc.setup)

当前工作目录下,(/home/IC/dc/DC_work/work/.synopsys_dc.setup)

配置DC的启动环境,就是在启动的目录创建.synopsys_dc.setup文件并进行修改。

当启动DC时,首先会在当前启动位置寻找.synopsys_dc.setup文件并加载,如果没有找到则回到当前用户主目录下寻找,若还没有找到则加载DC安装路径下的.synopsys_dc.setup。

新建并修改.synopsys_dc.setup文件:

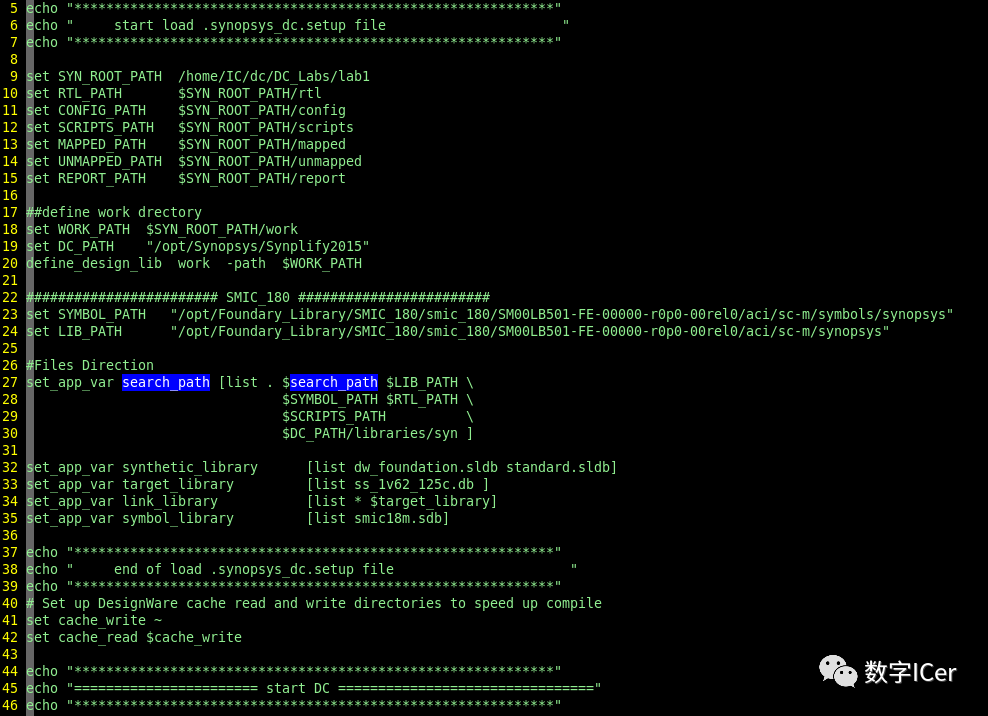

.synopsys_dc.setup

其中:

设置工程路径

DC运行时的工作路径(WORK_PATH);

DC软件安装路径(DC_PATH);

指定设计和库的工作路径:define_design_lib work -path $WORK_PATH

指定四个相关库路径:

链接工艺库(link library):链接库是target_library一样的单元库或者IP核。

*号表示开辟一块单独的内存空间给DC使用;

目标工艺库(target library):DC将RTL级的HDL描述映射到实际的门级电路时所需要的标准单元库。是工艺厂商提供的工艺库。

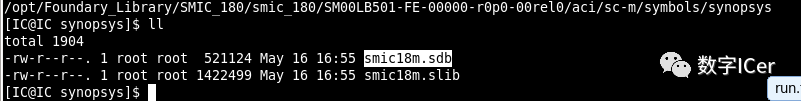

图形化符号库(symbol_library)(SYMBOL_PATH):指定符号库的路径,关联图形化库,使用GUI界面的时候,可以看到综合得到的门级网表的图形化界面。

文件位置:工艺库SMIC_180下

/opt/Foundary_Library/SMIC_180/smic_180/SM00LB501-FE-00000-r0p0-00rel0/aci/sc-m/symbols/synopsys

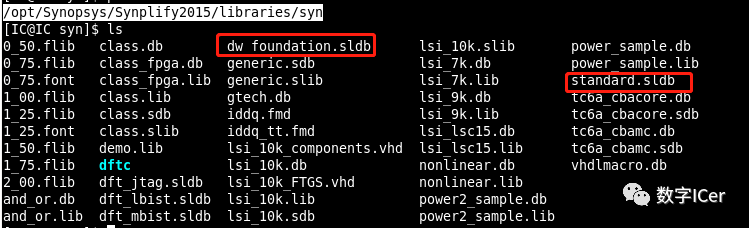

综合库(synthetic_library) :也叫IP库,synopsys做映射自带的库:DesignWare library优化算术器件DW_ foundation.sldb和标准单元库standard.sldb;

文件位置:dc安装目录下

/opt/Synopsys/Synplify2015/libraries/syn

上面的库设置仅仅适用于逻辑综合,也就是非拓扑模式下的综合;

拓扑模式下,需要用到物理库,或者相关的物理布局等信息;

create_mw_lib :主要使用DC的物理综合的时候,需要生成物理库;

set与set_app_var区别:

set: 自己自定义的一些变量;

set_app_var :定义DC内部的系统变量等,如果不是合法的名字set_app_var会报错。

主要指定有:search_path、synthetic_library、target_library、link_library、symbol_library 以及其他的一些命令开关等。

DC启动的三种方式

1、design_vision(GUI)

design_vision &

design_vision -topographical_mode &

使用拓扑结构启动时必须提供相关的物理约束和物理库;

2、dc_shell(shell)

dc_shell | tee -i run.log

3、batch mode

前面两种方式只是将DC启动起来,还没有开始工作,需要通过source命令把脚本写进去以后DC读取才开始工作。

而这种批处理模式,在启动的同时,DC执行run.tcl脚本即可工作,其中包括约束要求等:

dc_shell -topo -f run.tcl | tee -i run.log

-topo 使用拓扑模式启动DC,启动的同时执行run.tcl脚本,并且把启动过程显示在终端并打印到run.log中。

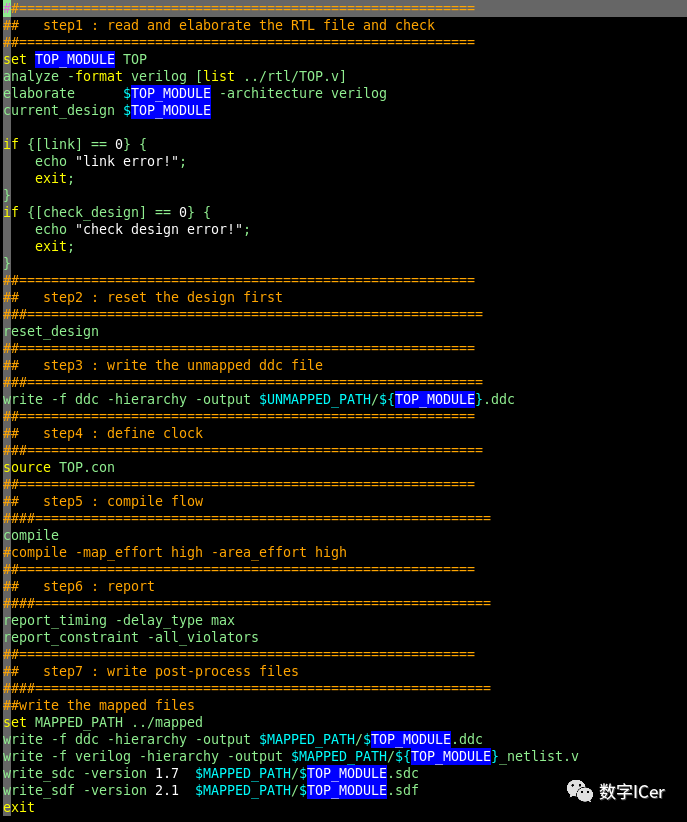

综合流程实操

DC综合流程:

1.准备好文件

2.启动DC

3.读入设计前的检查

4.读入设计和查看设计及库

5.约束设计

6.综合

7.综合后检查与优化

8.保存优化后的设计

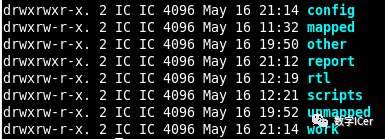

工程目录:

config: DC的配置文件

rtl:rtl代码

scripts:脚本

unmapped:DC转换后的GTECH文件或unmapped.ddc文件

mapped:编译后的网表文件

report: 综合后的报告

work:运行DC的工作夹

启动DC和检查库

1.启动DC

dc_shell | tee -i run.log

可以看到log位置,说明库加载ok:

start load .synopsys_dc.setup file end of load .synopsys_dc.setup file

2.读入设计前检查:

查看设置的库文件:

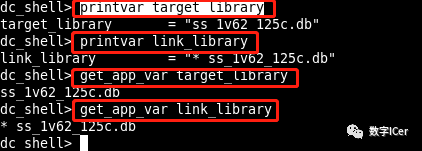

printvar target_library printvar link_library 或者 get_app_var target_library get_app_var link_library

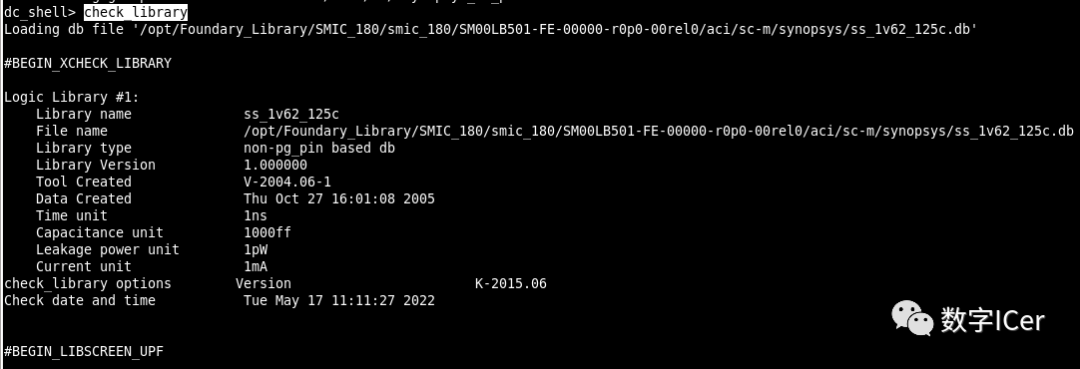

检查逻辑库信息:

check_library

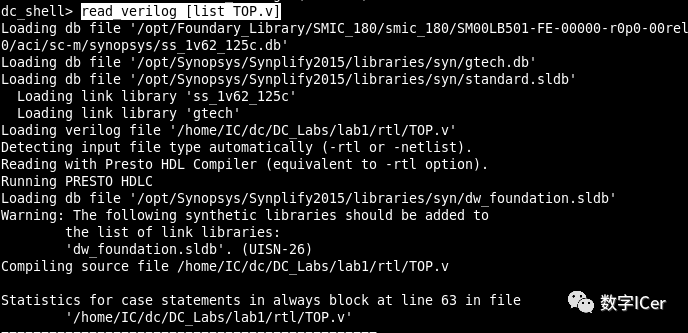

3.读入设计文件:

read_verlog [list TOP.v] 或者 read_vhdl [list TOP.vhd]

或者

analyze -format verilog [list TOP.v] //读入设计 elaborate -architecture verilog TOP //设置顶层

dc会自己寻找库文件和rtl文件:

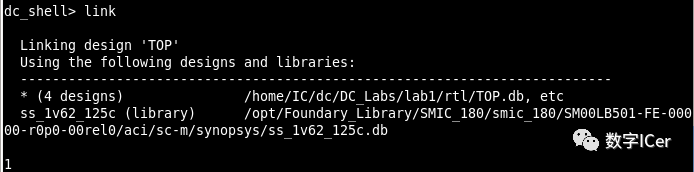

执行链接命令:查看当前要综合的设计是否缺少子模块

link

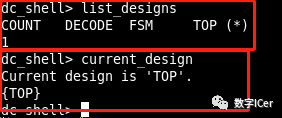

查看设计文件,*代表当前设计顶层 :

list_designs

显示当前设计顶层 :

current_design

更改当前设计顶层:

current_design COUNT

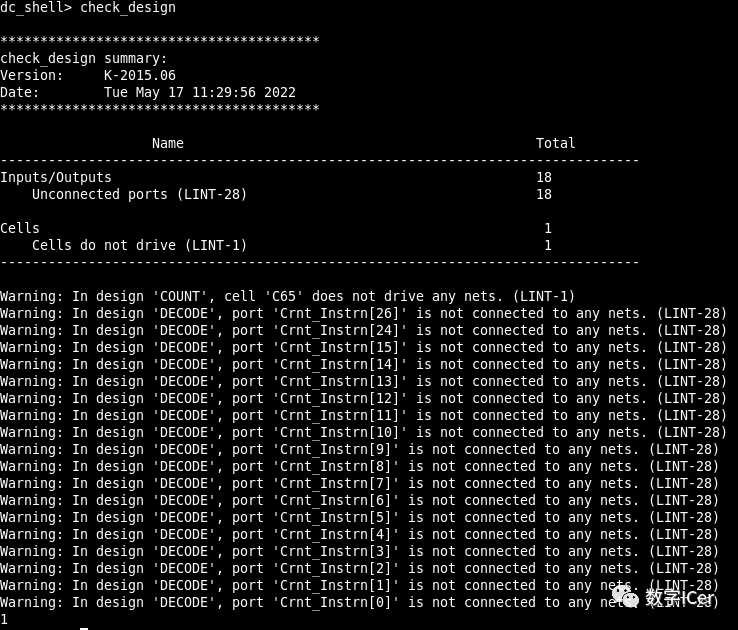

检查设计:如果返回0,表明当前设计存在问题,无法综合;

check_design

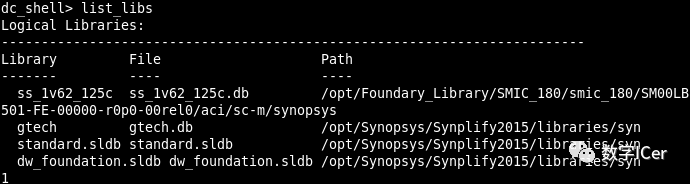

4.检查库

查看工艺库和synopsys库文件:

list_libs

查看库内容(需要安装Library Compiler):

report_lib ss_1v62_125c

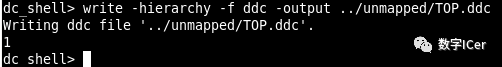

5.以ddc的格式保存未映射的设计:

write -hierarchy -format ddc -output ../unmapped/TOP.ddc

其他:查看命令解释:

man set_app_var set_app_var -help

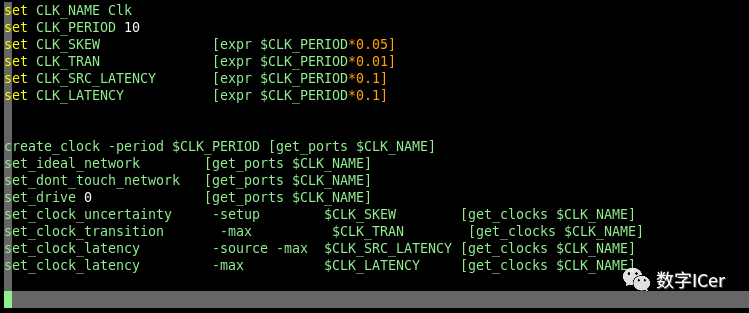

设置约束

source TOP.con

检查时序:检查有无路径没有约束

check_timing

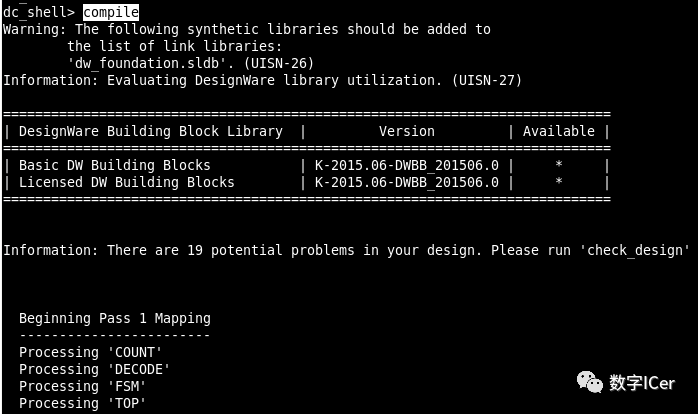

综合

compile

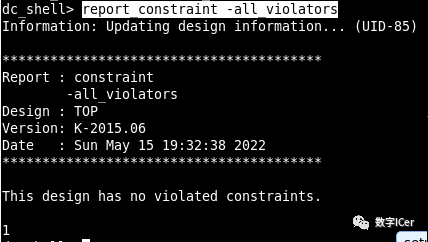

综合后,进行检查约束是否违例:

report_constraint -all_violators

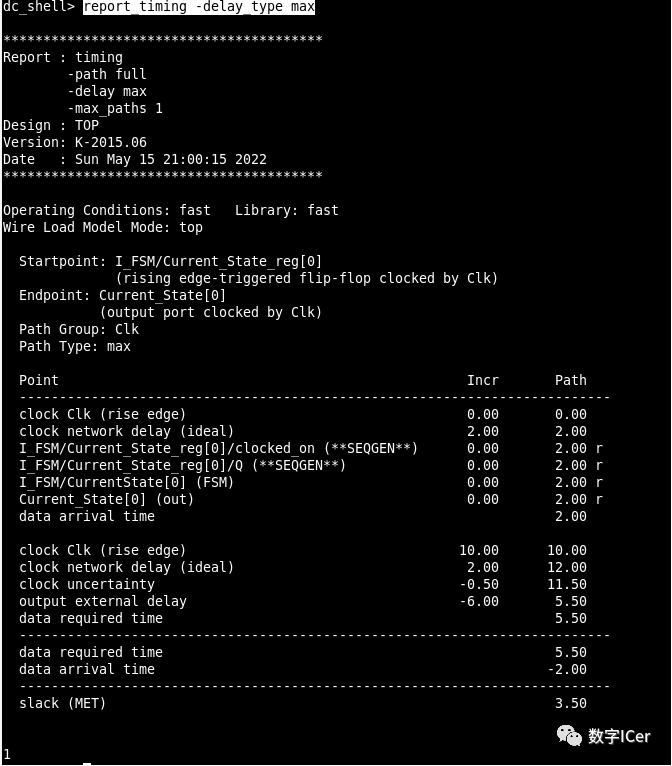

查看最差路径时序

report_timing -delay_type max

保存综合后的设计

保存网表:

write -format verilog -output ../mapped/TOP_netlist.v

以ddc的格式保存综合后的设计:

write -hierarchy -format ddc -output ../mapped/TOP.ddc

DC脚本运行

dc_shell -f ../scripts/run_1.tcl | tee -i run.log

编辑:黄飞

-

【AWorks试用体验】EasyARM-i.MX283A入门实操之Windows环境串口登录2015-08-10 7353

-

一种工业机器人综合教学实训平台2021-07-01 1992

-

机电技术综合实训系统分享2021-07-02 1230

-

无线路由器设置实操步骤详解2019-06-24 4711

全部0条评论

快来发表一下你的评论吧 !