Sigma-Delta小数分频PLL中的分频器该怎么做?

电子说

描述

**1 **分频器结构及原理

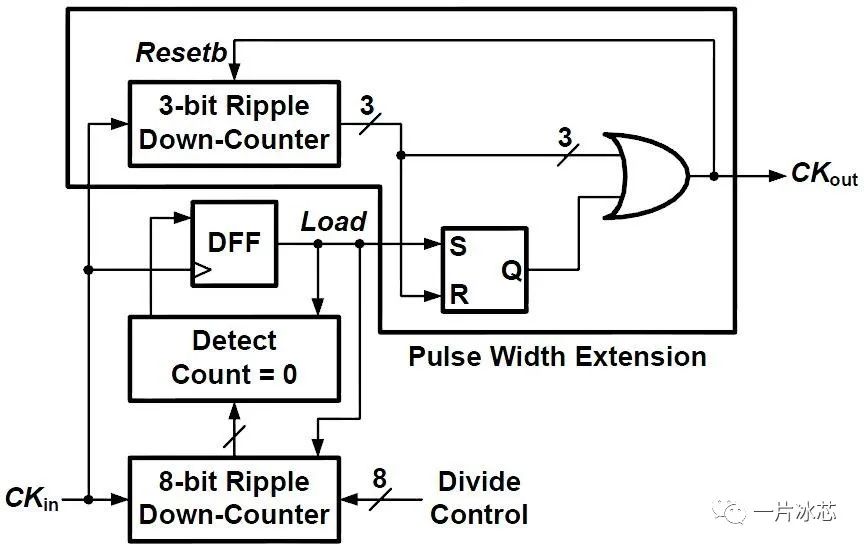

文献给出的分频器结构如图1所示。该分频器最高输入频率(f in )为16.3GHz,也就是一个周期只有(T in ,T in = 1/ f in )61.3ps。为了避免后级PFD无法分辨如此小的脉宽,线路中增加了脉宽拓展电路,通过3-bit Ripple Down-Counter将最小脉宽拓展了8倍。

8 bit分频比控制字(N)通过控制8-bit Ripple Down-Counter使分频器从16-257连续整数分频。总的分频比为N+2。

Fig1. PLL Divider

图1中的DFF应包含一个外部复位信号,用于保证DFF初始输出(图1中的Load)为高电平。

初始Load为高电平时,8-bit Ripple Down-Counter将8bit分频比控制字(图1中Divide Control, N)上的每bit配置(1或0)Load到8-bit Ripple Down-Counter DFF的输出端,第一个CKin上升沿(或下降沿)到来时Load变为0,直到8个DFF输出全部清零,Load信号再次置高,如此反复,实现N分频。

每个DFF输出(dq)与输入(di)相连实现二分频,最终实现N+2分频,如要实现257分频时,配置N=8'b11111111即可。

**2 **电路实现

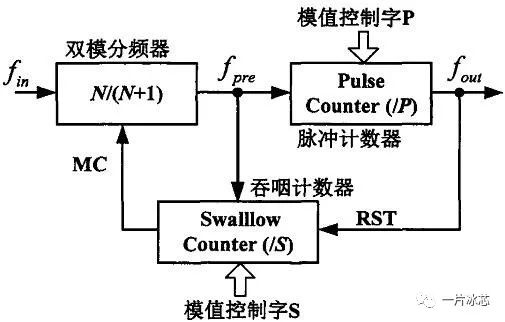

图1中的Ripple Down-Counter可参考脉冲吞咽计数器中的脉冲计数器或吞咽计数器 ^[3-5]^ ,如图2所示。只需要8个DFF级联并加上一些逻辑门就可实现,有这方面需求的人,最好亲自试一下,这里不再给出具体做法,要提醒的是计数器里的DFF最好用差分结构。

Fig2. 基于脉冲呑咽计数器结构的可编程分频器

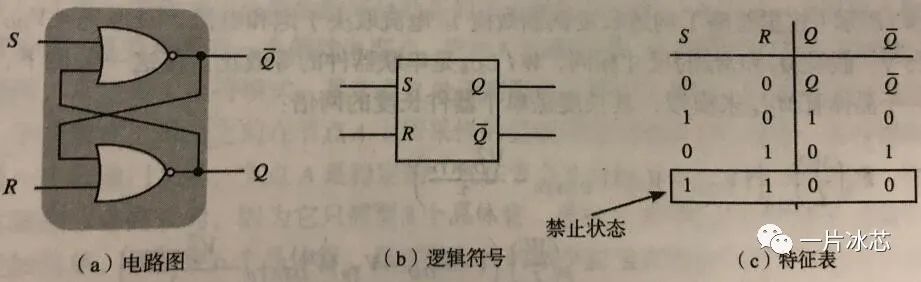

图1中的SR Latch可由图3实现。

Fig3. SR Latch的电路、符号图及真值表

**3 **仿真结果

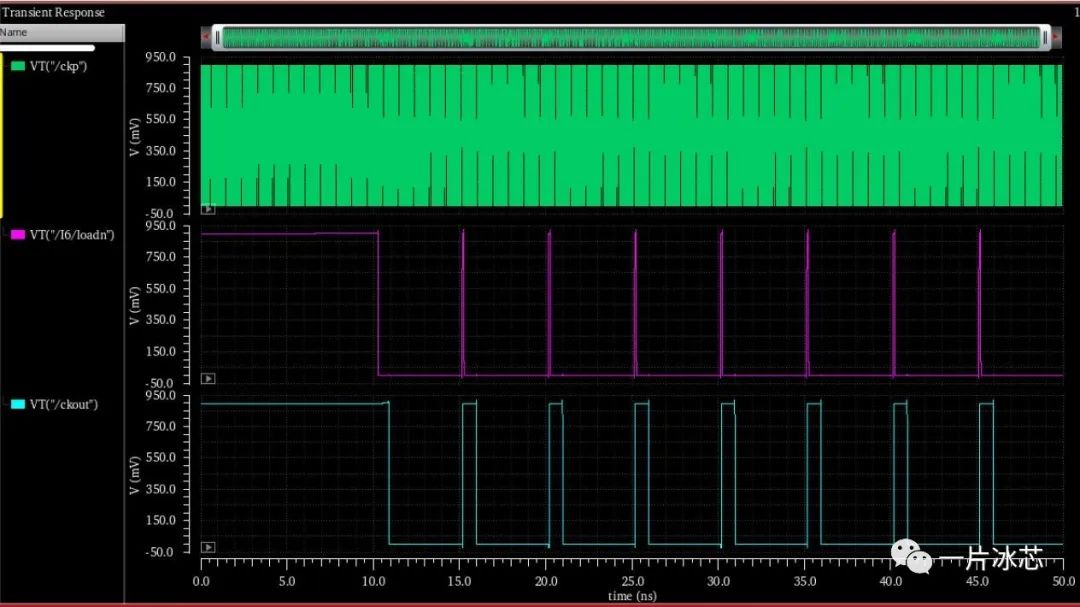

图4给出了输入频率为10GHz,分频比控制字N=00110000时的仿真结果。从上到下依次为输入时钟、拓展脉宽之前的输出信号及8倍脉宽拓展后的输出信号。图中ckp频率为10GHz,loadn为200MHz,脉宽为100ps,ckout为200MHz,脉宽为800ps。

Fig4. 分频器仿真结果

**4 **思考与讨论

图1中的脉宽展宽电路,为什么用时序电路实现,用组合逻辑也可以实现,两者有什么区别?用组合逻辑如何实现?工业上实用吗?

利用这个分频器如何实现小数分频呢?小数分频为何要引入Sigma-Delta?噪声整形的原理是什么?

-

Shanguc

2024-01-10

0 回复 举报请问是哪篇文献呢? 收起回复

Shanguc

2024-01-10

0 回复 举报请问是哪篇文献呢? 收起回复

-

锁相环整数分频和小数分频的区别是什么?2024-01-31 5369

-

FPGA学习-分频器设计2023-11-03 3257

-

分频器之小数分频设计2023-06-05 2512

-

偶数分频、奇数分频、半整数分频和小数分频详解2023-03-29 6809

-

偶数分频器的设计2023-03-23 3000

-

怎么把小数分频控制字与整数分频控制字结合起来去控制可编程分频器?2021-06-24 1037

-

基于FPGA的小数分频器如何去实现?2021-04-29 1499

-

如何使用FPGA进行任意小数分频器的设计2019-08-02 2969

-

分频器的作用是什么 半整数分频器原理图分析2019-02-01 18909

-

△∑小数频率合成器中的小数分频器设计2016-05-24 654

-

FPGA实现小数分频器2011-11-29 819

-

小数分频锁相环的工作原理2010-05-28 1323

-

任意分频系数小数分频器相关文档及源代码2009-08-03 696

全部0条评论

快来发表一下你的评论吧 !