一种基于Transformer结构的VCO介绍

电子说

描述

1 VCO需要注意什么

常规LCVCO由电感、电容、负阻、偏置组成,每个模块有很多种实现方式,下面给介绍一下各模块设计时的注意事项。

1.1 电感

电感有平面螺旋结构和堆叠结构。主要技术指标有品质因子(Q)、自谐振频率(F)、感值(L)。电感下面要加shielding,两侧要加isolation wall以提高Q值。Q值的提高主要从增大感值和减小串联电阻角度考虑,F值的提高主要从减小寄生电容角度考虑,L值可以从结构、线圈匝数角度考虑。

1.2 电容

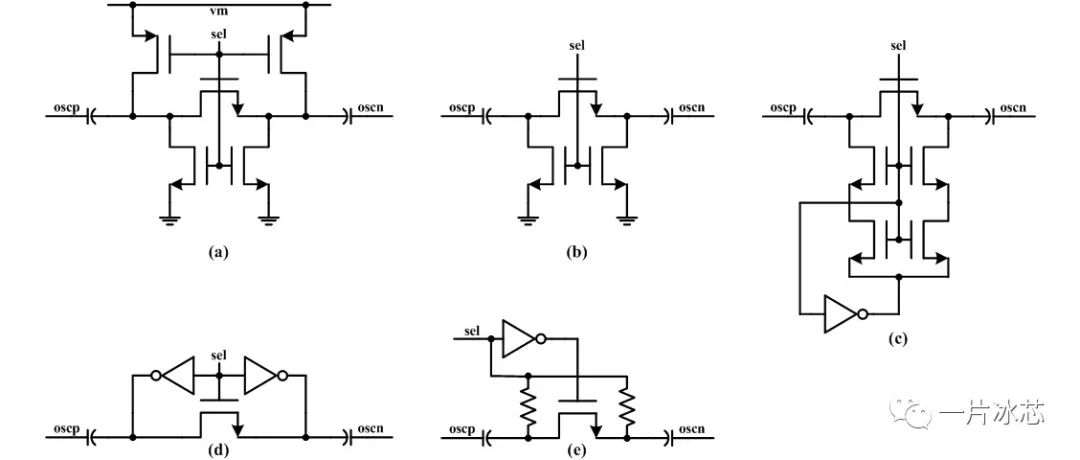

LCVCO通常需要电容阵列和varactor电容来实现较大的频率覆盖范围,电容阵列和varactor电容的尺寸、结构也有很多需要考虑的地方。图1给出了几种实用的单开关电容阵列结构,限于篇幅不再介绍每种结构的优缺点。

Fig1. 单开关电容阵列结构

1.3 负阻

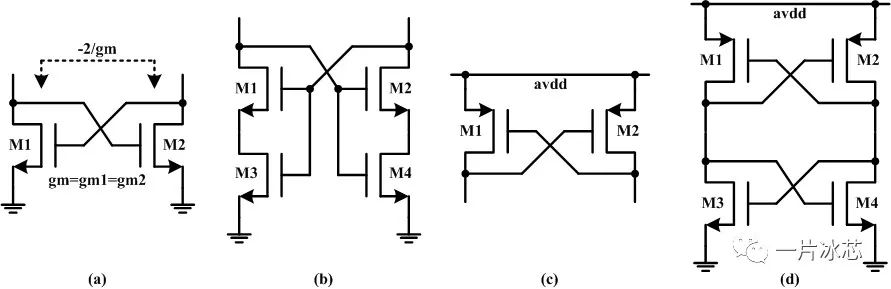

负阻有nmos-only(a), nmos-stack(b), pmos-only(c), cmos(d),结构,如图2所示,其中nmos-only适用于高频,cmos结构适用于低功耗。

Fig2. 常见负阻结构

1.4 偏置

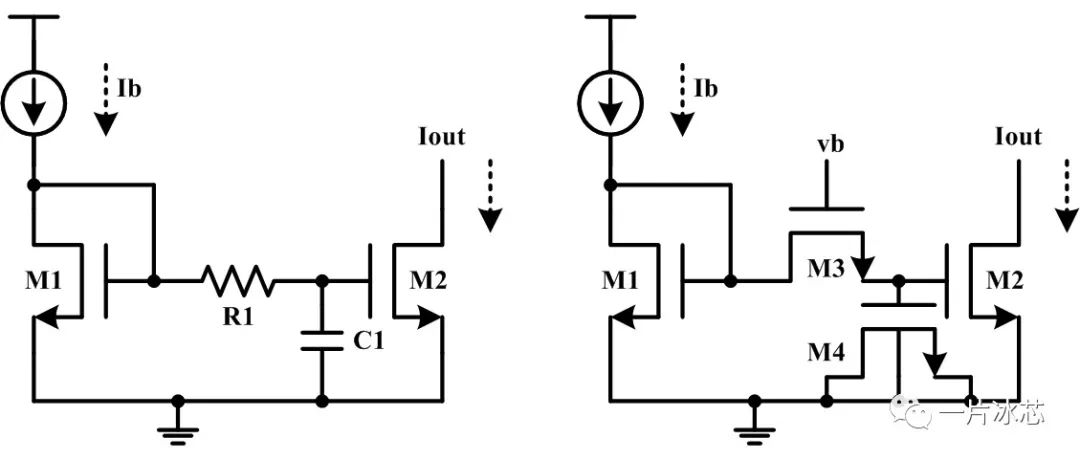

偏置电路需要滤波滤除来自基准、耦合及本身的噪声,图3所示为两种不同结构的偏置噪声滤波器,R1(倒比管M3)和C1(M4)的时间常数决定噪声带宽,噪声带宽至少要小于PLL环路带宽,因为PLL可以抑制VCO的带内噪声。

相同RC时间常数下,右侧结构消耗更小的面积。相同RC常数下,当M3等效电阻较大,M4等效电容较小时消耗面积最小。当截止频率为5kHz(R1=1MΩ,C1=30pF)时偏置建立时间需要200us,这会严重影响PLL的锁定时间。为减小面积,M4采用MOS电容并在上面叠MOM电容的方式。

Fig3. 不同结构的偏置滤波器

1.5 常见LCVCO结构

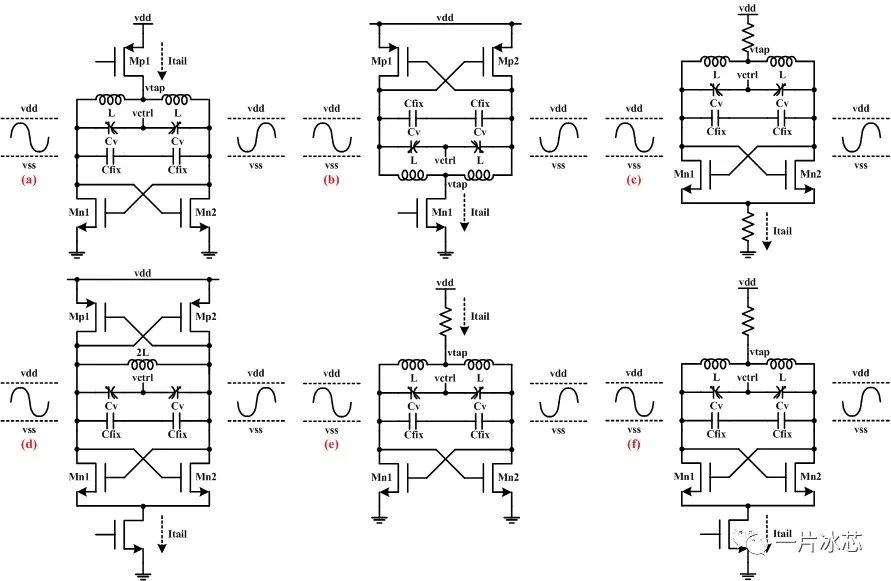

由电感、电容、负阻、偏置的不同组合可得到图4所示不同结构的LCVCO,同样限于篇幅不再介绍每种结构的优缺点。

Fig4. 常见LCVCO结构

2****Transformerbased VCO

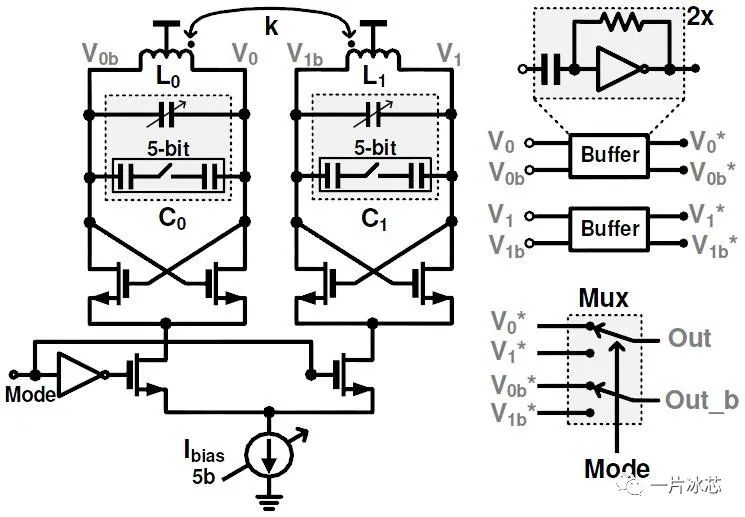

图5给出了一种Transformer based VCO^[1]^,该结构中的电容、负阻、偏置跟第一章的结构类似,主要区别是将第一章中的电感换成了变压器。合理设置C0和C1的比值(1.8)及模式0/1的选择可覆盖7~18.3GHz,18.3GHz的相位噪声为-100dBc/Hz @ 1MHz。

该结构将开关串联在负阻管交流地,避免让电感串联一个电阻,提高了电感的Q值。输出通过AC-coupled self-biased inverter结构减小DC失调的同时实现满摆幅放大。

Fig5. Transformer based VCO

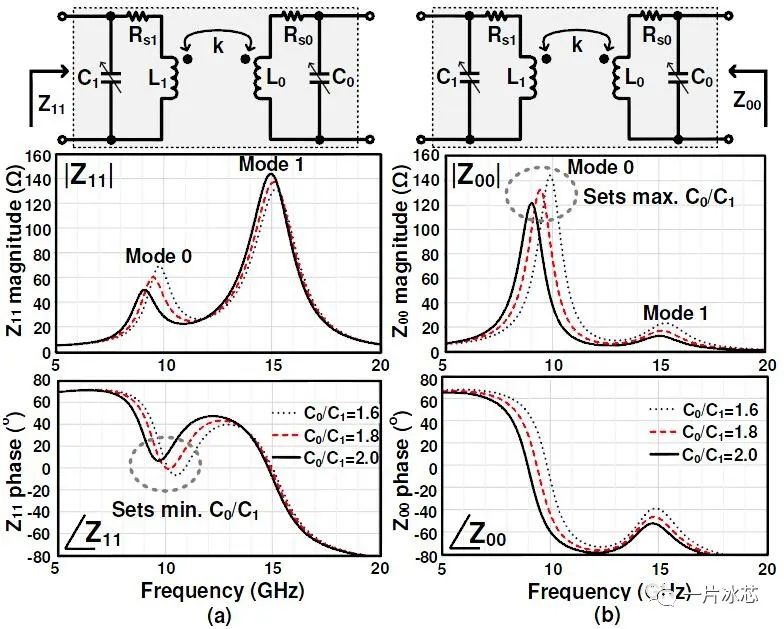

Z11和Z00的幅频和相频特性如图6所示。图中可以看出当C0/C1足够大(大于1.8)时,Z11相位只有一个过0点,因此,设置C0/C1大于1.8可以使Z11只有一个谐振点。随着C0/C1比值不断增大,Z00的幅度不断降低,因此,功耗限制了C0/C1的最大值。在频率调节过程中(粗调和细调)要时刻保持C0/C1的比值在1.8左右,以免谐振到谐波。

Fig6. (a) Z11 and (b) Z00 of a lossy transformer for different C0/C1

图7给出了Transformer的背景照片及结构,L0通过顶层金属与次顶层串联的方式增大L0感值,从而实现L0=L1。VCO面积仅为120 x 270 um^2^,最大功耗仅为4.4 mW。

Fig7. Chip micrograph and layout details

-

一款1.9~5.7 GHz宽带低噪声BiCMOS LC VCO设计2019-07-12 2142

-

求一种减少VDMOS寄生电容的新结构?2021-04-07 2039

-

介绍一种基于Internet的测控系统2021-05-26 1237

-

介绍一种基于FIFO结构的优化端点设计方案2021-05-31 1763

-

介绍一种按键检测电路2022-01-18 1726

-

一种新型结构的DC-AC矩阵变换器前级路介绍2009-04-03 575

-

一种新型的网格安全体系结构2009-08-13 632

-

一种基于FPGA实现的FFT结构2009-09-11 559

-

一种VLD结构VDMOS终端设计2017-01-07 887

-

详解一种简单而有效的Transformer提升技术2021-04-09 8047

-

一种新结构线性调节器的新应用2021-04-29 742

-

一种自适应网页结构化信息提取方法2021-05-08 972

-

关于Transformer的核心结构及原理2023-03-08 1734

-

Transformer结构及其应用详解2023-06-08 3453

-

大模型基础Transformer结构的原理解析2023-09-07 1862

全部0条评论

快来发表一下你的评论吧 !