AXI传输数据的过程

描述

以AXI4为例,有AXI full/lite/stream之分。

在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种:

•AXI-Lite,AXI-Full以及AXI-Stream,其中AXI-Lite和AXI-Full都是基于memory map的形式实现数据传输(即包括地址总线),而AXI-Stream是以数据流的形式传输,无地址。

•其中AXI-Lite是AXI-Full的简化版,适合小批量的数据传输,常用来进行命令的传输,IP核的初始化等。

•AXI-Full则适用于大批量,高性能的数据传输。

AXI是一种用于传输数据的模块或总线,用于两个模块或多个模块之间相互传递数据。它本身有很多优点,被SOC广泛采用了。

AXI传输数据的过程

AXI-full传输数据是全双工的,也就是说,读写是同时进行的。

一条AXI总线有5条通道,两个用于读,三个用于写。

首先描述一下AXI的写数据过程:

(1)Master主机通过写地址通道将地址传给Slave从机,从机收到地址可通过写数据通道往里送入数据,写完之后通过写回应通道给主机一个结束信号。

(注:写回应通道只需2个bit位就能代表四种状态,传成功了,传失败的几种状态)

(注:写回复是针对整个传输操作(transcaction)的,而不是针对每个写入数据(data transfer))。

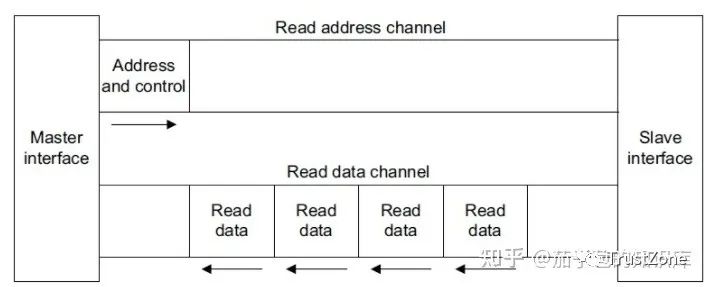

AXI读数据的过程:

主机给从机一个地址,从机通过读数据通道给主机返回数据。

为什么读只需要两个通道?因为完成信号可以用读数据传输一并传输。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RDMA简介8之AXI分析2025-06-24 764

-

ZYNQ的ARM和FPGA数据交互——AXI交互最重要的细节2023-11-03 2171

-

AXI数据传输读写数据结构2023-10-31 3826

-

AXI协议的几个关键特性2023-05-06 2071

-

浅析AXI DMA收发数据传输过程2022-10-11 3346

-

AXI VIP设计示例 AXI接口传输分析2022-07-08 3103

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10926

-

ARM系列 -- AXI协议资料汇总(一)2022-04-08 5529

-

AXI-stream数据传输过程2021-01-08 2909

-

Xilinx zynq AXI总线全面解读2020-12-04 9345

-

你必须了解的AXI总线详解2020-10-09 9232

-

AXI流数据包传输问题2019-04-15 2953

-

zynq linux AXI DMA传输步骤教程详解2018-07-08 32365

全部0条评论

快来发表一下你的评论吧 !