valid与ready信号有哪三种情况

描述

valid与ready信号分三种情况:

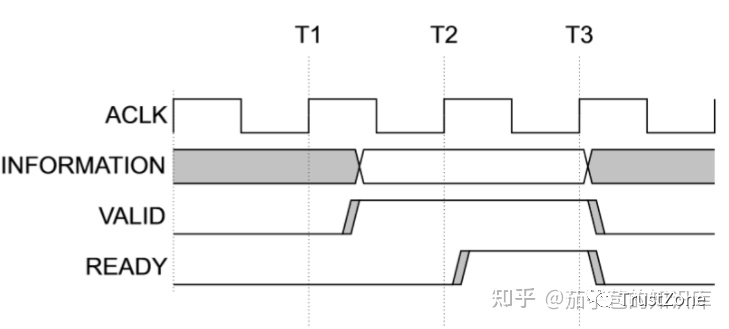

(1)valid信号先到达

主机valid信号早早就到了,T2时刻并没有见到接收方的ready信号。只能在T3时刻传输完成。

协议规定在这种情况下,valid信号一旦置起就不能置低,直到完成握手,至少传输一周期数据。 协议另外规定:发送方不能通过等待接收方 READY信号来确定置起 VALID 信号的时机。

通俗来讲就是设计发送方逻辑时,不能将 READY 信号作为置高 VALID 逻辑的条件,比如将 READY 信号通过组合逻辑生成 VALID信号,但接收方的ready信号按照协议可以依赖发送方的valid信号。

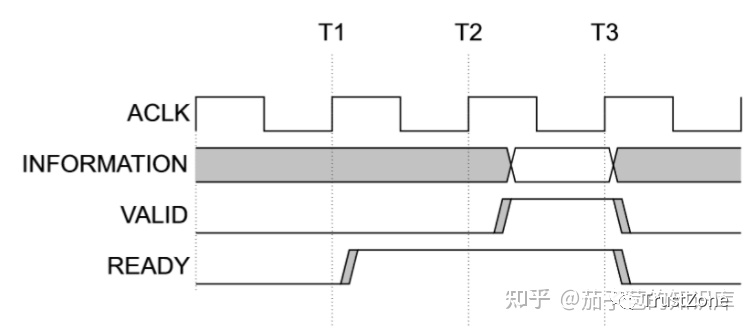

(2)ready信号先到达

ready信号很自由,可以等待valid信号到来之后再做响应,也可在valid信号到来前就置高,表示接收端已经做好准备。

而且,READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后置低 READY 信号。只要此时 VALID信号没有置起,这种操作是完全可以。

(3)tips

AXI总线是全双工的,全双工就意味着该总线的读写通道是分开的,互不影响,那就意味着每条通道都是单向传输,单向传输的通道就意味这两端节点的身份有差距,在AXI总线传输中,通道两端分为Master和Slave,主机总是发起读写请求的一方。

常见主机有CPU、DMA,而存储介质控制器则是典型的从机。主机可能通过从机读取或者写入存储介质。而显然从机不可能主动向 CPU 写入数据。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基本放大电路有哪三种2024-10-15 6277

-

数字示波器的测量方法有哪三种2024-07-17 4199

-

verilog中端口类型有哪三种2024-02-23 4346

-

valid-ready握手协议和enable-xoff协议对比2023-12-04 1928

-

电路短路的三种情况2023-11-23 10875

-

半导体的导电特性有哪三种2023-08-27 6404

-

在握手协议中的Valid及data打拍技巧2023-06-27 3029

-

网络拓扑结构哪三种2023-03-07 7089

-

常用的FBAR模型有哪三种?2021-03-11 2632

-

卷积的三种模式——full same valid2020-05-22 3522

-

电路的三种工作状态分别是什么2019-09-13 103563

-

三种投影机散热技术是哪三种2010-02-06 686

-

数码相机充电器对电池的充电状态判断方式有哪三种?2009-11-04 2982

-

有三种相位输出的移相器2009-04-15 1648

全部0条评论

快来发表一下你的评论吧 !