一种Inverter-Based CTLE以解决传统CTLE的不足

电子说

描述

传统CML结构的CTLE基于源极退化电阻电容实现均衡,当速度提高到56Gb/s或者112Gb/s时CML-based CTLE面临速度、面积、功耗的巨大压力(即使到了7nm工艺节点),本期介绍一种Inverter-Based CTLE以解决传统CTLE的不足。

1 从ISSCC2020看SerDes****未来

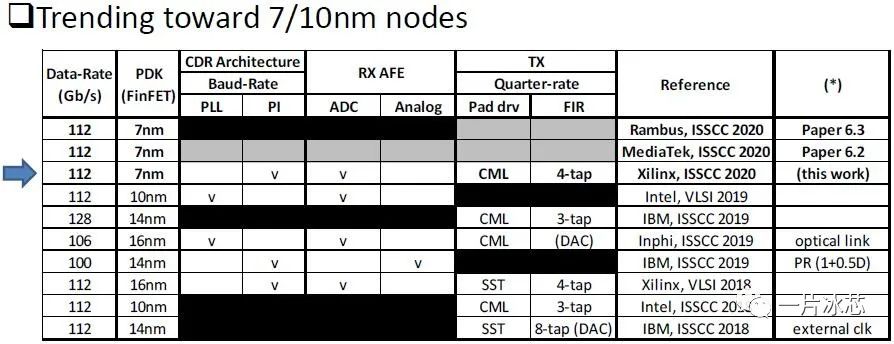

ISSCC2020 SESSION 6第一篇文章 ,是FPGA老大哥Xilinx发表的。图1给出了近三年(2018-2020)学术界或工业界发表的100Gb/s以上SerDes结构,我们可以得到以下结论:

① CDR采用PI-based双环路结构成为主流,双环路结构的优点是PLL环路(PI时钟)和CDR环路可以相互独立,同时多条Lane可共用同一时钟源,节约了功耗和面积;

② RX的DFE均衡变成了ADC+DSP结构,将复杂的均衡放到数字域去处理,减小PVT影响,同时便于工艺迁移;

③ 更多TX Driver采用CML结构(相对SST),因为CML结构在速度上具有优势;

④ 高速SerDes(56Gb/s+)具有超高的技术壁垒,玩家基本都是国外巨头,国内任重道远。

Fig1. 近三年100+ Gb/s SerDes结构

2 Inverter-BasedAFE结构

图2给出了112Gb/s RX sub-system,图中阴影部分的数据和时钟通路采用CMOS实现。那么CTLE和PGA如何用CMOS实现?本文为了提高速度提出了Inverter-Based CTLE和PGA 。

Fig2. RX sub-system

传统RC源极退化CTLE在112Gb/s速率下要保证带宽和线性度变得异常艰难,因为传统CTLE结构较复杂,电源到地通路堆叠的晶体管或电阻较多而且要在低电源电压下保证线性度,为了提高CTLE线性度我们只能进一步减小晶体管或电阻数目,减到最后不就变成Inverter了吗?

图3给出了112Gb/s RX sub-system中Inverter-Based CTLE结构图,合理设置输入输出管的共模电压和摆幅可得到线性增益,在负载管栅端(图中gm,hf和g m,lf )增加RC低通滤波器可实现peaking,采用有源电感(图中g mL )实现带宽拓展,具体工作原理详见第3章。

Fig3. Inverter-Based CTLE结构图

论文提出Inveter-Based CTLE全部采用纯CMOS实现(无电阻、电容、偏置、共模反馈),layout非常规整(Xilinx称之为“sea of gates”),如图4所示。单级CTLE面积仅为30 um*15 um,而且性能表现卓越。

Fig4. CTLE layout

3 Inverter-Based CTLE****原理

3.1 不同模式下 Inverter的小信号模型

文献[2]给出了Inverter工作在不同模式下的小信号模型,如图5所示,不同模式下的Inverter可以充当跨导、电阻以及有源电感。

Fig5. 不同工作模式下的Inverter及其等效模型

3.2 CTLE实现及仿真结果

将图5原理应用到图6所示电路可得其低频增益为g m1 /g ml ,高频增益为(g m1 +g m2 )/2g ml ,合理设置三者gm可实现CTLE均衡功能。

Fig6. Inverter-Based CTLE电路及仿真结果

3.3 subtractiveCTLE

文献[3]在文献[2]的基础上做了改进,提出了一种subtractive CTLE,将原来的additive CTLE的MOM飞电容(Flying capacitor)变成对地MOS电容,减小了面积,提高了线性度,但增大了功耗(典型的功耗换性能),如图7所示。

Fig7. Comparison of (a) additive and (b) subtractive CTLE circuit Inverter-Based

图8给出了Inverter-based单位增益放大器的大信号分析,为了在PVT下保证放大器的线性度,要求输入信号摆幅小于±300mV @ V DD =1.2V, V T =400mV。

Fig8. Inverter-based unity-gain stage for large-signal analysis

**4 **思考与讨论

① Inverter-Based CTLE变成了伪差分结构,对偶次谐波的抑制减弱,这在工程中是否引入较大的失真?

② 为了保证Inverter-Based CTLE的线性度,都采用了什么技术?

③ FinFET工艺和Bulk工艺下实现Inverter-Based CTLE有何区别?

④ 如何实现Inverter-Based CTLE高低频增益可配?

-

#CTLE技术#眼图#示波器 CTLE技术和运用过程的演示,让闭合眼图重新打开深圳市瑞普高电子有限公司 2024-03-05

-

浅析均衡器CTLE2019-07-23 3842

-

CTLE的结构中都包括什么?2021-03-06 4214

-

Inverter的工作原理介绍2021-11-15 1980

-

Frequency Inverter Based Drawi2009-01-19 1014

-

Z-Source Inverter for Power Co2010-02-21 535

-

以PC Based Controller设计Modbus通信2010-04-01 495

-

均衡器CTLE技术资料2017-09-19 1749

-

如何设置CTLE模拟以优化接收器眼图开度2018-11-28 5143

-

CTLE是什么?(原理、特点及作用)2021-04-07 36272

-

利用CTLE和时间交错闪存ADC来降低ADC分辨率2022-07-28 2559

-

CTLE均衡技术的工作原理2024-10-29 4802

全部0条评论

快来发表一下你的评论吧 !