FPGA中的逻辑运算是如何实现的?

可编程逻辑

描述

**1. **可编程逻辑功能块

可编程逻辑功能块(Configurable Logic Blocks, CLB),顾名思义就是可编程的数字逻辑电路,可以实现各种逻辑功能。

CLB是FPGA根据用户需求构建各种数字电路的核心模块,它是FPGA实现组合逻辑和时序逻辑电路的主要逻辑资源。同时,CLB也是FPGA芯片中利用率最高,占用面积最大的逻辑资源模块,它的作用犹如人体中最基本的细胞单元。

LUT也即我们常说的查找表,是CLB的主要功能模块,这点由CLB名字的全称(可配置逻辑功能块)就可以知道了。通过一个N输入的LUT可以实现任意N个变量的组合逻辑。为方便理解,我们以3输入LUT为例加以说明。

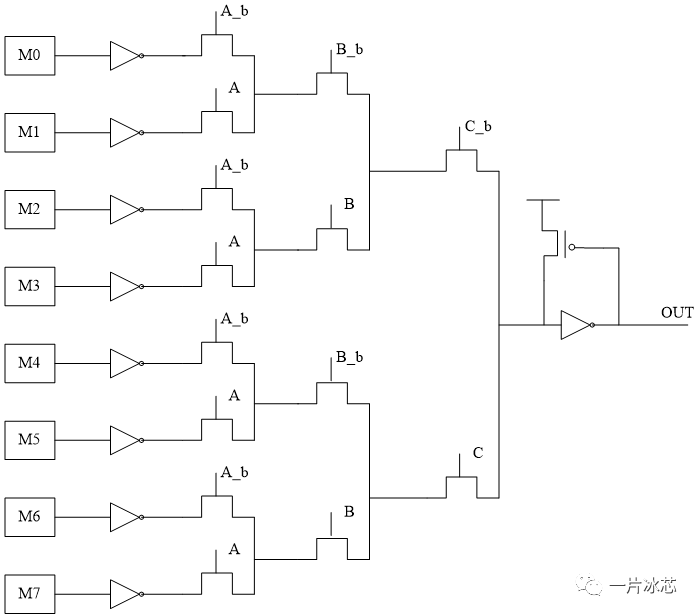

Fig1. LUT3原理图

图中M0-M7为查找表的配置存储器(即存储单元),通过编程下载将数据写入这个8个存储单元;输出OUT则根据A、B、C的值选择M0-M7的值。CBA=000时选择M0的值,CBA=001时选择M1的值,以此类推,CBA=111时就选择M7,这样就构成了一个Look up table,也就可以通过写入M0-M7适当的值来实现ABC的任意逻辑。

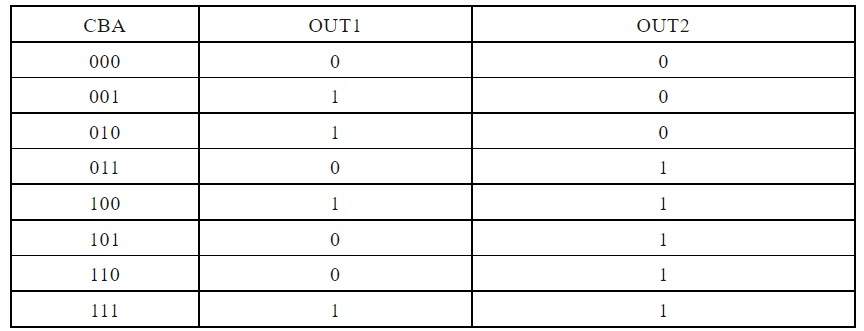

例如想要实现函数OUT1=C⊕B⊕A或函数OUT2=A&B+C,它们的真值表如下表1所示,所以只需要使M0-M7的值为01101001就可以实现函数OUT1的功能;只需要使M0-M7的值为00011111就可以实现函数OUT2的功能。6输入查找表原理一样。

表1 函数OUT1和OUT2的真值表

**2. **工程验证

2.1 建立Vivado****工程

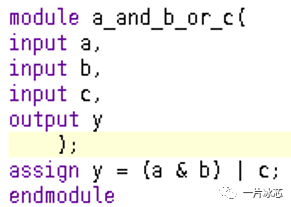

用Vivado软件编写verilog代码实现y = a & b + c,如下:

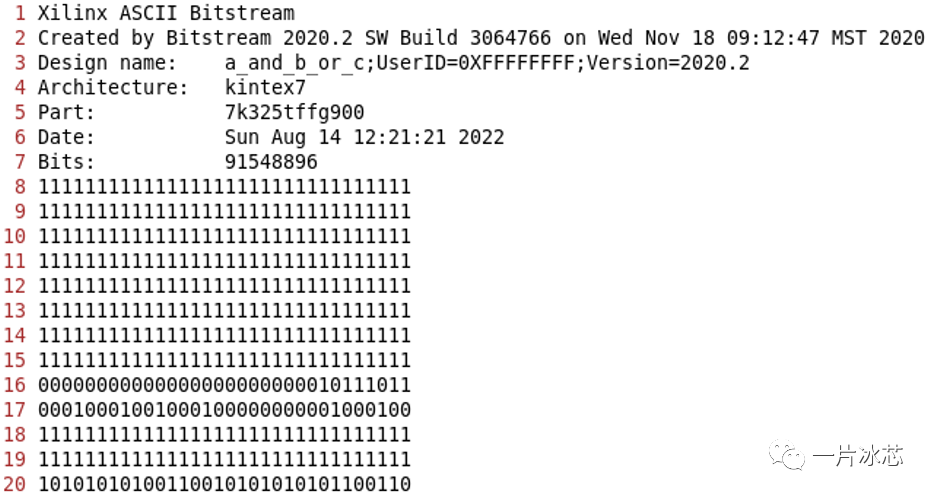

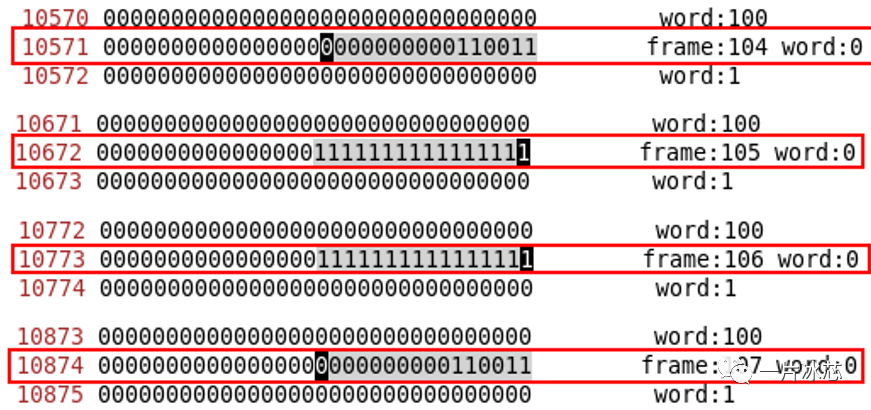

生成的bitstream(文件路径:工程名路径/工程名/工程名.runs/impl_1/工程名.rbt),如下(部分):

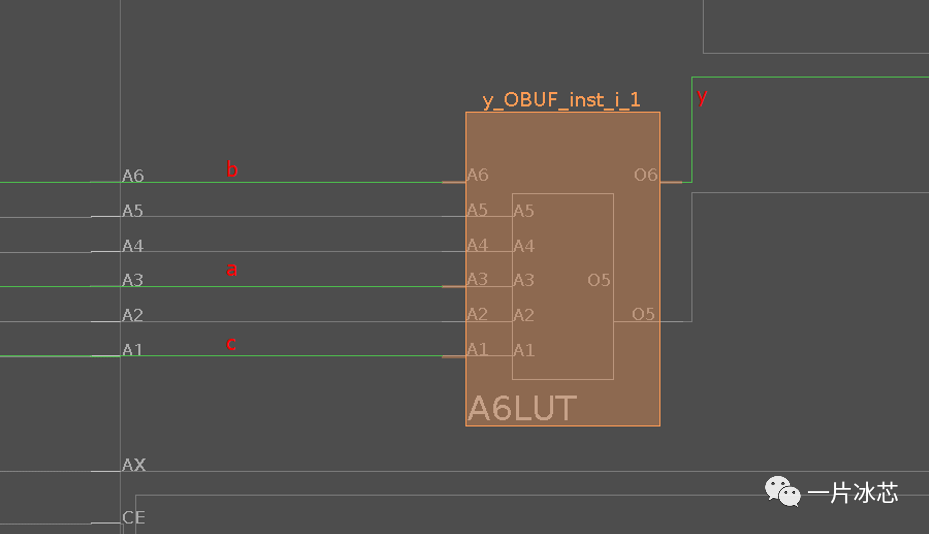

上述bitstream绝大部分会存储到FPGA的Memory Cell中,也就是图1中M7-M0的数据源。图1中的A、B、C和OUT来自FPGA的IO,由用户指定。其中A、B、C和OUT对应代码中的a、b、c和y。图2是Vivado自动布局布线出来的y = a & b + c,可以看出仅占用了FPGA的一个LUT6资源。

Fig2. y = a & b + c 软件视图

2.2解析bitstream

下载到图2中LUT6的Memory值是否是我们想要的呢?这就需要我们对bit流进程解析。

我们直接给出此LUT6占用的Memory Cell值及位置,如下:

其中frame表示一帧数据,共101个word,一个word表示32个Memory Cell,因此一个frame表示101 x 32 = 3232个Memory Cell。

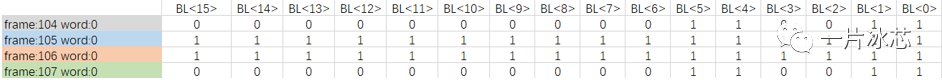

由第1章知识,可知一个LUT6需要2^6=64个Memory Cell,即上图灰色部分(16 x 4 = 64)。

**2.3 **分析验证

为便于分析我们把2.2节中frame:104/105/106/107 word:0的低16位取出放到表格里构成16x4的一个矩阵,如下:

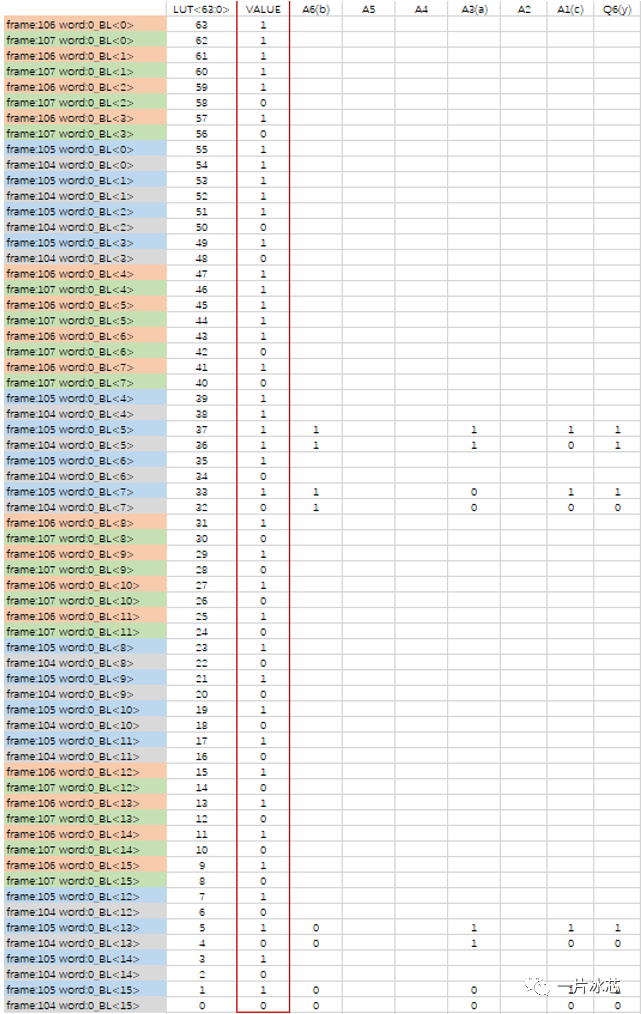

转换成64x1矩阵(转换关系由内部电路决定,这里直接给出),如下:

这里与表1呼应,至此我们工程化验证了y = a & b + c,你理解了吗?

**3. **思考与讨论

bitstream是如何烧写到FPGA芯片中的?如何利用CLB实现时序逻辑?FPGA内部时钟架构是什么样的?FPGA电源是如何划分的?

-

复合的逻辑运算2025-01-16 573

-

PLC中的逻辑运算方式有哪些2024-07-24 2144

-

verilog的逻辑运算符2023-09-21 3843

-

KUKA机器人的逻辑运算符2023-07-21 3540

-

三种基本逻辑运算介绍2023-03-23 9079

-

位逻辑运算符与表达式2023-02-21 2135

-

逻辑电路与逻辑运算符2021-07-16 1376

-

逻辑运算符是什么2021-07-14 1317

-

二进制数逻辑运算是怎么运算的2019-12-25 2618

-

基于单片机实现的逻辑运算程序详解2018-05-12 10852

-

16进制字符串的逻辑运算问题2013-09-17 7661

-

如何用“硅基”器件以外的材料实现逻辑运算。2012-12-29 2291

-

逻辑运算与移位指令2011-07-03 1251

-

逻辑运算,什么是逻辑运算2010-04-13 33001

全部0条评论

快来发表一下你的评论吧 !