晶圆术语 芯片ECO流程

描述

晶圆术语

1.芯片(chip、die)、器件(device)、电路(circuit)、微芯片(microchip)或条码(bar):所有这些名词指的是在晶圆表面占大部分面积的微芯片图形;

- 划片线(scribe line、saw line)或街区(street、avenue):这些区域是在晶圆上用来分隔不同芯片之间的间隔区。划片线通常是空白的,但有些公司在间隔区内放置对准标记,或测试的结构;

- 工程实验片(engineering die)和测试芯片(test die):这些芯片与正式芯片或电路芯片不同。它包括特殊的器件和电路模块用于晶圆生产工艺的电性测试;

- 边缘芯片(edge die):在晶圆边上的一些掩膜残缺不全的芯片而产生的面积损耗。由于单个芯片尺寸增大而造成的更多边缘浪费会由采用更大直径晶圆所弥补。推动半导体工业向更大直径晶圆发展的动力之一就是为了减少边缘芯片所占的面积;

- 晶圆的晶面(wafer crystal plane):图中的剖面标示了器件下面的晶格构造,此图中显示的器件边缘与晶格构造的方向是确定的;

- 晶圆定位边(wafer flats)/凹槽(notche):图示的晶圆由注定位边(major flat)和副定位边(minorflat),表示这是一个P型《100》晶向的晶圆。300mm和450mm直径的晶圆都是用凹槽作为晶格导向的标识。这些定位边和凹槽在一些晶圆生产工艺中还辅助晶圆的套准。

芯片ECO流程

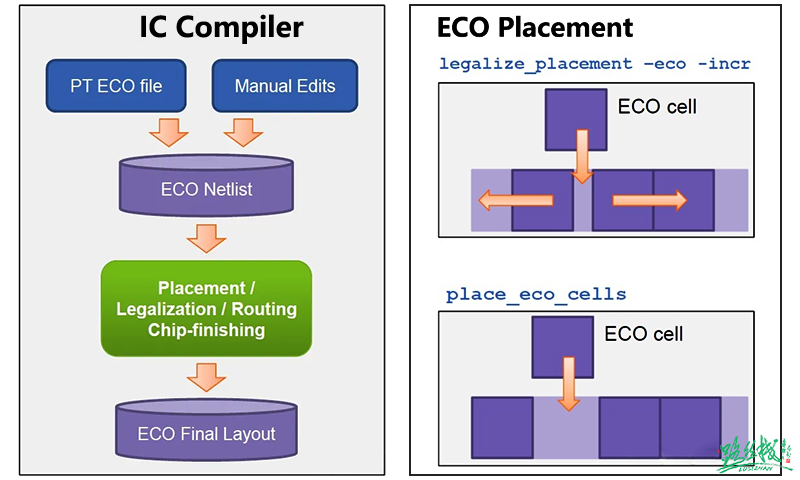

ECO 指的是Engineering Change Order,即工程变更指令。ECO可以发生在Tapeout之前,过程中,或者之后;Tapeout之后的ECO,改动少的可能仅需要改几层Metal layer,改动大可能需要动十几层Metal layer,甚至重新流片。ECO 的实现流程如下图所示:

如果MPW或者FullMask的芯片,验证有功能或者性能缺陷,通过ECO对电路和标准单元布局进行小范围调整,保持原设计布局布线结果基本不变的前提下做小规模优化,修复芯片的剩余违例,最终达到芯片的签核标准。不能通过后端布局布线的流程来修复违例(重新走一遍流程太费时了),而要通过ECO的流程来进行时序、DRC、DRV以及功耗等优化。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

详解晶圆的划片工艺流程2025-02-07 4022

-

硅晶圆的制备流程2024-10-21 2631

-

晶圆级封装的基本流程2023-11-08 12118

-

晶圆生产的目标及术语介绍2023-05-06 2455

-

为什么芯片是方的,晶圆是圆的?2022-12-19 4458

-

晶圆和芯片的关系,晶圆能做多少个芯片2022-01-29 62809

-

从晶圆到芯片,有哪些工艺流程?2021-12-30 21224

-

如何做晶圆切割(划片),晶圆切割的工艺流程2020-12-24 20693

-

晶圆制造工艺的流程是什么样的?2019-09-17 12305

-

晶圆制造流程2018-08-21 52157

-

史上最全晶圆专业术语2011-12-01 36801

全部0条评论

快来发表一下你的评论吧 !