FPGA学习-时序逻辑电路

描述

时序逻辑电路

一:触发器

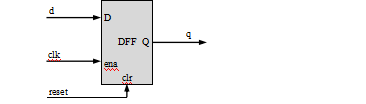

1:D触发器:时序逻辑电路最小单元。

(1):D触发器工作原理

忽略清零端情况下:当使能条件(往往为时钟的触发沿:上升沿/下降沿)满足时,将输入D端的数据给到输出Q,当使能条件不满足时,输入数据D会暂存在触发器当中,直到触发条件满足才给到输出Q。

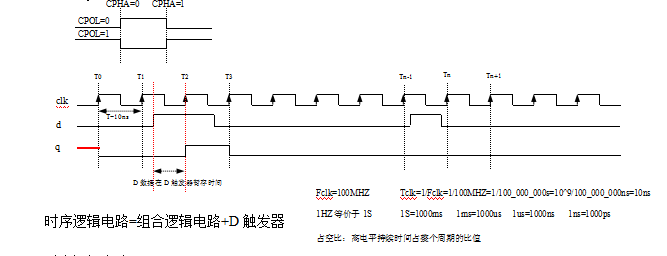

(2):D触发器工作时序

时钟clk:周期性变化信号。

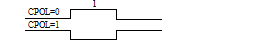

时钟极性(CPOL):时钟初始值是0,时钟极性为0;时钟初始值是1,时钟极性为1。

时钟相位(CPHA):出现第一个沿,时钟相位为0;出现第二个沿,时钟相位为1。

时序逻辑电路=组合逻辑电路+D触发器

二:时序逻辑电路

1:时序逻辑电路概念:

2:时序逻辑电路建模采用行为建模

以“always”为关键字出现,不仅可以描述组合逻辑电路;也可以描述时序逻辑电路。

(1):如果描述的是组合逻辑电路,表示形式为always @ (电平信号),一般可以写成:always @ (A0,A1,A2)/always @ (*)----组合逻辑电路

所有的组合逻辑电路赋值方式全部为阻塞赋值(“=”);

所有在always块中位于赋值号左侧信号必须定义为寄存器型(“reg”)。

(2):如果描述的是时序逻辑电路,表示形式为always @ (posedge clk)/always @ (negedge clk)。

always @ (posedge clk, negedge rst_n)----异步复位

always @ (posedge clk)----同步复位

所有的时序逻辑电路赋值方式全部为非阻塞赋值(“<=”);

所有在always块中位于赋值号左侧信号必须定义为寄存器型(“reg”)。

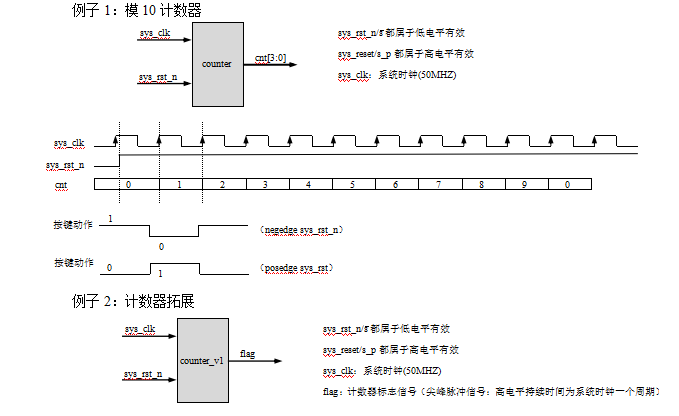

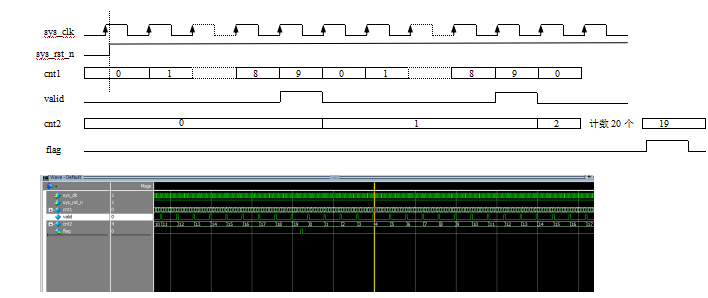

三:时序逻辑电路实例

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-时序逻辑电路

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- FPGA

-

时序逻辑电路有记忆功能吗2024-08-29 2983

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 14528

-

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?2023-04-23 2993

-

组合逻辑电路和时序逻辑电路的区别和联系2023-03-14 9332

-

组合逻辑电路和时序逻辑电路的学习课件免费下载2020-10-27 1597

-

什么是时序逻辑电路2019-02-26 33288

-

时序逻辑电路由什么组成_时序逻辑电路特点是什么2018-03-01 112400

-

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别2018-01-30 95153

-

时序逻辑电路的分析与设计2016-09-02 1245

-

时序逻辑电路的相关知识概述2016-02-29 896

-

fpga时序逻辑电路的分析和设计2012-06-20 10035

-

时序逻辑电路2010-08-10 967

-

同步时序逻辑电路2009-09-01 1160

全部0条评论

快来发表一下你的评论吧 !