芯片的真实成本是多少?

描述

过去,分析师、顾问和许多其他专家试图估算采用最新工艺技术实现的新芯片的成本。他们的结论是,到了 3nm 节点,只有少数公司能够负担得起——而当他们进入埃范围时,可能没有人可以支付了。

过去一段时间的几个流程节点发生了很大变化。越来越多的初创公司正在成功构建先进节点芯片,但其成本远低于那些被高调引用的数字。这些数字的背后是芯片设计和制造方面的一些广泛的变化。他们之中:许多先进节点芯片要么是用于人工智能/机器学习的高度复制的乘法累加处理元件阵列。与将不同组件集成到单个芯片上相比,这些相对简单,需要针对热问题、噪声以及各种用例和应用来表征它们。

自这些早期估计产生以来,先进封装已成为主流,它允许芯片制造商将在不同工艺节点开发的芯片或小芯片捆绑在一起,而不是试图将模拟功能推向 5 纳米及以上,这既昂贵又无益。

过去,迁移到最新节点可确保性能和功耗的市场领先地位。现在已不再是这种情况。成熟节点的改进以及涉及硬件和软件的架构变化使许多芯片制造商能够推迟迁移到最新节点,至少直到这些流程足够成熟且具有成本效益。

早期预估的一大问题是它们是对当时可用的最佳数据的推断。主要来源是 2016 年逐步淘汰的国际半导体技术路线图。在接下来的几年里,芯片设计和制造的基本原理发生了巨大变化。

例如,许多人认为所有新芯片都会填满标线,并且设计的尺寸和复杂性将继续增长。在某些情况下,复杂性确实增加了,远远超出了将所有最新功能安装在单个掩模版上的程度。但其中许多新功能是使用最新工艺几何形状和已建立的工艺节点的组合来开发的。在其他情况下,封装中处理元件的数量增加了,但复杂性实际上下降了。

软件是另一个定义要素。并非所有软件都需要从头开始开发。此外,还有大量适用于 Arm、NVIDIA 以及越来越多的 RISC-V 设计的现有工具和生态系统。几乎所有大型 EDA 公司都在人工智能/机器学习方面投入巨资,以缩短和改进设计流程,特别是在软件调试以及通过强化学习更有效地利用整个公司的专业知识方面。

数字

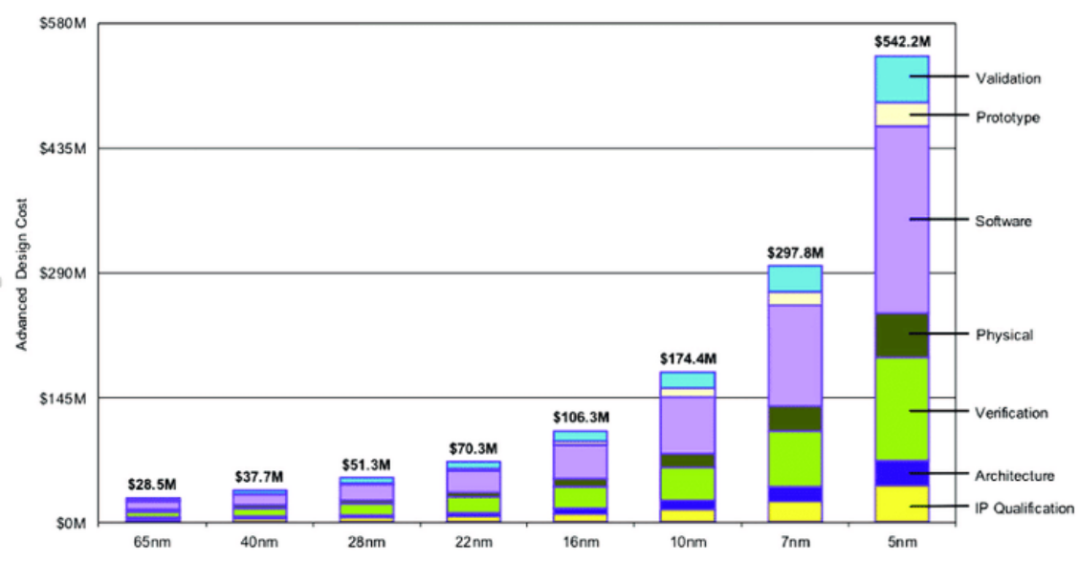

早在 2018 年,即最后一次有人做出此类估计时,IBS 发布了如图 1 所示的图表。该图表将 5nm 芯片的成本定为 5.422 亿美元。如果这是真的,那么今天显然只会生产两到三个芯片,而且可能没有人会关注 3nm 以外的技术。

图 1:生产新芯片的成本。来源:IBS 2018

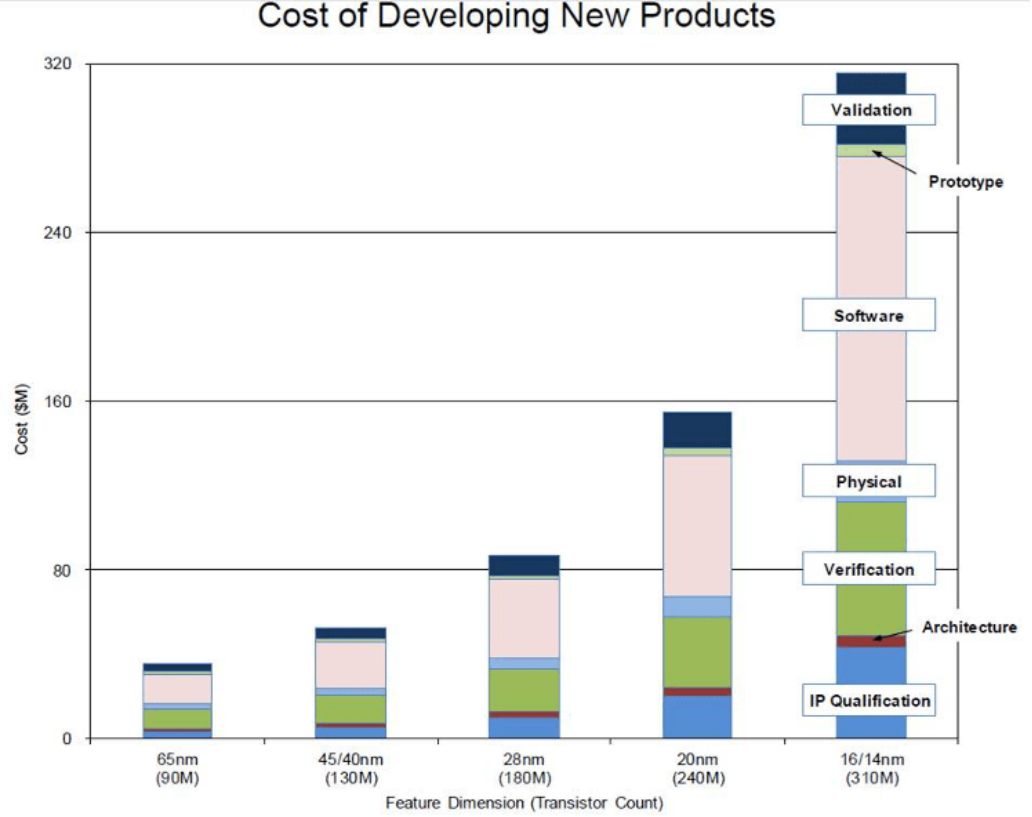

如果我们回顾几年,并将其与 IBS 在 2014 年制作的图表进行比较(见图 2),我们可以看到这些估计值如何随时间变化。

图 2:生产新芯片的成本。来源:IBS 2014

16nm/14nm 的估计成本从约 3.1 亿美元增至 1.06 亿美元。再往前追溯,28nm 的价格从大约 8500 万美元增至 5100 万美元。这是否超出了估计成本,或者这反映了一旦新节点变得更加成熟,成本就会急剧下降,这是一个有争议的问题。但如果最新数据按类似金额折算,则 5nm 芯片的成本约为 2.8 亿美元,7nm 芯片的成本约为 1.6 亿美元。

Siemens Digital Industries Software营销和业务开发高级总监 Isadore Katz 说道。“如果考虑高通或英伟达建造一款新芯片确实花费了 5.42 亿美元,那么他们和其他一些人可能是唯一真正有能力去做这件事的人。但他们不会制造 5 nm芯片。他们将采用一种架构,在该架构中进行一些创新,作为过渡到新工艺节点的一部分,然后他们将开发一系列在该工艺节点上运行的部件。”

很少有公司公布其实际成本,但可以查看公司收到的风险投资,并通过查看他们在发布第一个芯片时消耗了多少钱来找到粗略成本。Achronix 产品规划高级总监尼克·伊利亚迪斯 (Nick Ilyadis) 表示:“Innovium 的初始芯片投入了 1.5 亿美元,然后他们又获得了 1 亿美元的另一轮融资,资助了多代芯片。” “自 2014 年成立以来,Innovium 在 10 轮融资中总共获得了 4.02 亿美元的融资,并且在 2021 年以 10 亿美元的价格出售给 Marvell 时,手头仍有 1.45 亿美元的现金。他们的第三代芯片采用 7 nm工艺制造。”

成本的很大一部分是先进入者的学费。Ansys产品营销总监 Marc Swinnen 表示:“与大型数字芯片相关的费用呈爆炸式增长,这就是那些大标题数字的来源。苹果公司创造一款新芯片需要什么:18 个月、数百名设计师、许可证、一套全新的掩模组、先进的工艺。到时候成本就会上升。但如果使用较旧的节点,那么现在这些成本就会低得多。”

这些数字中还可能隐藏着一些成本。“确实需要大量投资来重新表征新晶体管的功能,使掩模制造能力到位,了解制造问题,创建提取模型,”西门子的卡茨说。“但是我们正在利用之前节点上的经验教训,一旦我们完成了这些构建块、BSIM-CMG 模型、提取模型、芯片变化和金属化,我们就能够利用参数化、或我们在上层拥有的独立处理技术。”

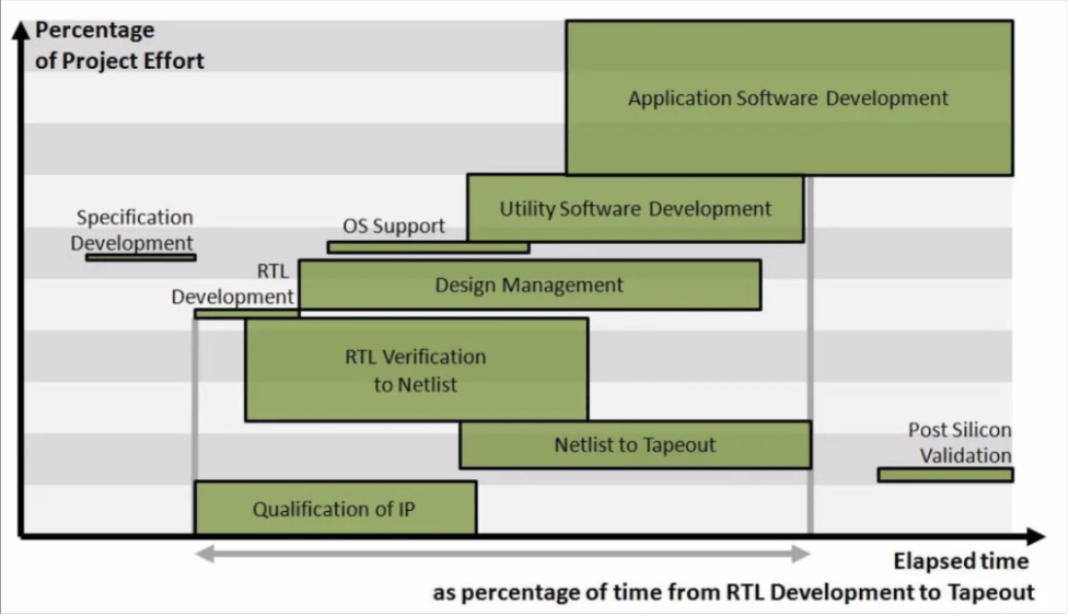

这些数字让其他人感到好奇。“这是我 12 年前创建的图表(见图 3),”Arteris 解决方案和业务开发副总裁 Frank Schirrmeister说道。“我从 IBS 收到了四到五组数据,但无法公布这些数据,所以我创建的图表对支出类别进行了平均。这显示了芯片开发的主要步骤。它沿 x 轴显示了从 RTL 开发到流片的时间线。然后整个项目工作量的百分比位于 y 轴上。”

图 3:制造芯片所需的时间和精力。来源:弗兰克·席尔梅斯特

根据图 3,可以考虑其中任何一个是否会随着时间的推移而发生变化,或者是否会随着规模或生产节点的变化而变化。例如,人们经常声称验证成本随着规模的大小呈二次方上升,尽管历史证明这并非事实。“验证成本确实会上升,因为设计越大,模拟所需的时间就越长,需要生成的测试用例就越多,”伊利亚迪斯说。“您可以使用前几代的基线测试,并继续运行它们。然后是与正在添加的附加功能相关的新测试。这需要更多的服务器、更大的服务器、更多的磁盘。它会作为额外成本波及基础设施。”

基础设施是否包含在公布的成本中?“关键在于如何理解这些数字的细节,”Arteris 的 Schirrmeister 说道。“所有的软件都包含在其中吗?其中有多少新的 RTL 开发?验证多少?需要买模拟器吗?当你研究一下掩膜的成本时,你会发现,这至少与这些芯片的成本相当。”

有些成本确实会随着时间的推移而下降。“当你考虑 IP 的成本时,你要么必须使用内部工程资源来开发它,要么必须获得许可,这意味着你需要向供应商付费,”Ilyadis 说。“通常,许可证附带支持和维护——这就是现金支出。然后是工具成本。每一代都需要一套新的工具,因为布线变得更加复杂或者需要考虑其他事情。有正在开发芯片的团队的人数。另外,还必须构建测试装置,甚至是可以演示的芯片产品。现在我们要讨论芯片本身之外的问题,但所有这些都与实际芯片开发以及将其推向市场所需的内容相关。然后就是不断赠送的礼物——软件。大多数这些芯片都具有某种可编程性。最重要的是制造,包括测试仪、测试夹具和用于进行加速寿命测试的老化夹具。”

即使 IP 成本也可能是一个重要的变量,特别是如果您考虑通过购买 IP 节省的时间或与开发 IP 相关的间接成本。“SoC 设计成本和复杂性的增加给计算基础设施带来了更大的压力,” Arm基础设施业务线产品管理高级总监 Brian Jeff 表示。“这正在推动定制芯片的发展趋势,以便为特定工作负载提供专门的处理,并获得大规模的效率节省。通过开发具有可定制基础的 IP,它使 IP 提供商能够承担合作伙伴必须重复设计的许多常见集成、验证和验证任务。这使得合作伙伴能够将资源集中在有助于他们区分和塑造适合其工作负载的完整芯片设计的功能上。在一个示例中,合作伙伴将其高端基础设施 SoC 开发成本降低了 80 个工程年。”

许多成本是增量的。“我们不会重新学习流程节点之间的所有内容,”卡茨说。“我们记住我们必须做的事情。我们在参数化或设计工件的表示方面投入了大量资金,从最顶层、测试平台、我们描述 IP 的方式、我们表达自定义逻辑和加速器的方式,一直到我们如何布局单元。我们了解必须在哪些地方进行调整,并且有旋钮和旋钮可以进行纠正。节点之间没有人从零开始。即使我们改变晶体管表面的工作方式,或者重新组织第一级个性化金属的工作方式,我们也确实需要花费额外的时间来表征。我们需要花费额外的时间来了解如何提取它,并且我们可能必须对我们的单元设计进行小而适度的调整以适应它。但基本的拓扑结构就在那里。”

成熟的 IP 将可在多代芯片中重复使用。英特尔、AMD、Marvell、博通、NVIDIA 和高通等公司内部开发了很多 IP。其中一些以小芯片的形式出现,可以在预先确定的架构中对其进行全面表征和重复使用。其代价是需要内部专业知识,但该领域的惊喜也较少,并且没有许可成本。

EDA 的成本

每个节点都会产生一些新的问题和挑战,这通常需要 EDA 供应商对新工具或流程的创建进行大量投资。当节点是新的时,许多工具都是粗糙的,解决方案是与任何可以解决问题的技术拼凑在一起的。

随着时间的推移,行业会了解什么有效,什么无效,流程得到改善,最终实现自动化。“许多挑战都可以通过蛮力来克服,”Ansys 的 Swinnen 说道。“他们利用了可用的工具和足够多的人员,并使其发挥作用。这需要与供应商密切合作。这不是一个可以提供给常规主流芯片设计人员的流程。随着时间的推移,我们向他们学习,他们也向我们学习。工具变得更好,自动化程度更高,粗糙的边缘已被消除,中间的手动步骤也已减少。这使得生产力大大提高。”

不过,今天行之有效的方法在未来可能行不通。“你必须计划一系列事情,”卡茨说。“我参与了计时、过程变化和地弹方面的工作。当您将电压阈值降低到 1V 以下时,其中许多问题就会成为问题。当我们进入 14 nm时,这是未知的。今天终于明白了。人们了解设计的时序或布局可能会出现什么问题。他们了解金属对延迟和定时的贡献必须注意的因素,并且他们也越来越意识到一些物理副作用、对毛刺噪声的敏感性、对泄漏。这些都添加到了剧本中。该手册将引导您了解过去 10 或 15 年中的每一个陷阱。你如何解决这些问题?你如何自动化这些?或者说,你是如何设计这些的?”

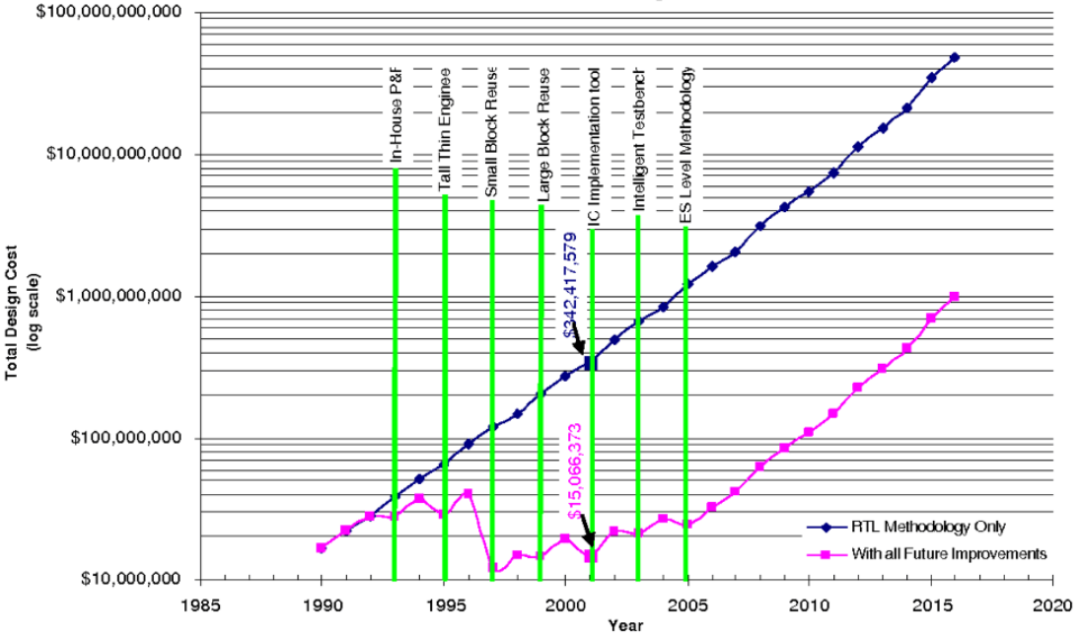

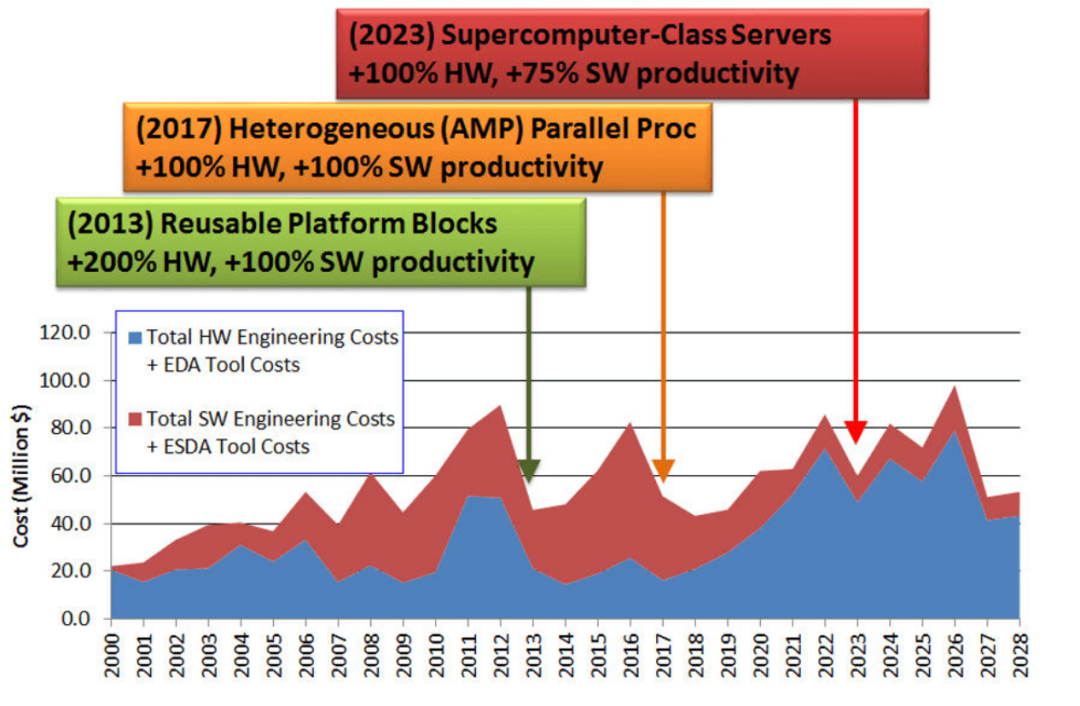

另一张值得重新审视的旧图表如图 4 所示。Andrew Kahng 和 Gary Smith 在 2001 年对设计成本进行了分析,以显示新的 EDA 开发如何影响生产力。该报告由 ITRS 于 2002 年发布。

图 4:2001 年 ITRS 的新设计成本模型。来源:2002 年质量电子设计国际研讨会论文集

虽然这展示了从未出现过的未来技术,例如 ESL,但其他技术却出现了。ITRS 的后续出版物表明,开发成本确实保持一定程度的静态,随着时间的推移,成本只会略有增加。图 5(下)是 2013 年的图表。

图 5:EDA 对 IC 设计成本的影响。来源:安德鲁·康,2013 年

开发成本确实会上升,特别是对于新节点。“工具变得越来越复杂,并且必须根据设计尺寸进行扩展”Ilyadis 说。“通常情况下,这些更新的工具可能会一代又一代地增加 25% 的成本,而这正是工具公司赚钱的地方。他们必须进行开发,必须在工具中投入工作,以使它们与下一代 IP 兼容,无论出现什么新挑战,因此他们都会将开发成本作为增加的许可费转嫁出去。”

但对于主流开发者来说情况并非如此。“在半导体设计的经济学中,EDA 工具的成本从来都不是一个关键考虑因素,”Swinnen 说。“这是人们必须担心的成本因素,但在芯片设计的整体经济性中,EDA 从来都不是决定因素。这是制造业。EDA 对设计成本的影响更多的是生产力。”

可以看到与 EDA 工具相关的基础设施成本迅速增加。“随着人工智能被引入工具套件中,人们很容易开始对设计空间进行更多探索,”Schirrmeister 说。“图表中的每个数据点都意味着在云中运行的额外容量和周期。为了获得最佳实施,您现在花费更多的计算工作。过去是人员乘以时间和一些基础设施成本,现在正在成为成本的重新分配,其中计算成本本身在整体成本方程式中扮演着更高的角色。”

结论

迄今为止,没有一款芯片的成本能够达到公开数据中显示的水平,因为没有一款芯片能够真正从一张白纸开始。这个行业的一切都基于知识产权的重用,其中一些与 IP 块相关,一些与 BSIM 模型相关,一些在创办新公司的工程师的头脑中。对于总是建立在大量代码库之上的软件行业来说,即使不是更多,也是如此。但这些数字对于前沿设计来说是正确的数量级。了解与开发相关的总成本非常重要,而不仅仅是关注流片。

-

现在最新的PADS版本是多少啊! 大虾们!~2012-07-15 12188

-

请教:LABVIEW的最新版本是多少2013-05-22 3886

-

请教protel ***目前最新的版本是多少?2013-08-28 4140

-

大咖帮忙解释下多层PCB制造成本是多少?2019-07-29 1866

-

请问XP系统支持CCS的最高版本是多少?2019-10-23 3144

-

请问BlunoBasicDemo.apk的版本是多少?2019-11-08 2046

-

请问官方镜像基于的BSP版本是多少?2021-12-30 1304

-

请问目前鸿蒙手机最新版本是多少?2022-05-30 6555

-

暴利?一枚芯片的实际成本是多少?2016-04-25 28197

-

解读芯片硬件成本之外的软性成本2016-04-28 2388

-

数据中心停机成本是多少?2017-11-28 1450

-

Vive Pro的成本是多少?也许不久会随着其价格的发布而得到解答2018-06-14 1246

-

使用先进工艺的芯片设计成本是多少2023-11-01 1448

-

连接器的真正成本是多少?2023-12-01 2260

-

智慧路灯的成本是多少2025-03-27 905

全部0条评论

快来发表一下你的评论吧 !