分享一种将AD原理图更新Allegro PCB文件的方法

电子说

描述

Altium Designer是原Protel软件开发商Altium公司推出的一款优秀的电子EDA设计软件,主要运行在Windows操作系统。Altium Designer 除了全面继承包括Protel 99SE、Protel DXP在内的先前一系列版本的功能和优点外,还增加了许多改进和很多高端功能。

Protel在很多学校都有普及使用,从使用群体数量来讲,无疑是众多PCB设计的EDA软件中使用人数最多的。

但卫红的工程师们长期使用的EDA软件为Cadence和Pads,对AD的了解还停留在Protel99se的时代。几天前 ,一个客户发来一个AD的原理图,希望能做出PCB设计,鉴于对AD不熟悉,只能使用Cadence Allegro进行PCB设计。

最初尝试将AD的原理图转为OrCAD的原理图进行设计,而且现在OrCAD17.4的软件也可以很方便的将AD的PCBDOC文件转成ORCAD的DSN文件。

但转换后发现一个问题,AD的原理图中不同页码中相同的网络,转成了DSN文件中,这些网络名字后面都被加了“_1"、”_2"等变成了不同的网络,这样实际相同的网络都没法连接起来。

经过研究才发现,这个是软件间不同的使用Ruler造成的,在OrCAD中不同页码之间相同的网络,必须通过跨页连接符offpage来定义连接,在AD中则不需要,只要定义相同的Net label,就直接默认连接起来。这就造成了AD的原理图转换到OrCAD后,Net label虽然在的,但页码之间没有offpage,OrCAD就认为不是相同的网络。

重新添加offpage工作量很大,而且AD中原理图和PCB封装名字和属性都习惯用小数线、空格之类的,这些在OrCAD中都不支持的,导致即使原理图可以用,导Netlist时也会report出来很多问题,只有把这些名字中非法字符更改后,才能顺利导出Netlist文件。关键是EDA工程师对原理图不熟悉,更改原理图后可能会产生一些不可控的问题出现会影响到PCB设计端。

几番衡量之后,还是决定将客户的原理图导出网表后,将Netlist的网表导入到Cadence Allegro中进行PCB设计,感谢行业资深工程师陈工提供的Netlist转换工具,先将具体的方法分享给大家。

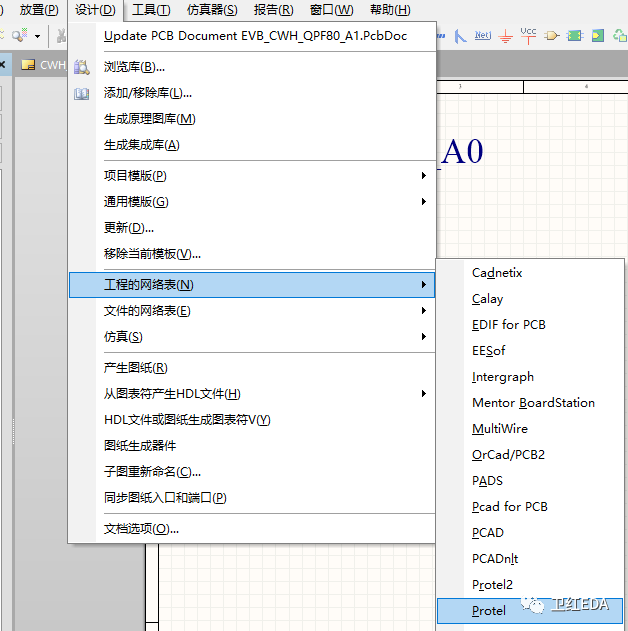

1、先将AD的原理图,导出Protel格式的Netlist文件,操作如下图所示,要导出整个工程的网表,不是某页的网表;

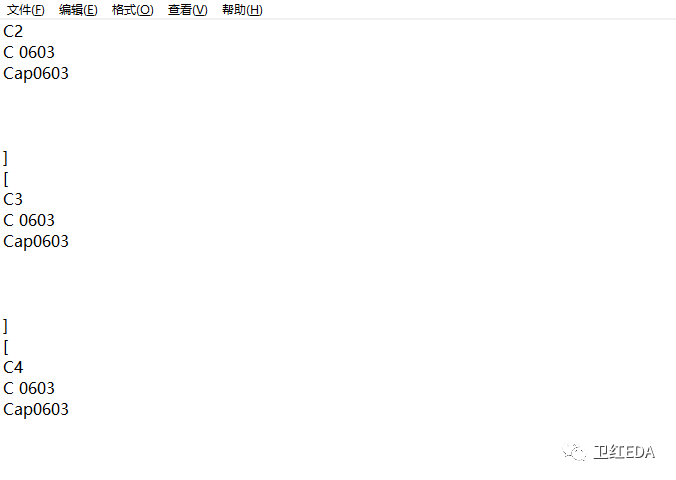

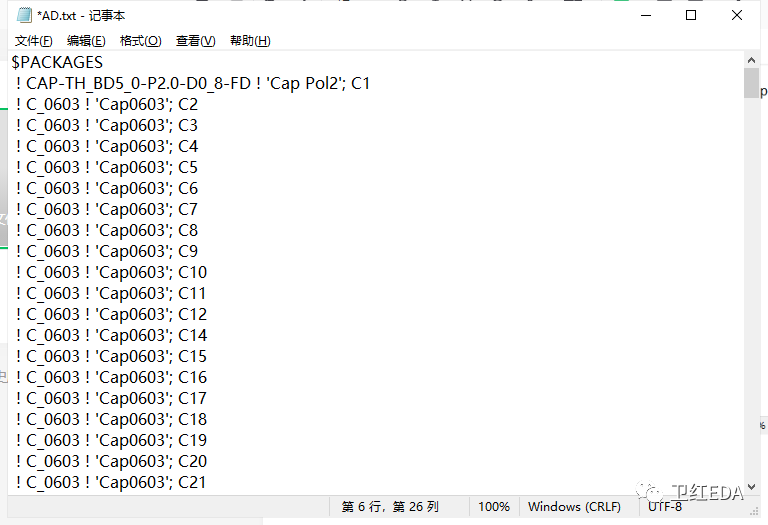

2、Protel格式的Netlist文件后缀名是net的,用记事本打开后,是这个样子,如下图所示,这个格式显然是Allegro不能识别的,我们需要将Netlist文件进行转换下;

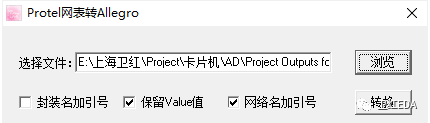

3、打开Protel网表转Allegro.exe的程序文件,选择Protel格式的Netlist文件,其他默认选择,点击转换进行网表格式转换;

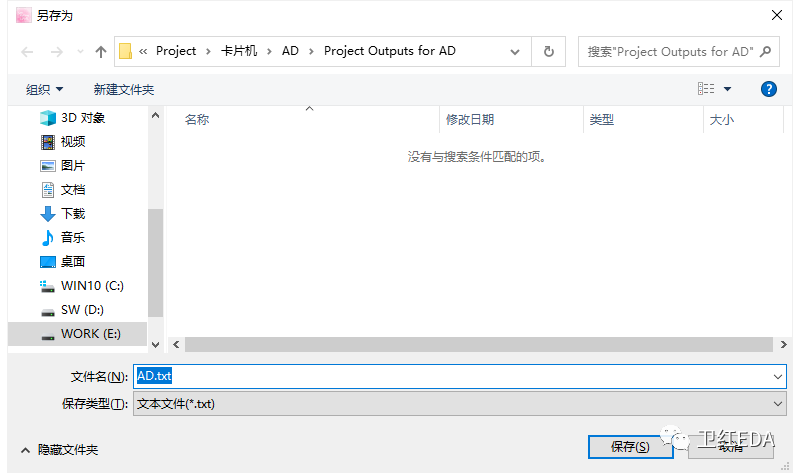

然后就生成了一个txt后缀名的文件,如下图所示,直接点击保存即可;

4、用记事本打开转换成的txt文件,可以看到文件格式转换已经好了,但名字中出现了很多小数点和空格的非法字符,这个比较麻烦,就需要手动去修改下,如果这款软件能自动把小数点和空格自动改为Underline,那就更方便了;

5、这个还需要手动把“!”前的一部分删除掉,更改后的结果如下图所示;

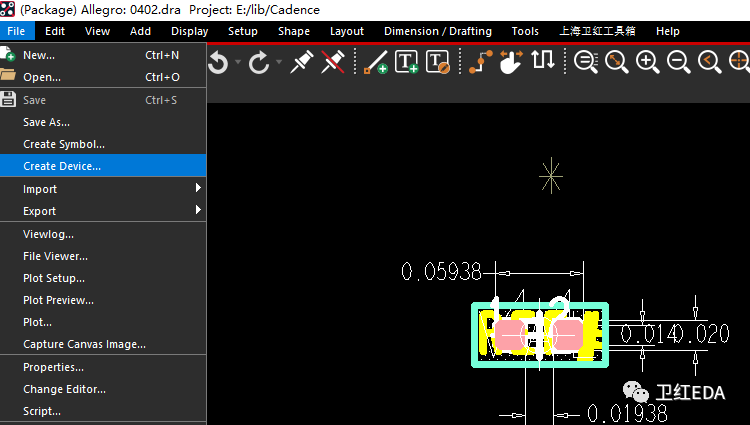

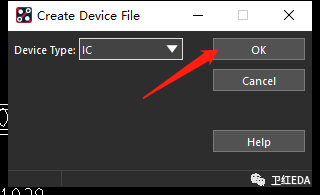

6、还有一点的就是PCB封装不仅要有dra文件、symbol文件,还要有device文件,这个可以打开dra文件,然后执行Creat Device,如下图所示;

直接点击OK就生成了一个txt的device文件,操作虽然很简单,但架不住封装数量多,可以做个批处理的脚本文件来自动执行;

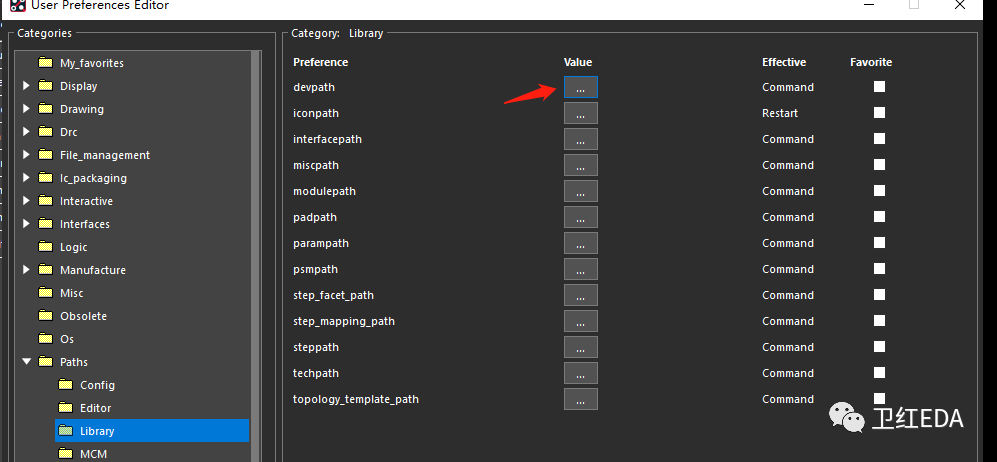

同时,不要忘了将device文件的路径更改到PCB库的路径一样;

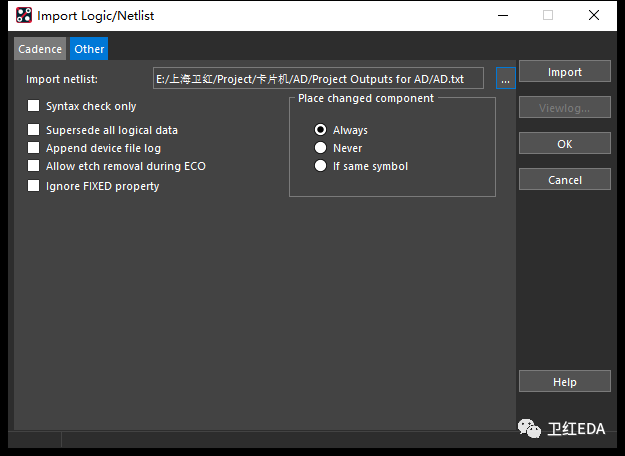

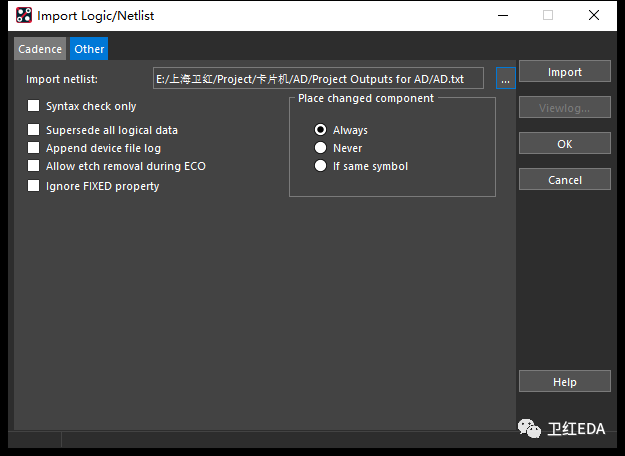

7、最后就需要将更改后的Netlist文件导入到Allegro的PCB文件中了,导入后可能会有很多的报错信息出现,比如device文件找不到, 需要有很大的耐心去处理。

-

jf_19928712

2024-09-09

0 回复 举报Protel网表转Allegro.exe工具可以分享一下吗 博主 收起回复

jf_19928712

2024-09-09

0 回复 举报Protel网表转Allegro.exe工具可以分享一下吗 博主 收起回复

-

使用ORCAD做原理图PADS做PCB的方法步骤2014-11-15 12479

-

PCB文件PROTEL到ALLEGRO的转换的注意事项与技巧2018-09-17 2032

-

将Protel DXP 的PCB 板子转到Allegro实战2019-07-08 2410

-

Altium的pcb文件转allegro的方法2019-09-03 5295

-

Allegro文件转成PADS文档的方法2019-09-17 8735

-

ALtium原理图更新时,未改变元件,但PCB出现改动的解决方法2019-09-29 4037

-

Cadence Allegro 17.2更新元件封装的操作方法2020-07-06 10735

-

portel的PCB文件怎么导入allegro2010-03-18 6438

-

Cadence_Concept_HDL&Allegro原理图与PCB设计2016-01-20 1558

-

allegro 快速更新封装2018-08-11 3535

-

Altium Designer原理图设计导入PCB的两种方法2020-10-16 88520

-

Altium Designer原理图PCB转换到cadence的方法(一)2023-03-07 32377

-

Cadence allegro更新PCB封装的方法2023-03-27 13656

-

PCB原理图与PCB设计文件的区别2023-08-01 7032

-

Allegro原理图与PCB设计.zip2022-12-30 1188

全部0条评论

快来发表一下你的评论吧 !