射频基础知识问答题及答案

RF/无线

描述

01

有关ADS版图的仿真的问题

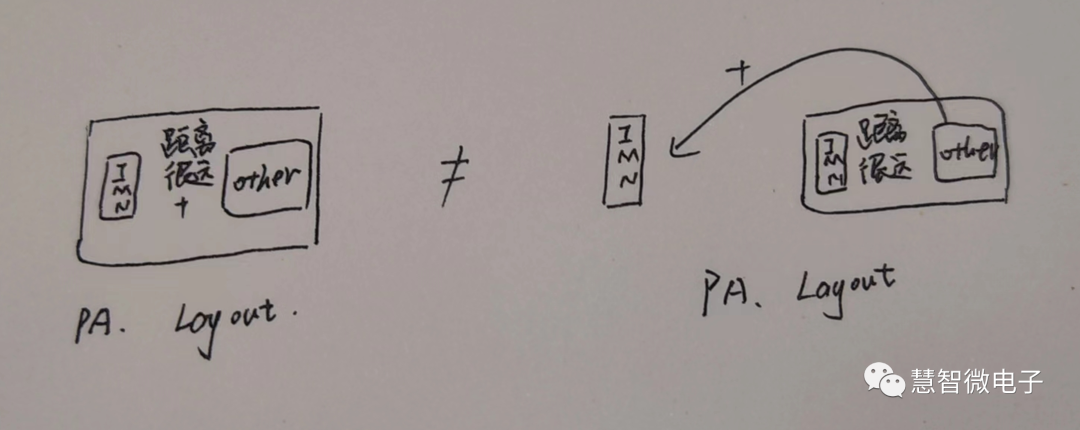

Q:向大家请教一个ADS版图的仿真的问题,这两种情形仿出来不一样是为啥呀?

A:放在一起EM仿真和单独放不一样?

Q:是的

A:如果距离很远,查一下port,用direct模式,不要用TML,如果还是不一样,查一下地,看看两种情况的共地。

Q:好的好的,谢谢大佬 ,明天上班看看。

02

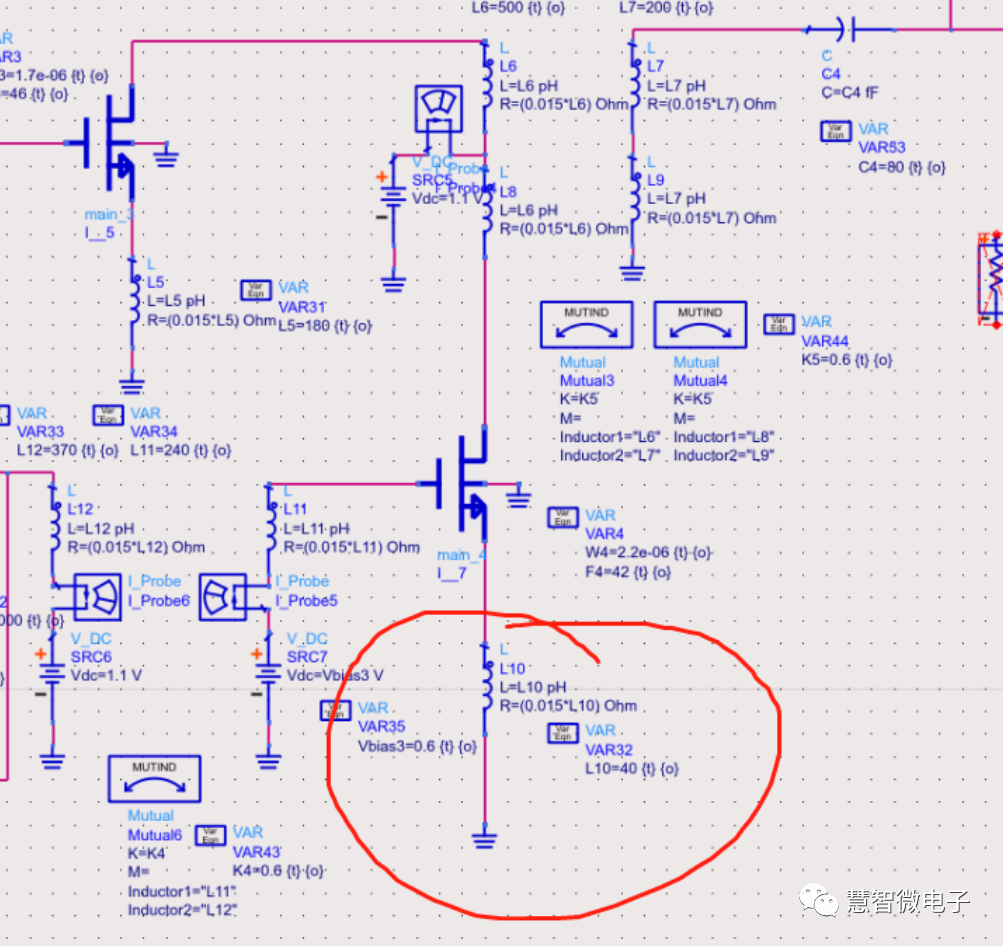

有关晶体管寄生容感去嵌入后Loadpull的讨论

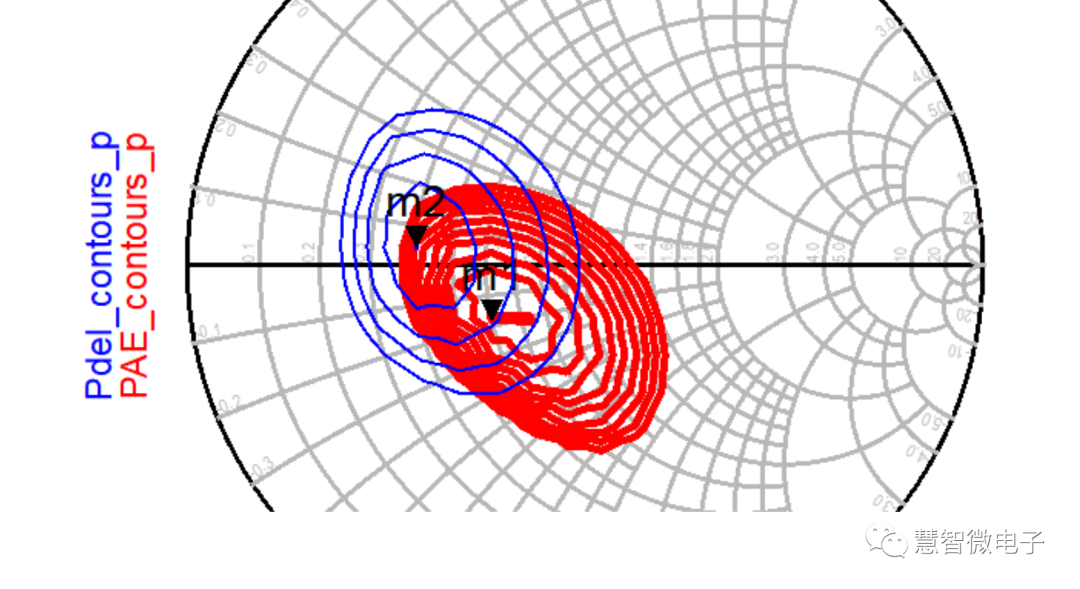

Q:请教各位大佬们一个问题,把晶体管漏极寄生电容和电感去嵌以后做负载牵引,功率圆中心在实电阻处,但是最大效率圆心不在这个位置,这个是为什么呢?

A:这个看你有没有去嵌干净,假设你去嵌干净了,把输入和输出的所有谐波阻抗(到3次)都设成0,再看看。

Q:输出谐波阻抗设置可以短路,但是源阻抗设成短路,好像HB仿真会报错。只设置输出谐波阻抗短路,但源阻抗谐波开路的话,两个圆心比较接近。

A:换个问法,晶体管的最佳功率点和最佳效率点不同,是由管子漏极的寄生电容引起的吗?

Q:对,就是这个问题。

A:我觉得你的这个做法可能不能验证,管子内部的这个寄生电容是非线性的,跟驱动功率有关系,你去嵌的做法是一个线性的操作。

A:不是,你想想,最大输出功率的时候,你看的只是基波的功率,这个时候你没管谐波,但是最大效率点,你是用基波功率除以总功耗,其中总功耗包含了DC+基波+谐波。

Q:如果去嵌的模型是饱和功率下提取的,那在这个驱动功率下负载牵引的应该就可以吧,而且谐波阻抗都短路,目前是牵引出来的最佳功率阻抗与理论计算的Ropt差别比较小?

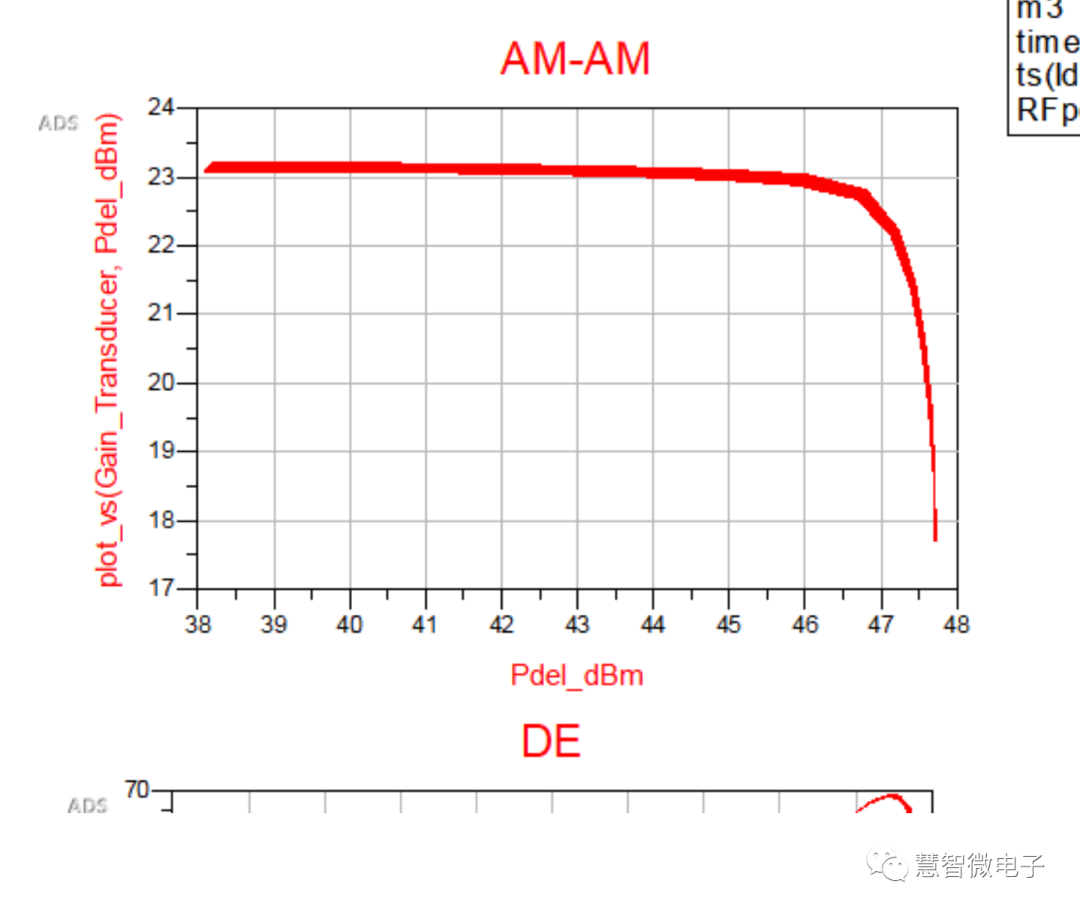

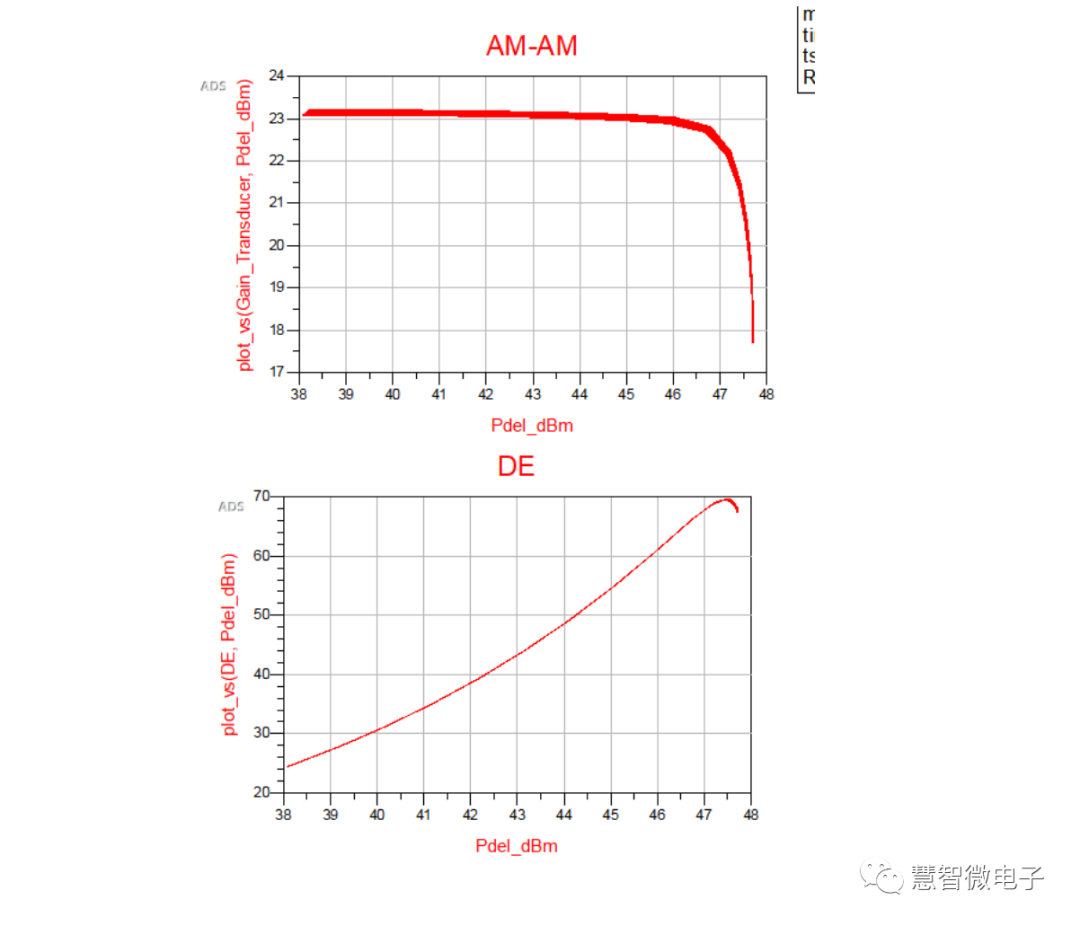

A:稍等,我最近在做一个项目,给你看看我去嵌的效果

我把输入和输出的频率部分(就是电容和电感)全部去嵌掉了,上面的图是我从100M扫描到8G的AMAM曲线。

可以看不管是功率还是增益,跟频率没有关系,这表示你的去嵌去的是正确的,就是把管子频率部分去掉了。

Q:输入和输出的寄生去嵌之后,最佳功率点和最佳效率点是接近的吗?

Q:那在实际设计中有什么想对有用的电路结构可以消除掉管子的频率部分吗?

A: 看这个图再加上我上面对于谐波部分的解释你就知道是不是一样了

Q:懂了,谢谢。

Q:再请教一下,这种非线性的电容,去嵌方法是什么?

A:去嵌的电路,比如GaN,可以找一篇管子建模的paper看看,里面有现成的电路结构。对于非线性部分,这个其实就要分析和取舍,比如GaN PA,其非线性电容分为几部分,分别是Cgs,Cgd,Cds,这部分可以分为两部分提取,一是在冷管情况下提取,比如是C0,冷管提取有一个好处,就是可以避免管子自激。

剩下的就是非线性部分,就要在谐波仿真里面,将C0+X,将X作为一个扫描变量来扫描相关的参数,比如Cgs+X可以侧重于小信号增益,Cds+X可以侧重于输出功率,等。

对于GaN而言,其X并非是一个持续变化的量,具体可以参考变容二极管的电容随电压变化曲线,有一个拐点,即突变点,突变点前后变化剧烈,而突变之后变化并不剧烈。当然,有源部分的参数提取没有准确一说,因为影响因素太多了,功率越大的管子提取越费劲,可以研究一下。

Q:去嵌的目的是啥呢,方便后续设计吗?

A:就是做宽带的时候比较好选阻抗点,比如输出阻抗,其变化的由两部分,一是R,不同的R决定了不同的性能,二是频率部分,电容和电感,频率部分决定了不同频率的阻抗,在做宽带时不好用Loadpull选阻抗点,可以做参数提取,变化的是R,不变的是频率部分,就比较好匹配。

Q:不好意思,lgen是指die的哪个位置?

A:Current Generator。

Q:不好意思有个疑问:去嵌的目的是为了宽带时选择阻抗点,但我理解,这个频率部分其实是不消耗能量的,它只是周期性地吸收和释放能量,所以我原本会觉得做宽带匹配其实就是通过对匹配网络的设计让匹配到的阻抗实部是Ropt,虚部在0附近就行的,如果我这样理解没什么问题的话,那好像也不需要去嵌?那去嵌是如何帮助选阻抗点的呢?

A:这个问题如果从头来解释比较长,一个小反问,你说的没有错,确实是去掉虚部留下实部,那咱怎么能知道我要去掉的虚部是多少,要留下的实部是多少呢?

Q:虚部有影响,从时域上看,虚部就是决定电压波形和电流波形的相对相位。

A:我这还有一个疑问,我的理解是电阻的响应随频率的变化不大,电容得响应随频率变化大,跟您提到的方法刚好相反,是因为电容的特性已经由外部的去嵌电路抵消了吗?

Q:对,在外围电路加一个负的拓扑就可以抵消了

A:感谢老师。

Q:PA这个东西挺深的,从材料到数学模型到物理模型到实际应用(结构+热处理等),基本上就是一个射频系统,有很多问题还学不明白,共同探讨,不存在老师一说,嘿嘿

A:请教下,宽带不好用loadpull选阻抗点是什么原因,带内不同频点load出来的阻抗很发散吗?

Q:数学公式上阻抗是由实部+虚部组成,虚部的值就是电容和电感随频率而产生的阻抗值。所以同一个电容或者电感,但是频率不一样,阻抗就不一样;电路角度来说,就是一个电阻R与电抗Z并联或者串联,而Z是随着频率变化,所以你看到的阻抗就是随频率变化,个人理解。

A:请教个问题,balance PA的架构,对二次谐波的抑制有什么利好吗

Q:好问题,用时域信号算一下,看看二次谐波的相位是怎么变化的。

A:谢谢,还是不太理解为什么做宽带的时候,变化的实部R,而频率部分不变。去嵌以后是去除了频率部分,而得到一个在实轴上的值。那么这个时候,实部随什么变化呢?

Q:额,我说的这个变化是你根据你的需要选择R,比如你想选高效率,或者高功率,或者高功率,这个是根据你的需要做选择,站在你的角度来说是一个主动变化,你要求它变。

A:哦,这样理解了,自己去trade off ,去嵌后,排除虚部带来的随频率的阻抗旋转,其实你就是选定了一个中意的实部了,然后来做匹配。

Q:好解释。

03

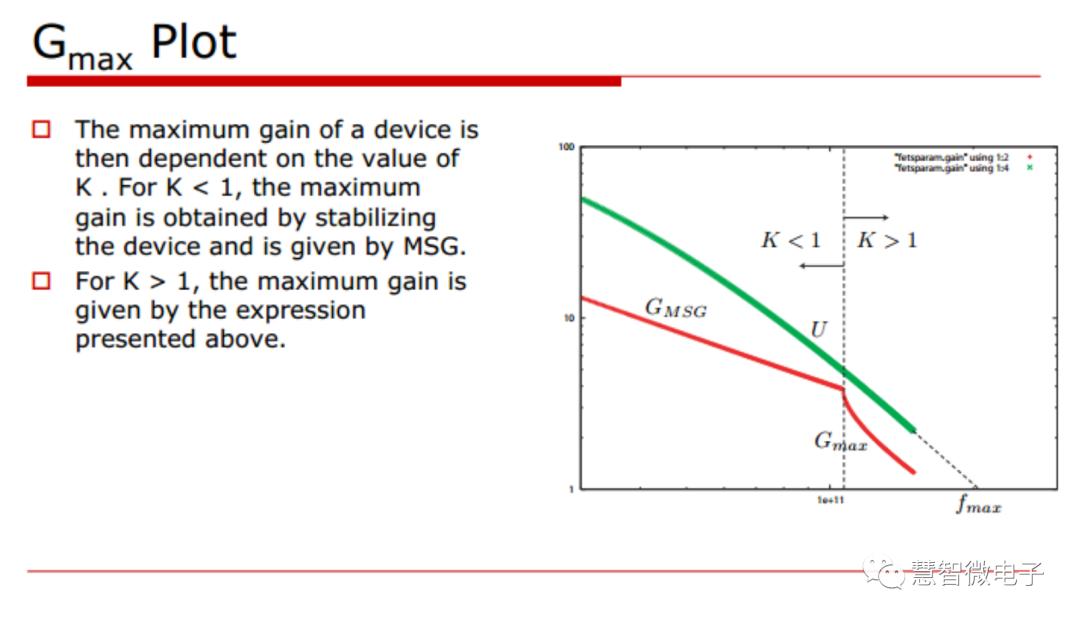

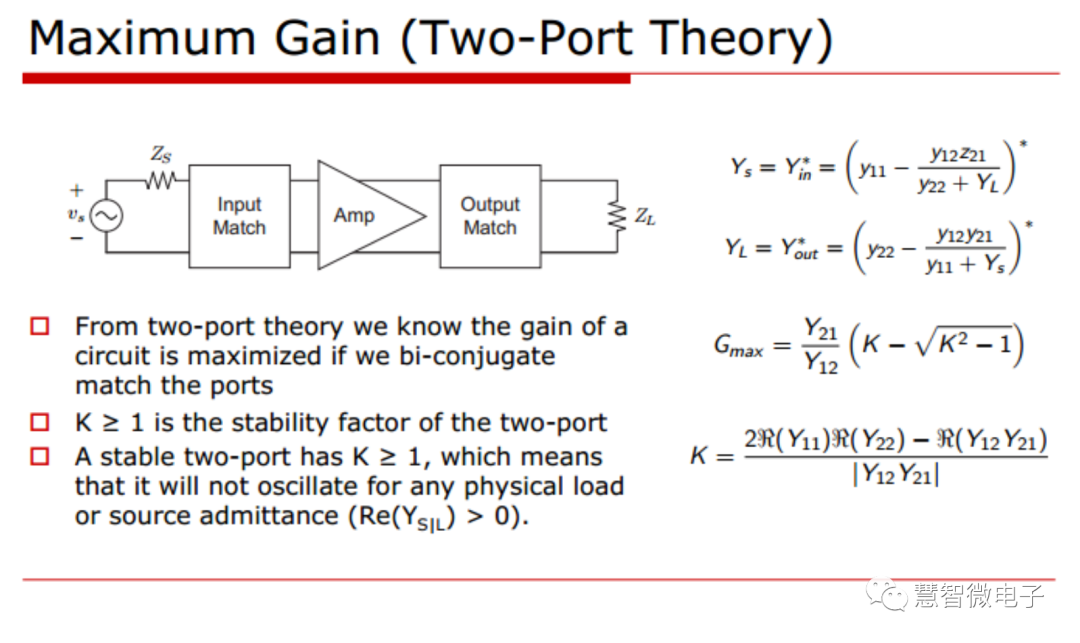

有关Gmax转折点的讨论

Q:请教一个基础问题,为什么Gmax会有一个拐点?或者谁Gmax的的表达式是什么样的,好像是文献及教科书,还是仿真,都是有这么一个拐点,一直不同明白为啥。

A:MAG和gMSG的分界点。

Q:就是说这个曲线是两条的重叠?

A:可以看一下ISSCC2020-ShortCourse2

Q:豁然开朗,谢谢你。

04

有关TFR电阻加工误差的讨论

Q:关于HBT中 TFR 电阻加工误差请教一下群里大佬们

1: TFR加工的时候阻值误差主要来源于长宽厚(浓度) 这几个因素中的哪一个,还是随机的?

2: 在一张Wafer上,一颗小的die上,die上面的TFR电阻偏差,是往一个大小方向偏差的,还是有一定的随机性。

A: 1.宽度和浓度,建议用3um以上宽度TFR,2.中心值上下偏差,不同foundry不太一样,三安一般+-3ohm内

Q:非常感谢!

05

有关SMA接头打螺纹胶的讨论

Q:请问各位前辈一个工艺问题,有在SMA接头上打螺纹胶的吗?有必要打吗?

A:因为SMA内部是聚四氟乙烯有一定”弹“性或不同材质间的差异性,不像2.92、2.4mm是空气介质;在需要经常振动的产品上最好在上完力矩后点些中强度或低强度的螺纹胶保险一些。

Q:谢谢。

06

有关ADS优化滤波器时的算法讨论

Q:请问ADS里,优化滤波器的时候,用那个算法比较好呀?

A:我一般遗传再模拟退火

Q:這樣比較快嗎? 我都放退火而已? 有相關資料可以分享嗎? 謝謝群友。

A:没有比较快,只是习惯了,或是路径依赖吧。

Q:能否分享一下算法?

A:直接用遗传算法会不会很慢才收敛,是不是反过来反而会快些。

A:我觉得模拟退火后是全局最优,所以把这个放在后面。

A:应该都有风险落在局部最优,遗传算法的结果应该不会相对前一个结果恶化。

Q:我試了這個 結果不能跑 其他的算法才可以 請問是什麼原因?

A:里面没有一种遗传退火算法么?只听过这种方法做过波束赋形。

07

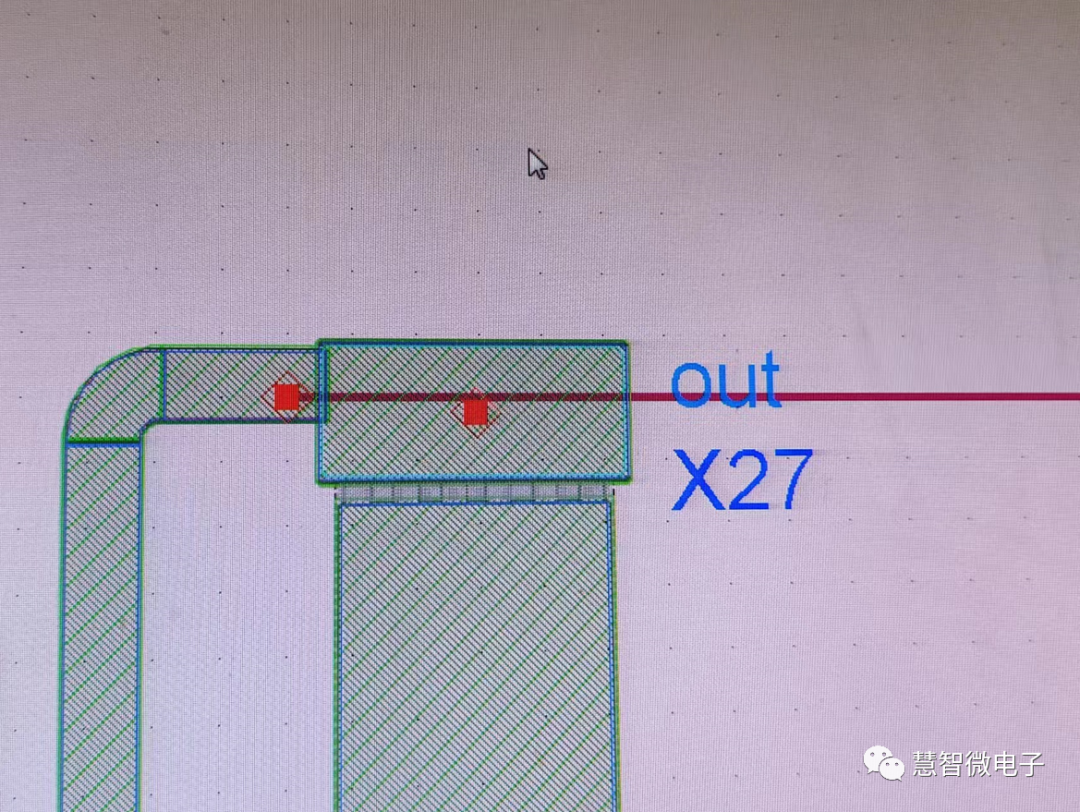

有关ADS仿真中线连接不上连接点的讨论

Q:请问有人见过这种wire连不上红色格点的情况吗?怎么解决的呢?

A:Ctrl+E.

Q:OK.

08

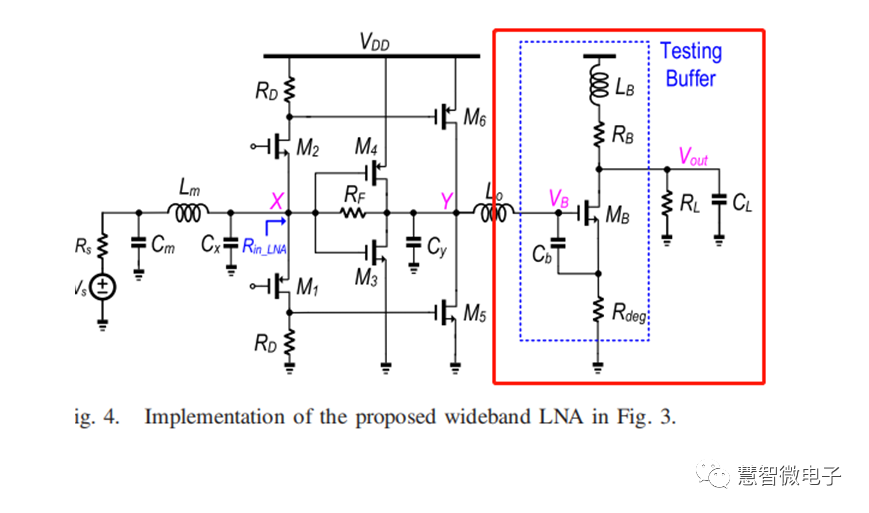

有关电路中增加测试buffer级的讨论

Q:请问大家,为啥在好多文章中看到低噪放的末端需要加一个testing buffer

A:方便测试啊,又不影响性能。到时候直接去嵌。

Q:话说怎么方便测试啊?

A:不然核心电路还要去搞输出匹配啊。有了test buffer以后就不用做了。测完再把这个buffer剪掉就是你电路的性能了。这不是很方便嘛。

09

有关噪声贡献仿真的讨论

Q:请问大家,cadence或者ads可以仿真电路某个部分的噪声贡献吗?

A:cadence的noise summary可以看到噪声贡献。

Q:恩恩,这个之前有查到过,但是不知道在ADS里咋仿因为管子都链接到ADS里了。

ads不知是否有类似仿真噪声贡献的设置?

A:可以,你在ADS help去搜Noise,就很多类型的。

Q:ADS 感谢老师!

10

有关射频放大器中馈电电感的设计

Q:大家在设计LNA、PA的时候,馈电电感的取值是如何让选取的?是不是越大越好?一般PDK中的电感设计不了太大。大家的biasing network都是咋设计的,可以交流交流

A:满足你应用频段的RFchoke就行了吧,面积越小越nice

Q:一般RFC的在工作频段的阻抗要求多大呢?我看有的书上写的是10*Zo,至少500欧姆,这个高阻的RFC一般的PDK中实现不了,电感值一般会偏小,电抗较低。

A:是的,所以很多单片放大器很多要求片外加额外的rfc电感。

Q:所以在设计中,如果要把偏置电路集成到MMIC中需要牺牲一部分性能为代价?

A:我觉得这要看拿什么对比了,你做自适应偏置电路,是对你电路的pvt性能产生优化作用的,你拿理想器件看可能感觉牺牲了性能。

Q:自适应偏置一般是用在栅极的吧,漏极的偏置一般使用RFC的吧?

A:是的,习惯上说偏置一般是指栅极的偏置电压

Q:好的,多谢。

11

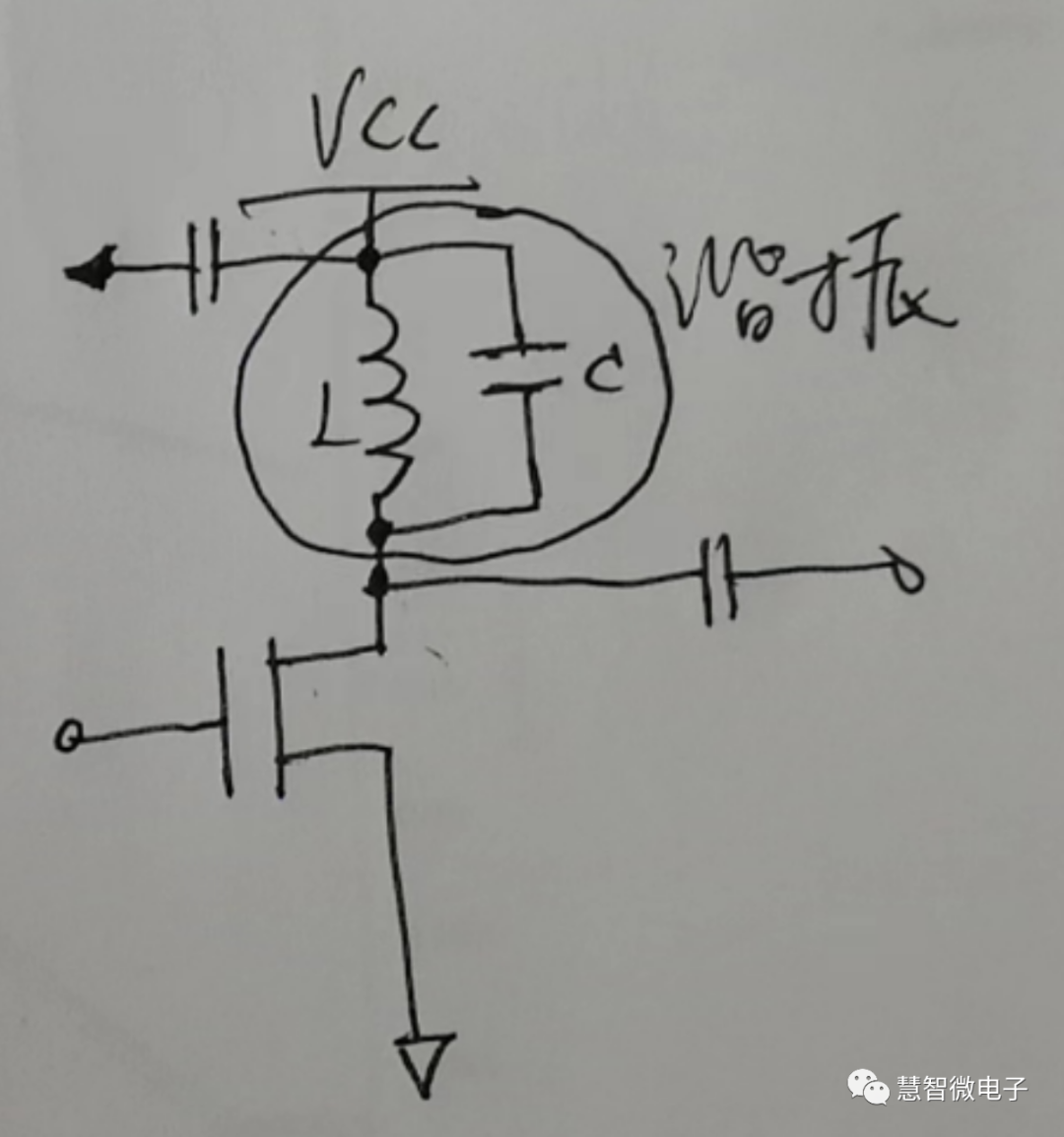

有关馈电电感的再次讨论

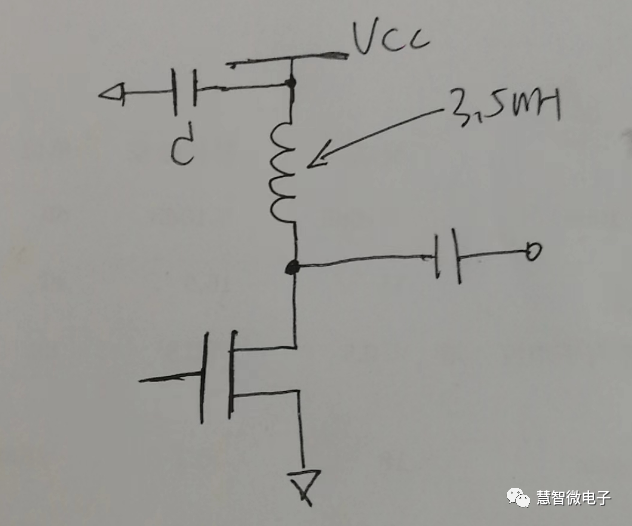

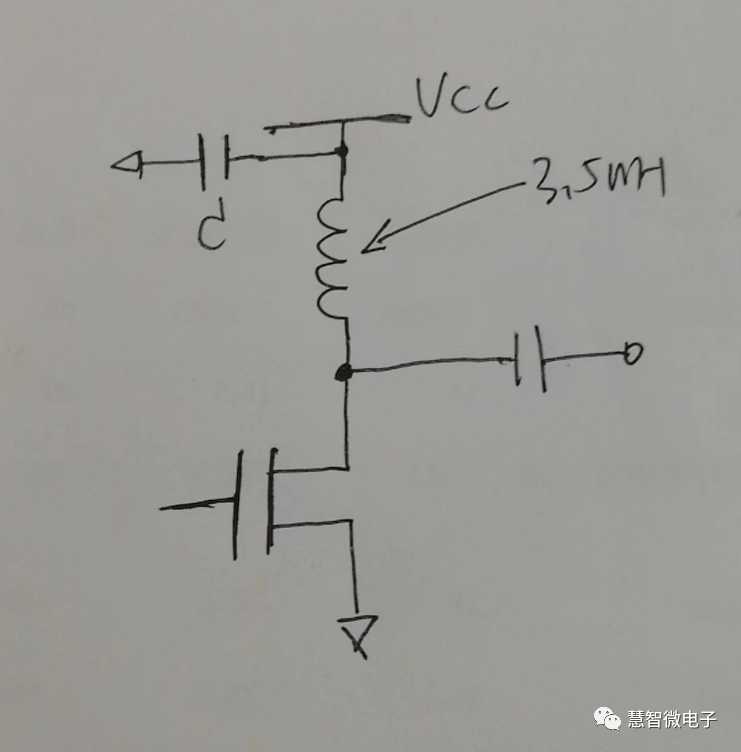

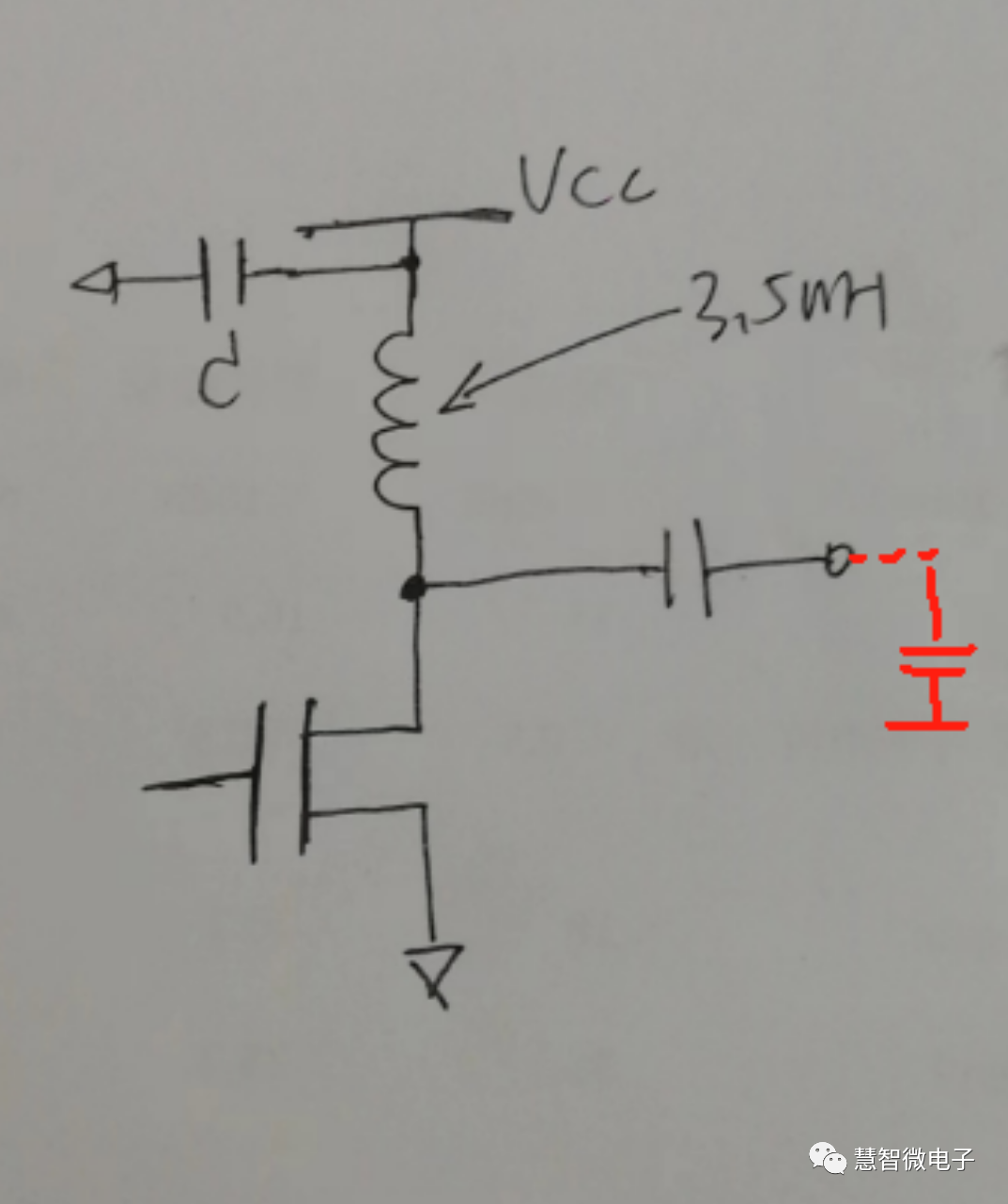

Q:有人说这个3.5nH的电感是负载电感,不是馈电电感,如何解释?这个电感和哪个电容谐振呢?实际的负载阻抗是LC谐振阻抗值,不是电感的值。有劳各位,给解释一下,我被这个搞蒙了

《射频与微波晶体管放大器基础》书本上是这样的

A:一般这种两种作用都有的吧,参与匹配和choke。

Q:但是实际上,在低频段,如果把馈电电感集成在MMIC内部,一般PDK都不会有太大的取值,或多或少都有RF信号的泄露。

但是我看有一个例子。2.4GHz,漏极馈电电感取值3.5nH,有老师说这是参与谐振的LC电路,属于负载电感。但是不知道和哪个电容C谐振

A:尝试回复一下:choke电感的作用是通直隔交(不会让交流信号耦合到电源),理想情况下需要足够大才能达到效果(ads里model的10uH左右?)

但是因为我们现在都会存在bypass或decouple电容作为射频地,所以对choke电感的要求降低了,使其可以使用较小的值同时可以提供匹配的效果(uH级别并联电感在smith圆图上是基本不动的)

说到谐振网络:要看你是想要带通效果还是低通效果,带通可以在choke上并电筒,低通可以输出串电容(该电容还有隔直的效果)

A:我觉得不可能完全隔绝射频信号泄漏进偏置电路的,或多或少都有

Q:就是这个电路,2.4GHz,取值3.5nH,如果计算电抗只有53Ω,有个老师说是谐振电路,但是不知道和哪个电容谐振。说这个电感是负载电感

A:这个要具体分析,理想情况是输出串的电容和这个3.5nH,非理想情况会有段走线到Vcc,这个时候bypass的C会和3.5nH谐振(因为不是理想地了)。就是有两个谐振点。

A:会不会是和漏端的所有等效电容。

A:实际上面那个C和VDD相连,是隔绝从VDD带来高频干扰的吧

Q:C是bypass电容。

A:只有一种可能存在谐振,后面你有负载电容,不然的话就是一个dc馈电

Q:后面直接接50欧姆负载了,是不是MMIC直接馈电的话,都是利用谐振原理设计的,PDK中没有那么大的RFC,在低频中,如L/S,高频就可以用微带线了。

A:會不會是跟cds 諧震呢?是有人用並聯電感去消除cds 影響。

Q:应该不单单是Cds,Cds没有那么大。

A:“是不是MMIC直接馈电的话,都是利用谐振原理设计的,PDK中没有那么大的RFC” 一般用tank搞个几百欧的Rp就够了。

12

有关放大器退化电感的讨论

Q:大家好,请教一个问题,电路里的高频增益与源退化电感有很大关系,调整的过程中发现源退化电感越小,增益越大,但现在这个电感已经比较小了,请问各位大神有无好的办法?

A:源退化电感是为了噪声么,如果不能直接去掉,考虑使用其他类型的放大器?

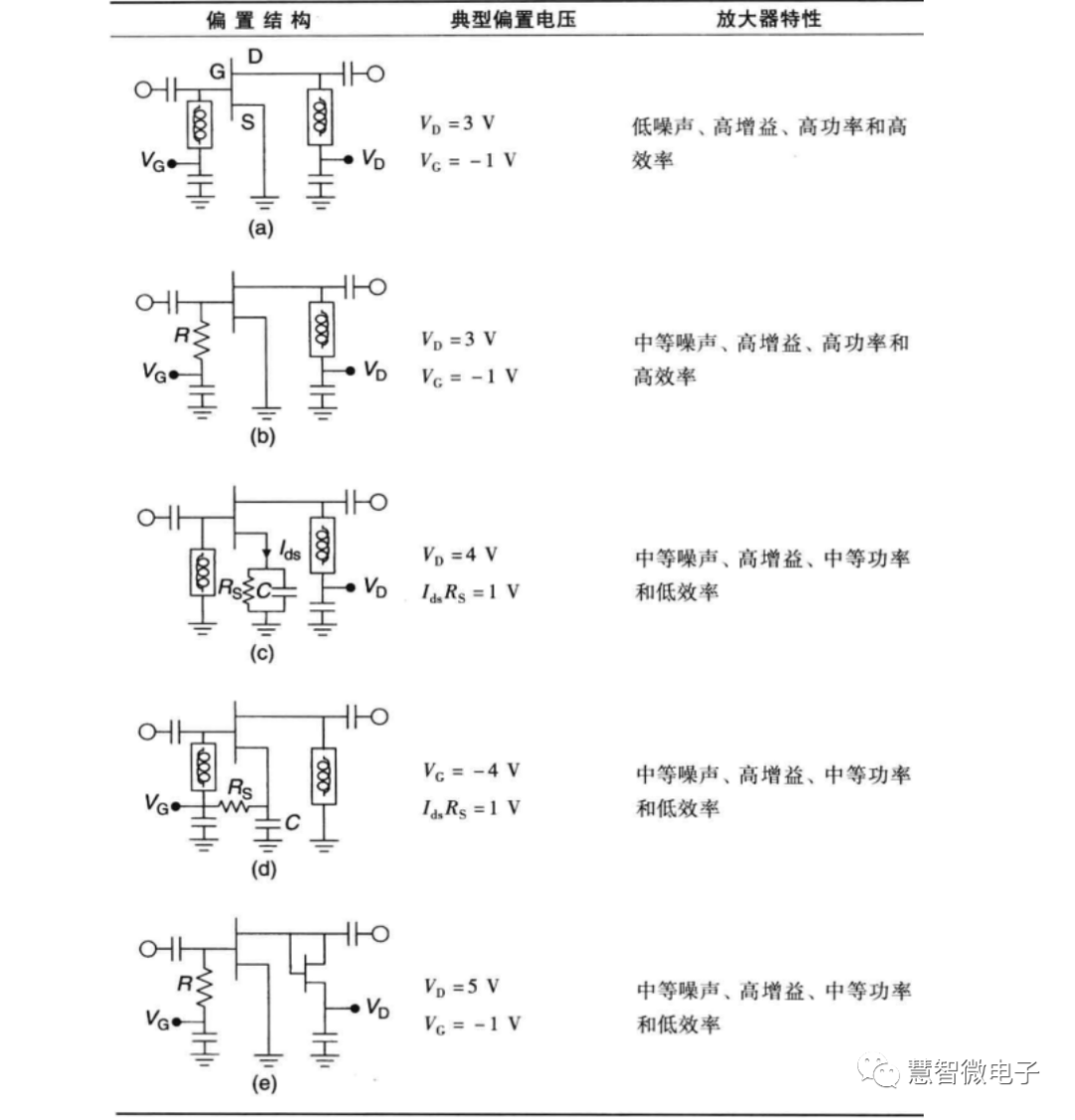

Q:这种?

A:是的,现在用的大都是这样的。

Q:谢谢大家。

13

有关Doherty的非对称设计

Q:如果Doherty中辅助功放电流是主功放的三四倍了,回退功率点大于6dB了,有什么坏处吗?

A:这不就是非对称的doherty吗?很正常吧,因为现在的调制信号也不止6dB了,8或者9的papr都有,就需要1比2或者1比1.5了

Q:我看到辅助功放电流大一些线性度会更好,但如果太大会有缺点,不知道是什么缺点。

A:符合你设计的要求就好,因为peak大部分时间也不会接近饱和。

Q:谢谢。

14

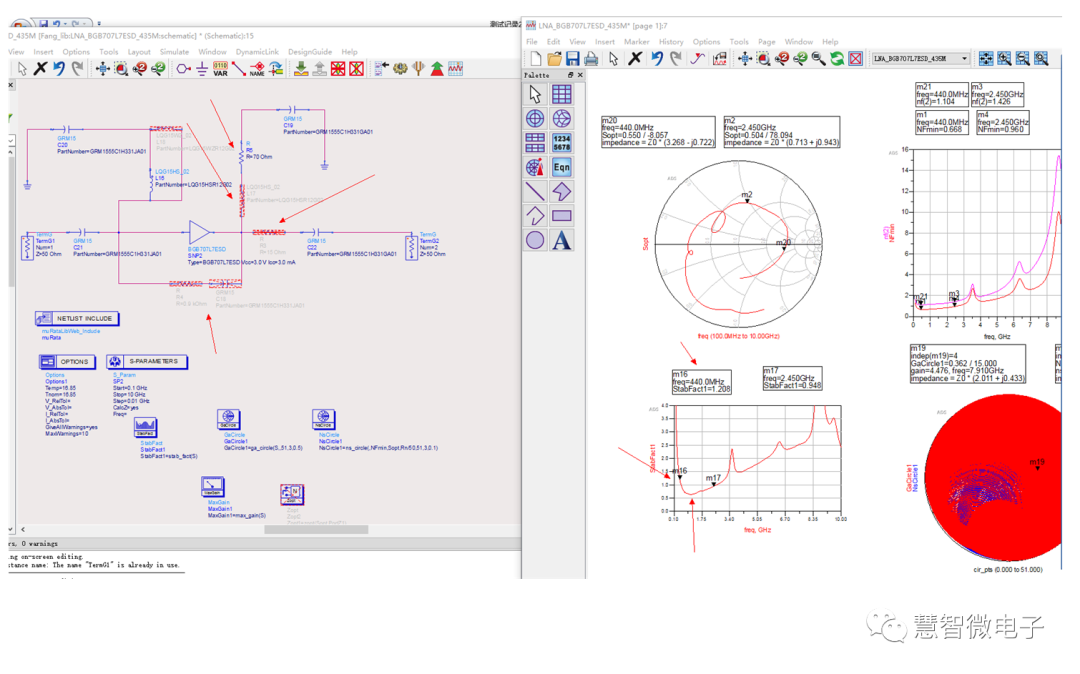

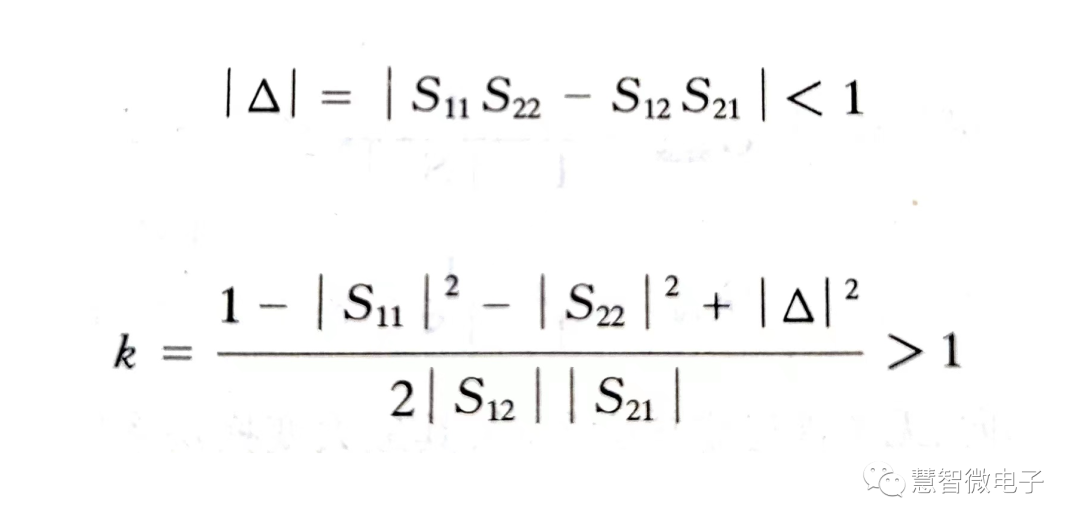

有关LNA稳定性设计的讨论

Q:请教一下LNA提高稳定性的方法,如果不用负反馈,要通过偏置和输出串联电阻来调整的话,怎样才能把图片中最低点调到大于1,而且工作频率433M的K值又不要太大了,1.1左右。现在就是如果全频段大于1,工作频率433M又太大了。

A:加个滤波器,把gain卡在范围内。

Q:这样啊,滤波器不是外围的吗,会影响LNA的K值?

A:如图:

A: 滤波器如果是无穷Q 的, 不会改变K。 如果改变是因为gain 降低了, 其实和反馈或是其他减低增益的方法没有本质区别。

Q:降S21来提高稳定性? 那我还是乖乖用负反馈吧,本来想用偏置和输出电阻来提高K值的,结果K值工作频率太不平坦了。

A:如果不想降低增益, 提高K 值。 里面的电路设计需要修改, 主要是看到反馈dB(|S12|) 是不是够大 > 30dB。 如果够大,但是K 还是有风险,检查一下电路中有没有类似 oscillator 的架构,找到的话,把它毁掉。一般的de-bug 就这思路。

Q:试了一下负反馈,K值是好平坦,但是NFmin由0.6变成了1.0了。

Q:负反馈就是回引入噪声,想问一下,k值平坦度有什么影响吗?

Q:不是大于1就可以了?

Q:想问一下,稳定性因子需要在全频段大于1吗,只在工作频段大于1可以吗

A:全频段都需要。其他干扰信号不一定在工作频段内。

k和增益相互制约,要做高效率肯定要限制k不能太高,在1附近能出管子最大性能。

Q:我用的英飞凌这个芯片都是设计全频道大于1,只工作频段会不会有风险?

A:K>1 不是干扰的担忧, 主要是带外阻抗的担忧。

Q:带外阻抗是指的是??

A:人们引入K 的概念是想解决无条件稳定的问题,无条件是指 我们不知道input 或是 output 的阻抗是啥,所以就说那就是整个smitch chart 的任何一点吧。

Q:不都是看Mu值吗?

A:是的,mu 更好, 历史上也是现有K+delta, 后来才有的mu 。K 值 >1, 只是告诉我们 无条件稳定,但是 k=2 和 K=3 比,我们不能说K 越大 这个电路就稳定。而mu值确实可以这么下结论。

滤波器无论是放在前面还是后面, 只能保证 带内50ohm,带外是啥阻抗,没有人控制的了,一般在smith 圆外侧。但是还是不能改变K ,因为它自己的计算就是整个smith 圆。

Q:“人们引入K 的概念是想解决无条件稳定的问题,无条件是指 我们不知道input 或是 output 的阻抗是啥” 这个是啥意思,那如果LNA在板子上,前后都有固定物料,那是不是就带内K大于1就行了。

A:他的意思是不管接什么阻抗都是稳定的,K才全频段大于1,其实很难知道,所以K>1 是现在的标配。

Q:有一个问题,就是稳定性看的一般都是小信号,如果设计的是class c的pa,看小信号的话会不会没有意义,因为管子都没开启。是不是还要看大信号仿真。

A:直接用ab类的稳定网络。

Q:你好,稳定系数看全频段,是指带宽内的所有频率,还是说我0-100G这种所有频率?

A:0-100这种

Q:看你们之前的聊天,说还要看mu,我没看过这个,就大概看下K,有啥影响吗?

A:两个都看。

Q:学到了,谢谢几位的解答。

15

有关谐振腔带外凹点的讨论

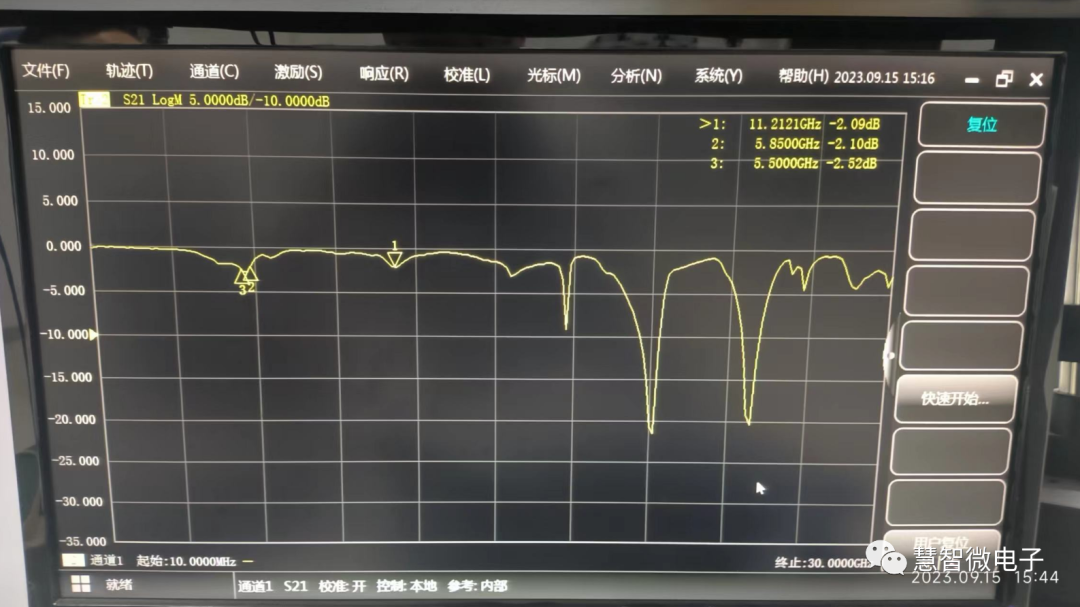

Q:在测量谐振腔的S21参数时,为什么在第一个谐振坑11GHZ前还有一个坑,有哪位大佬知道吗?

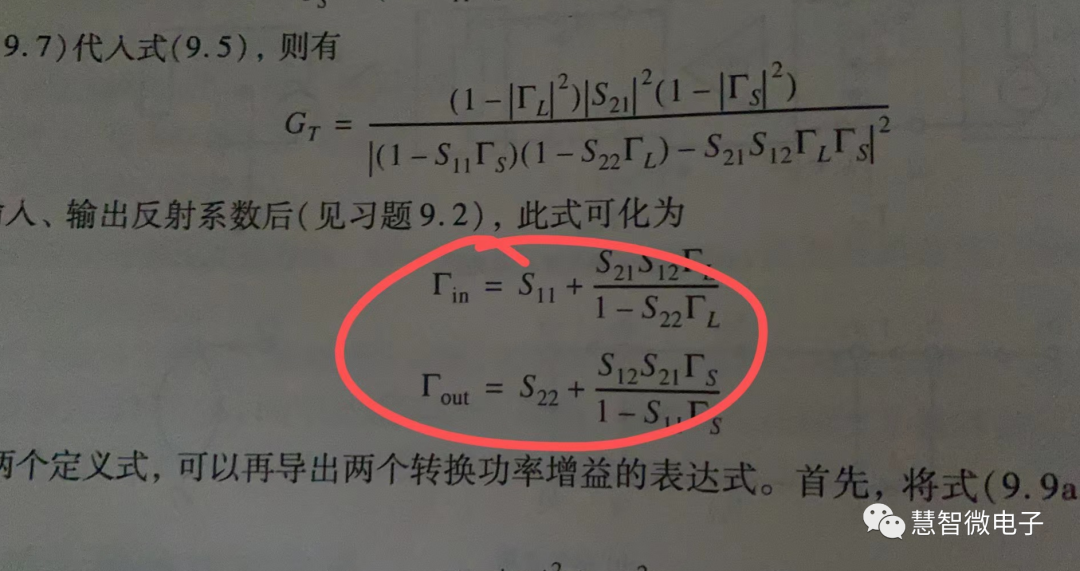

Q:网络的S参数是固定不变的吗,还是随源和负载的不同而变化呀?有哪位好心人解答一下吗?ADS中仿真出来的S11是理论的S11,还是输入端反射系数呀?

A:应该是反射系数,会随源和负载变化的。

A:S参数是会和负载源的不同变化的

Q:我的理解是只要这个网络做好了,他的S参数就固定不变了,因为S参数是在匹配情况下的值,应该是唯一的。但是为什么仿真的时候会随着变化呢?

A:有截图吗?是怎么个变化?按道理,只要你的网络做好了,负载,源这些都没变,S参数是不会变的。

Q:现在手里没图

Q:反射系数和s参数不是一回事吧,

A:只要你的隔离度做的好,输入端的反射系数就大概等于S11。

Q:哦哦,谢谢各位了

A:嗯,反射系数和S参数相互之间可以换算的,是与源或者负载阻抗相关的。

A:s参数是某个电路在特定条件下(源端/负载匹配)的特性;反射系数是此电路在实际情况下(源端/负载不一定匹配)的特性。

A:是的 我们常认为测试的s参数 是在负载端匹配下,也就是gamma L 等于0。

Q:那么仿真软件测出来的s11/s22就是输入/输出端口实际的反射系数,并不是网络本身的s参数特性?我看过一篇帖子说s21测出来的是电路的实际增益,maxgain才是网络的S21

A:仿真某电路的时候也是要50Ω负载的,这个实际增益也是在仿真条件下的增益,实际上源/负载阻抗有变化,这个增益就会和仿真有变化。

Q:好,谢谢老师。

16

有关LNA设计中RC并联电路作用的讨论

Q:有个问题想请教大家 LNA版图上经常在源到地那里挂RC并联电路主要是为了什么?跟直接电感或者电阻地有啥区别?

A:电阻R起到负反馈作用来稳定直流工作点 电容C的话在高频时旁路信号 从而不起到负反馈作用 就不会降低增益 感觉有这方面因素哈。

Q:感谢各位解答。

17

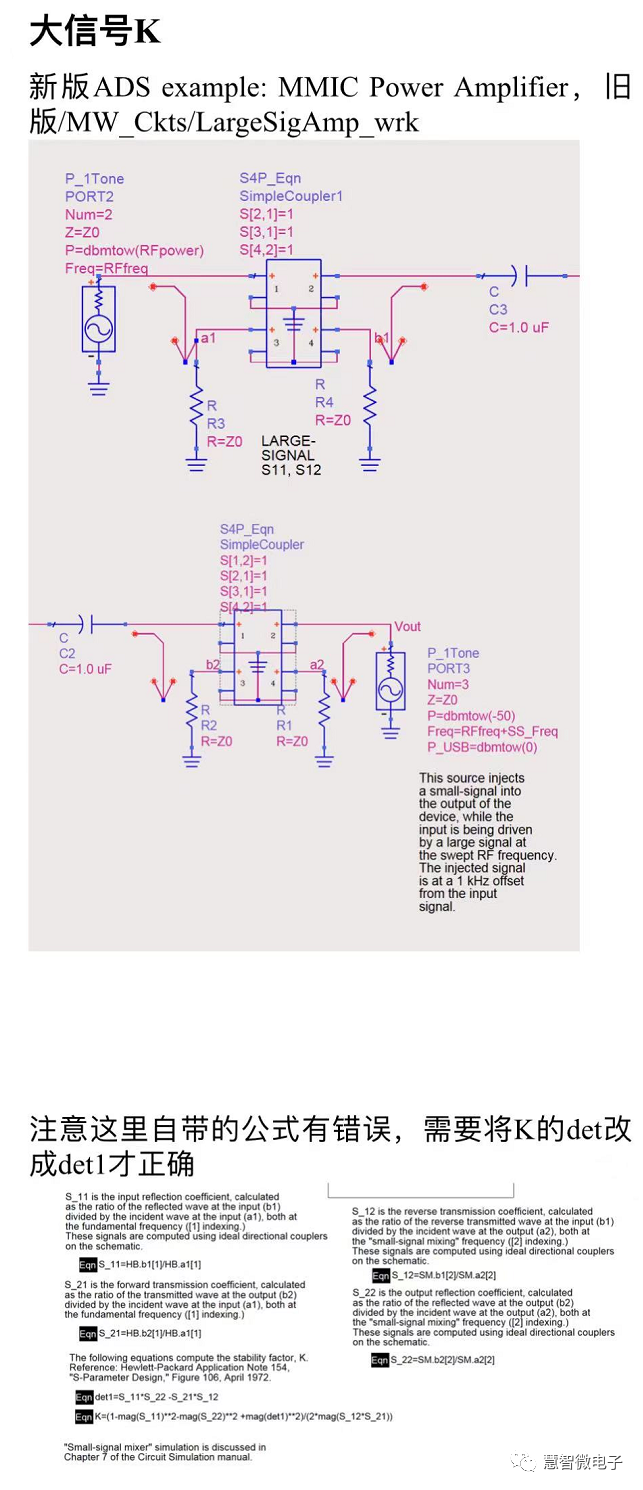

有关PA大信号稳定性的讨论

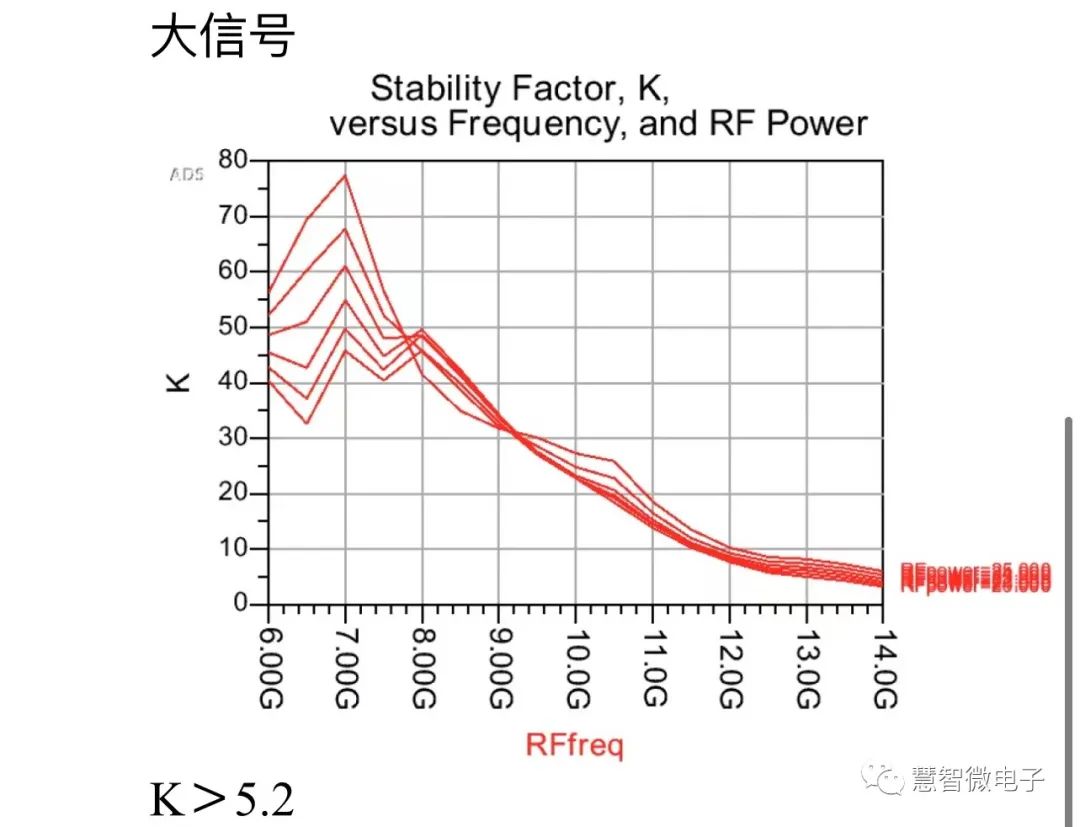

Q:大家好!有个关于PA放大器的设计当中,关于稳定性的考量,大家通过什么去进行设计的。通常来说一个是小信号的K,u值;那在大信号仿真上面呢?

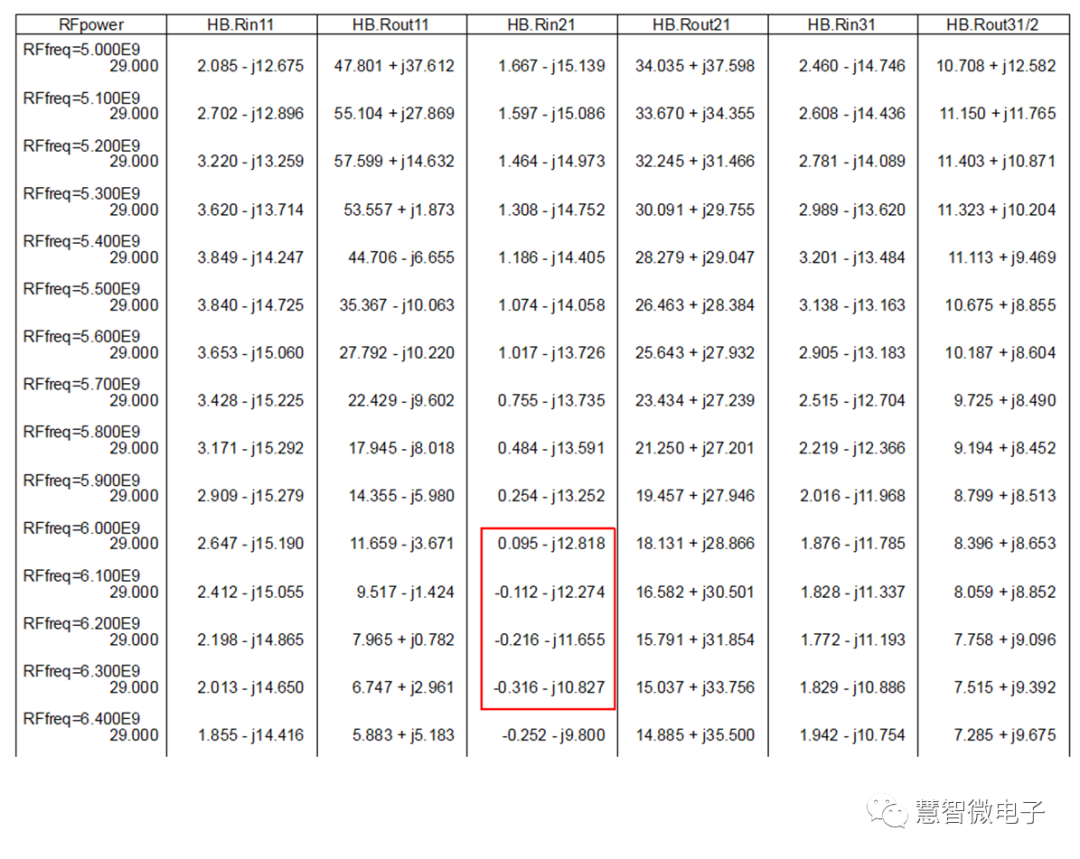

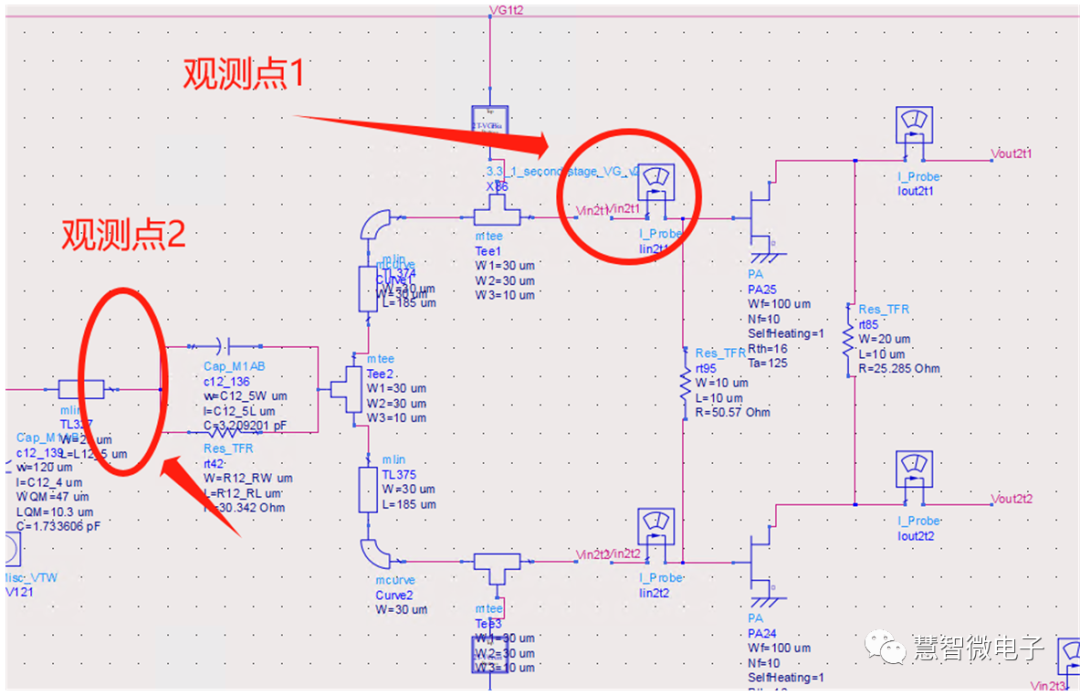

我们在整版原理图的大信号仿真上,在单管的输入输出添加电压表和电流表,通过公式Rout=Vin[1]/Iin.i[1]来看管子输入输出的阻抗,观察大信号阻抗来判断其稳定性以及阻抗匹配等。发现在管子的输入端,在某些频点会出现负阻的情况。

一个是,不知道这种看大信号阻抗的方式是否能用来判断功放的稳定性。另外一个就是,大信号的稳定性,大家是通过什么方式去进行考量、验证的?

A:可以通过瞬态看,看看bias上有没有非理想的波形。

A:最近设计的pa流片回来也发现白激严重,仿真的时候u在所有频段是大于1的。最后实测发现是流片的电容整体偏小,导致Vcc的并联耦合电容偏小从而导致自激。

A:有大信号稳定性的模版,找一个大信号仿真的模版 然后看这个大K值。

自激目前来说,还要看下级间稳定性,用WSprobe或者这个SProbePairT模版,我做了两个PA都没震荡,看这个是没问题的,也和别人询问过经验,也是用这种方法。

Q:那个我们敲公式看的那个负阻 其实参考意义不大的是嘛?

A:也有这种说法,不过这个模版公式里好像就是用这个看的。

Q:好的 我们去check一下。

A:以我观察,pa尤其是基站pa还是基于测量的技术,例如loadpull确定最佳阻抗的方法,包括稳定性,最终还是通过实测来定论的,因为管子的模型还不够准确完备,各种脉冲信号调制信号的响应并不完全正确。设计时,稳定性还是以小信号参考为主。比如k值留有余量,驻波小于0,带外无高增益,无阻抗突变等等。小信号没问题,我感觉能保证90%的pa是稳定的。但是还是有10%的pa在特定场景下,比如低温,双音脉冲或者其他特别的信号条件下,蹦出一些杂散信号出来,需要具体问题具体分析的。仿真时,尤其是die输入负阻,阻抗在smith圆图外是不被允许的,意味着驻波大于0,不稳定。一定要通过串电阻或者有耗匹配把阻抗都转到圆内。大信号的稳定性可能可以看看阻抗和曲线amam,ampm是否有突变等等。稳定性我理解主要还是参考小信号。

A:小小补充下,就算厂家能准确测出大信号模型,但实际运用条件和环境变化都会导致管子大信号阻抗和大信号模型有较大差别PA还得是一门优化调试的手艺活

Q:这里我有个疑问就是 我比如我已经采用有耗匹配的方式去进行阻抗的一个转移。

采用有耗匹配对单管的阻抗进行改善,那我后续采用的观测点是用1还是2?这里关于观测点的选择,也可能是造成我们困扰的一个原因之一。

A:一般来说就加在管子前后,如果不是用WSprobe这种,还得把稳定网络加上。

Q:感谢各位老师!

18

有关Doherty功放设计的讨论

Q:大家好!向大家请教一下关于Doherty 功放中Peak路单管调试方法的相关问题。目前,peak功放输入和输出匹配网络的微带线已经确定,用电容调试功放的性能。目前用矢网调输入匹配网络S11<-10dB,然后调输出匹配网络,脉冲信号下调Psat。请问:1.调小信号S11的目的是什么?这个与Peak路开启点有关系吗?2.当输出匹配网络调不动了,目标的Psat没有达到。下一步是不是需要在脉冲信号的情况下调输入匹配网络?然后相互迭代?还是修改Peak的匹配网络,直到满足Psat为止。3.peak路的效率应该怎么考虑?满足什么要求?

A:个人理解仅供参考,有问题欢迎大佬纠错

1.我理解只是调输入驻波,跟开启点没关系;2.输出调不动就调输入,找到合适状态返回调输出,进行迭代;3.peak开启是为了要饱和,一般按设计peak要出到接近最大功率的,这个状态可以不考虑效率

Q:我理解功放管大信号和小信号的输入和输出最优阻抗点不一样。最初调输入S11是为了什么?

A:你们小信号驻波要求多少,对于功放-10应该已经很好了,按说是不太差就行。

调完输出匹配网络之后再去看小信号S11,S11发生了变化,要求我不清楚,调S11<-10之后,直接脉冲调输出,调Psat。

A:peak路要调整小信号下的s22,需要单独接出来看,通过调整offset line保证接近开路点,psat出不了可能的相位合得不好。

Q:目前只调peak功放单管。在AB类的偏执下,调它的Psat。调输出匹配网络的电容,找它的Psat。

A:peak路调s11为了啥 peak.路不是c类吗?

Q: AB类的peak和C类的peak在小信号的大概增益差多少?psat大概差多少?

A:c类小信号没增益,功率看你DPA的是不是对称的 对称一样 非对称 根据回退量可以计算出来。

编辑:黄飞

-

超详细的射频基础知识2022-11-04 3496

-

ARM常用模块与综合系统设计练习题与答案2011-11-29 5203

-

转:ARM知识知多少?经典ARM问答,你都get到了吗?2016-08-02 3113

-

电工知识问答题库2009-07-04 1321

-

电视技术习题集(问答题)2009-07-29 1337

-

路由器基础知识问答2009-08-01 818

-

电池问答题全集(含答案)2009-11-13 2764

-

音源基础知识问答2010-04-01 1151

-

射频基础知识培训2016-09-01 1065

-

模拟电路基础问答题总结2016-09-20 745

-

示波器基础知识一百个问答2016-10-10 656

-

射频电路预备基础知识2021-06-07 1662

-

射频、光纤基础知识2021-06-15 1154

-

减速电机基础知识问答2022-01-07 2280

-

射频与微波基础知识2024-01-16 1972

全部0条评论

快来发表一下你的评论吧 !