FPGA学习-分频器设计

描述

分频器设计

一:分频器概念

板载时钟往往是有限个(50MHZ/100MHZ/24MHZ/60MHZ…),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频/倍频,目的是用于满足设计的需求。

分频:产生比板载时钟小的时钟。

倍频:产生比板载时钟大的时钟。

二:分频器的种类

对于分频电路来说,可以分为整数分频和小数分频。

整数分频:偶数分频和奇数分频。

小数分频:半整数分频和非半整数分频。

三:分频器的思想

采用计数器的思想实现。

例子1:模10计数器

假设系统时钟sys_clk是50MHZ,对应的时钟周期Tclk=20ns,计数器每计数一次需要20ns,那么计数10次需要200ns。

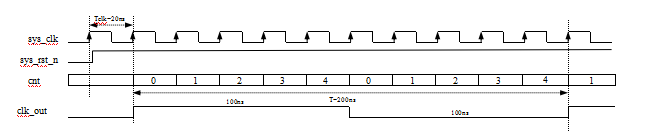

1:整数分频:偶数分频(Duty:50%)

计数器计数10个持续时间为T=200ns,那么输出频率:

F=1/T=1/200ns=10^9/200HZ=5MHZ。

1MHZ=10^3KHZ=10^6HZ

通过模10计数器得到的频率为5MHZ,

占空比:高电平持续时间占整个周期比值。

50MHZ~5MHZ:10分频电路(Duty:50%)

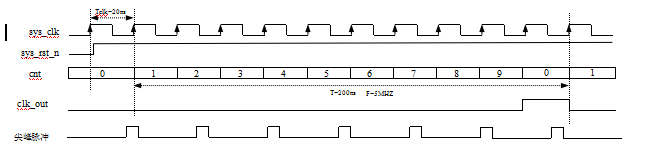

2:整数分频:偶数分频(输出时钟高电平持续系统时钟一个周期:尖峰脉冲信号)

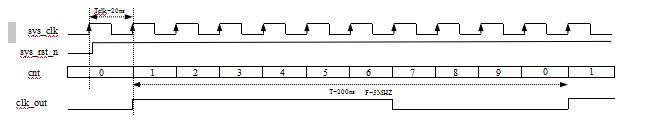

3:整数分频:偶数分频(Duty:60%)

根据上述偶数分频的方式,可以得出以下结论:

Fsys_clk = 50MHZT sys_clk = 1/ Fsys_clk = 20ns

如果Fclk_out = 5MHZTclk_out = 1/ Fclk_out = 200ns

以系统时钟上升沿来时,使其计数器加1,换句话说计数器计数一次需要20ns,当满足200ns持续时间时,需要让计数器计数10次。

那么计数器计数最大值cnt_max=10。

推导公式:cnt_max(计数器计数最大值) = 200ns/20ns = Tclk_out / T sys_clk = Fsys_clk / Fclk_out

4:整数分频:奇数分频

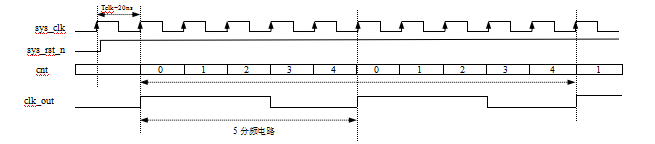

例子1:5分频电路(50MHZ--->10MHZ):Duty=3:2

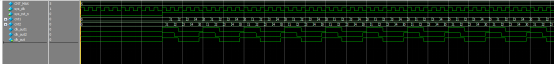

测试3:5分频电路(Duty=3:2)

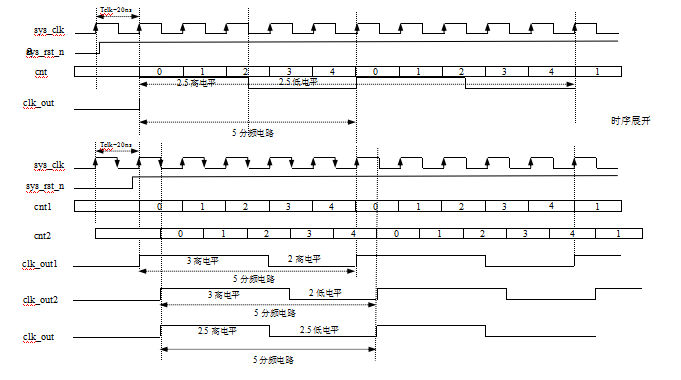

例子2:5分频电路(50MHZ--->10MHZ):Duty=1:1

首先需要设置两个计数器(0~4),第一个计数器以时钟上升沿计数,第二个计数器以时钟下降沿计数,都分别产生5分频电路,且占空比都为3:2,最后输出5分频电路占空比1:1就是由上述两个5分频电路相与得到的。

clk_out = clk_out1 & clk_out2;

如果5分频电路占空比是2:3时,最后输出5分频电路占空比1:1就是由上述两个5分频电路相或得到的。

clk_out = clk_out1 | clk_out2;

测试4:5分频电路(Duty=1:1)

测试5:5分频电路(Duty=1:1)

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-分频器设计

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- FPGA

-

基于FPGA的任意数值分频器的设计2010-04-26 2998

-

基于FPGA的任意分频器设计2014-06-19 23930

-

基于FPGA的通用分频器设计2009-12-19 672

-

基于FPGA 的等占空比任意整数分频器的设计2010-02-22 863

-

基于CPLD/FPGA的多功能分频器的设计与实现2009-11-23 1692

-

什么是分频器 分频器介绍2010-02-05 5325

-

FPGA实现小数分频器2011-11-29 884

-

基于FPGA的通用数控分频器设计方案2015-05-07 5841

-

用Verilog实现基于FPGA的通用分频器的设计2016-07-14 1299

-

分频器有哪些_分频器分类2018-01-10 17192

-

音箱分频器怎么接线_音箱分频器接线图解2018-04-13 122440

-

分频器是什么东西_音箱分频器的结构、特点2018-05-25 16192

-

一种基于FPGA的分频器的实现2021-05-25 1033

-

基于CPLD/FPGA的半整数分频器设计方案2021-06-17 1173

-

FPGA分频器的设计方法2023-05-22 3298

全部0条评论

快来发表一下你的评论吧 !