WPE效应的概念 如何让减小WPE效应呢?

电子说

描述

如果模拟IC工程师你经常用.18um以上的工艺,那么你很可能从来没有关注过WPE以及LOD(Length Of Diffusion)效应。到了.18um以下的工艺,就要关注这些物理效应了,因为这些物理效应已经对电路造成了不可忽视的影响。

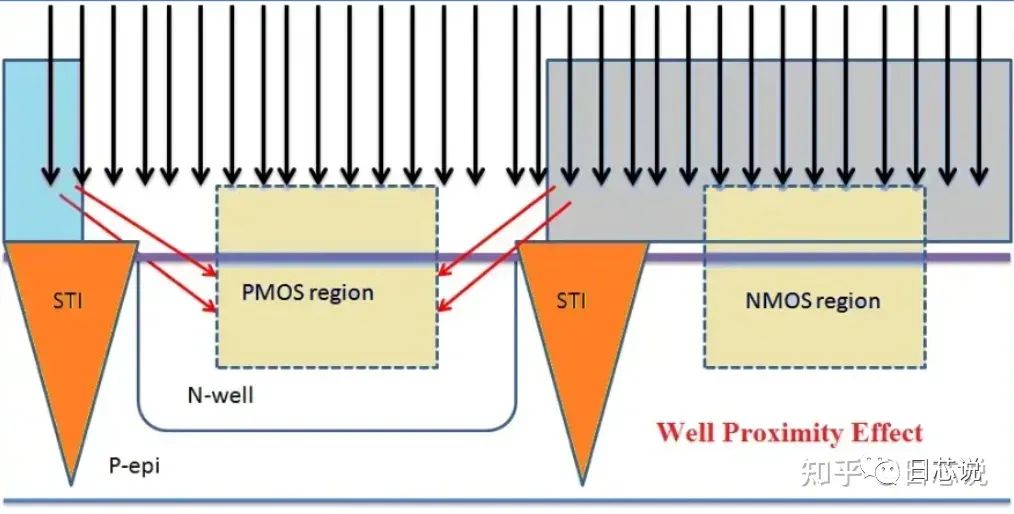

WPE(Well Proximity Effect)就是阱临近效应,是指在阱doping的过程中,阱边缘由于散射doping浓度比其他地方要高一些,这样临近阱边缘的器件特性就与远离阱边缘的器件特性不一致,主要体现在阈值电压、迁移率和体效应上。

WPE的概念就是这么简单,那么主要体现在什么参数上?

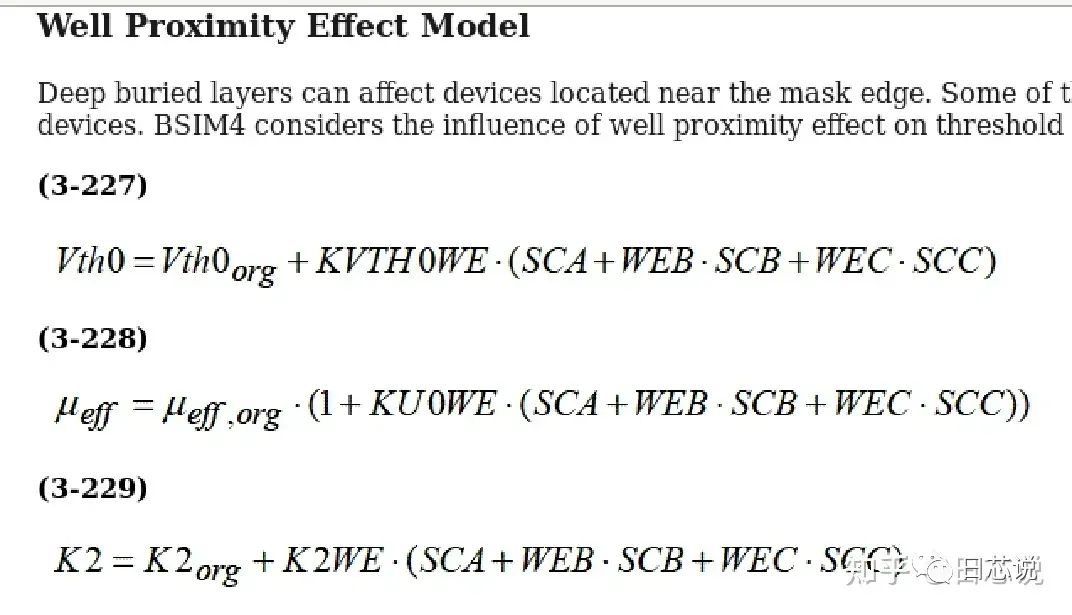

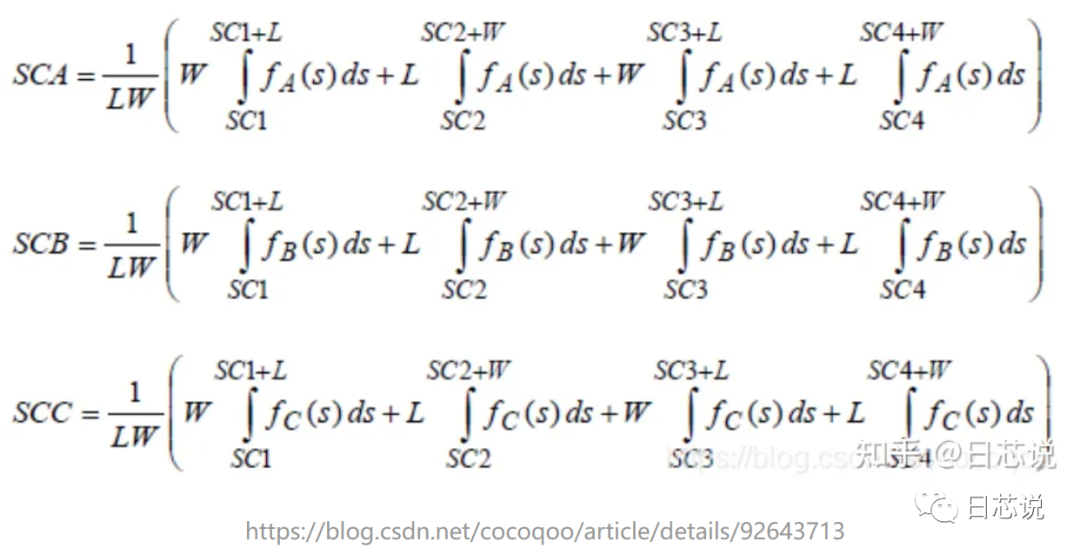

bsim模型中的介绍是以下这样的三个公式。Vth0、Ueff和K2分别是阈值电压、体效应和电迁移率影响因子,我们关注最多的就是阈值电压的影响,如果你的电路对阈值电压很敏感,那么就要特意关注一下WPE参数了。

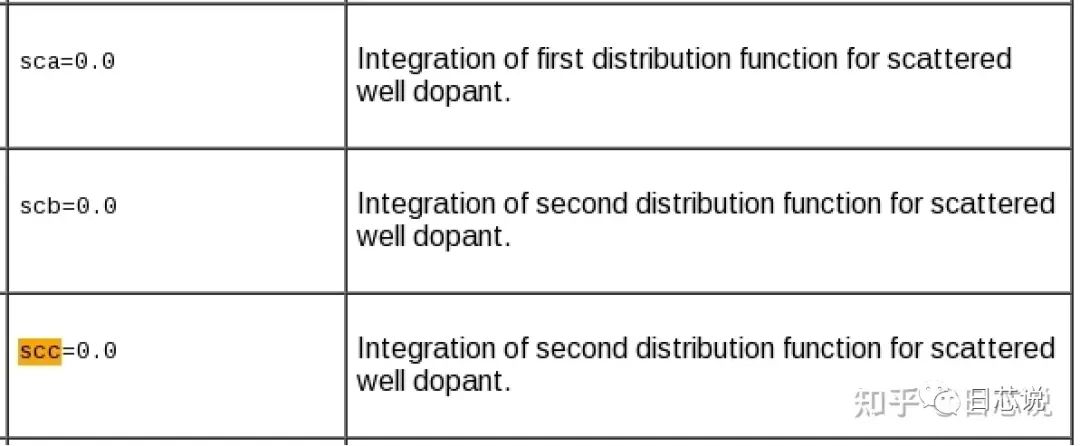

可以看出,主要是由三个参数SCA、SCB和SCC影响,在bsim模型中,这三个参数定义如下:

有人说,这个定义很晦涩,没关系,不用管,你就知道这三个参数越大,WPE效应越大,对阈值电压等的影响越大就可以了,其实SCA,SCB和SCC通俗的讲,是器件各个边缘到well距离的积分。

那么在实际cadence中,该如何考量?

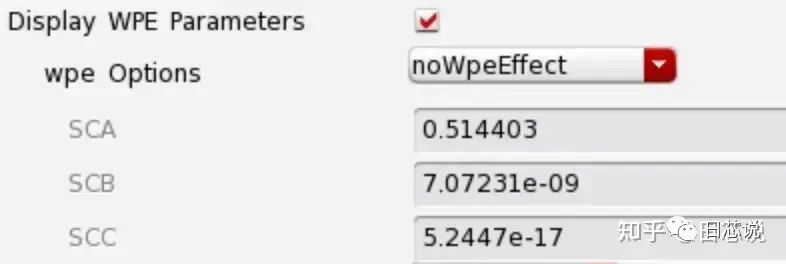

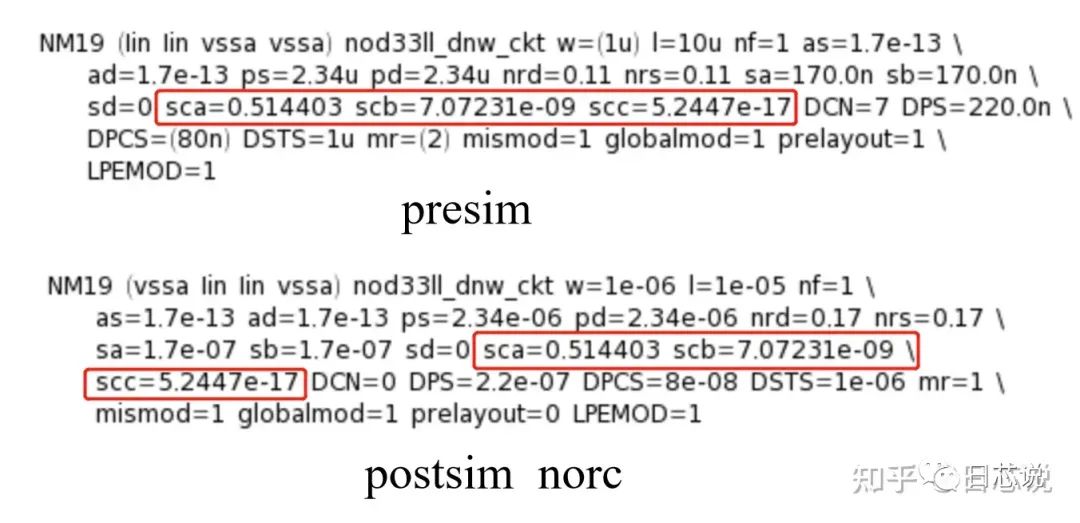

在我们做前仿真的时候,一般不会特别注意WPE效应的参数,在每个MOS的properties界面中,WPE参数是默认隐藏的,如果你点击display,它会默认选择了no wpe effect,就是在前仿真不考虑WPE效应,可以看到,SCA、SCB和SCC这个数值,在no wpe effect这个数值是很小的,几乎不会对阈值电压等参数造成影响。

那么,在画完版图进行后仿真的时候,我们知道,我们一般会先做norc的抽取,norc抽取不抽取版图中的寄生电阻和电容,但是会考虑WPE以及LOD这些物理效应。当我们norc做完得到后抽的网表后,我们第一步应该去看你的电路的dc电对不对,对于前仿真来说有没有很大偏移,关键电压或者电流节点是一定要看的,如果你做了一个基准电路,你不能只看你的基准输出电压,你内部的关键节点的电流或者电压节点都是要看一下的,因为有时候,输出是对的,但其实内部有节点是不正常的。

版图如果画的完美,那么后仿真的WPE参数和前仿真几乎是一样的,差距很小。如果画的不好,WPE参数就会变大。但实际上,版图做到完美有些难,我们就是尽量减小WPE效应。

下面是一个前后仿真的WPE参数对比,做到了前后仿真完全相等,是不是很惊讶。

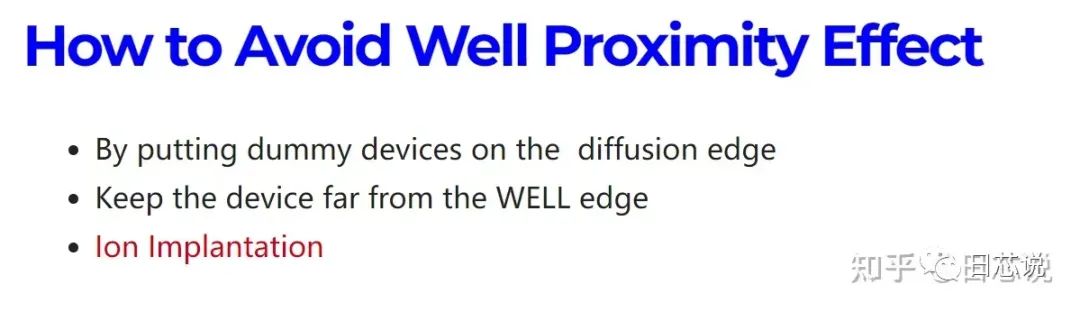

那么,如何做到以上结果呢?在siliconvlsi中给出了以下3个方法,但是实用的我只知道第二种很实用,其他两种待验证。但是第二个方法有个弊端,就是会增大版图面积,因为阱需要一个大的阱,所以如果对阈值电压、体效应等这些要求不高,可以适当增大阱的面积,不要增大的太大,在面积和精度上取个折中。

第二种方法,将器件远离阱,可以减小WPE,即将well面积画大一些,将器件的上下左右四个方向到well的距离尽量大,一般都会有一个最小距离要求,大部分是2um以上,不满足2um也不会报DRC错误,所以在DRC和LVS验证的时候是查不到WPE效应的。

如果满足了2um,一般都可以将WPE降到很小,**如果满足了2um还不能和前仿真相等,那就是你用的工艺还有一些其他的规则要求,但这时候WPE肯定是在可以接受的范围了。

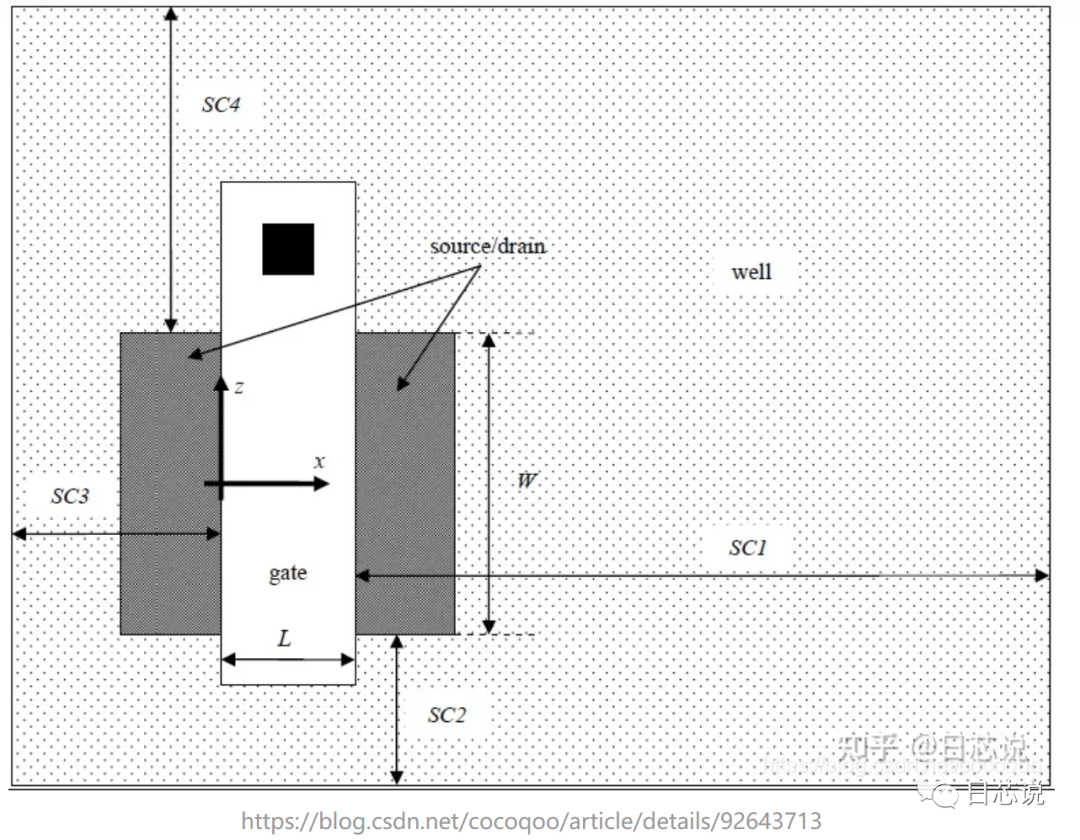

如下图,在画版图的时候,将器件4个方向到well的距离SC1~SC4都取大,这时候WPE效应就很小了。

因为WPE的三个参数SCA、SCB和SCC,都是SC1~SC4的积分,如下公式,这时候回到以上bsim模型中关于SCA、SCB和SCC的表格的定义,就很清楚了,其中fA(s)、fB(s)、fC(s)是经验常数。

-

MOS管的米勒效应:如何减小米勒平台2023-02-14 14975

-

讲一讲LOD效应2023-11-03 5942

-

场效应管的关断问题2017-12-09 21893

-

场效应管概念2019-07-29 4442

-

如何减小过孔的寄生效应带来的不利影响?2021-04-21 1834

-

怎么设置mos管的WPE Proximity Effect?2021-06-24 2554

-

如何利用霍尔效应测量磁场呢?2023-04-13 1411

-

用MOS场效应管网络减小音频振荡器的失真2009-04-08 740

-

场效应管概念:2009-11-09 1154

-

简述什么是压电效应_压电效应的发现2019-07-18 36730

-

分析一个电路因WPE效应挂掉的案例2023-02-20 10804

-

为什么说共源共栅结构会减小米勒电容效应呢?2023-09-05 3001

-

什么是凹槽效应?什么原因引起的?怎么抑制这种异常效应呢?2023-10-11 4059

-

逆压电效应的概念及其特点2024-07-26 8289

-

霍尔效应是一种磁电效应吗2024-10-15 2066

全部0条评论

快来发表一下你的评论吧 !