LVDS串并转换与并串转换设计

描述

串并转换与并串转换是高速数据流处理的重要技巧之一。其实现方法多种多样,根据数据的顺序和数量的不同要求,可以选用移位寄存器、双口RAM(Dual RAM)、SRAM、SDRAM或者FIFO 等实现。

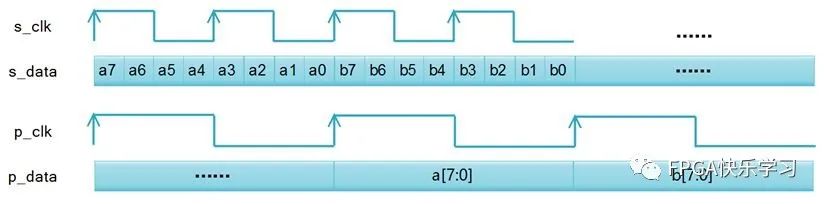

带有高速收发器或LVDS等串行收发器的应用都包含了典型的串并转换与并串转换设计。以笔者在《XilinxFPGA伴你玩转USB3.0与LVDS》一书的第8章介绍的LVDS收发实验为例。如图3.21所示,FPGA接收到LVDS串行时钟s_clk和串行数据s_data,s_data是逐位传输的,每个s_clk时钟周期传输4bit数据。每2个s_clk时钟周期共传输8bit数据,这8bit数据就是实际应用中有具体意义的有效数据。因此,串并转换后,1bit位宽的s_data在2个s_clk时钟周期中累计送入的8bit数据,最终要转换为FPGA的并行时钟p_clk所同步的8bit位宽的并行数据p_data上。

图3.21 串并转换波形

由于LVDS的传输基于FPGA的硬件物理层结构,因此FPGA开发工具上通常都有配套支持的IP核供直接配置使用,串并转换(LVDS接收)或并串转换(LVDS发送)的工作都由IP核完成了,无需设计者自己写代码实现。

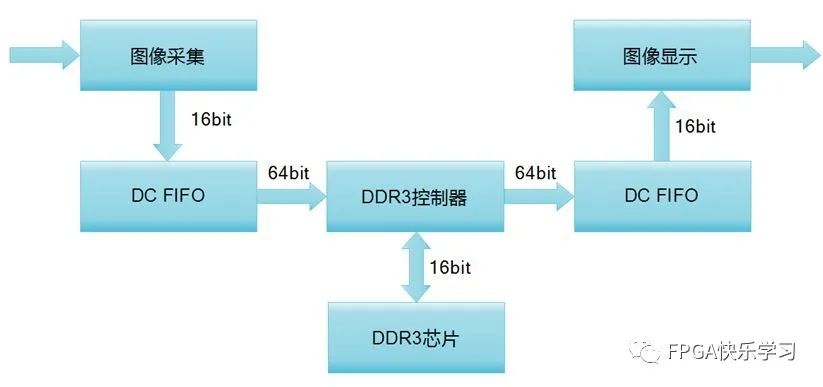

笔者在实际设计中,使用较多的是基于FIFO的串并转换或并串转换设计。如图3.22所示,左右两个FIFO,除了起到了数据缓存的作用,也起到了位宽变换,即串并转换(16bit转换为64bit)和并串转换(64bit转换为16bit)的作用。

图3.22 串并转换与并串转换应用

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何使用其gearbox功能来实现不同的比率的串并转换功能2022-08-02 4596

-

FPGA设计思想与技巧之串并转换和流水线操作2012-02-10 6892

-

串并转换74hc1642013-10-12 3026

-

求助 双工 并串转换的板子的通信问题2014-03-30 2653

-

1to8串并转换2015-03-09 3129

-

FPGA串并转换实现问题2015-07-08 5283

-

LVDS信号串并转换芯片UB92402017-03-25 5554

-

FPGA串/并转换的思想相关资料推荐2022-02-23 1104

-

串并转换VHDL代码2008-05-20 4212

-

84调制解调程序(包括串并转换,判决等等)2008-11-28 1320

-

串并转换 通过多通道串-并转换器将多个同步串行数据流转换为并2009-06-14 685

-

基于CPLD的串并转换和高速USB通信设计2011-09-27 969

-

并串转换和串并转换2016-04-27 2503

-

74ls164与单片机的串并转换(串转并\串进并出)2018-05-08 33649

-

(18)FPGA串/并转换的思想2021-12-29 536

全部0条评论

快来发表一下你的评论吧 !