芯片DFX:Coresight架构

电子说

描述

最近接触到了一些产线的Test的东西,然后发现这里面有一些DFX的相关东西。

之前在梳理整个安全领域全景图的时候,也提到了调试安全。

林林种种原因让我打算来学习一下DFX相关的内容,那自然就绕不开Coresight。

今天就一起来看看Coresight吧,最近喜欢上了画图来整理自己的思路。

缩略词

CoreSight Soc-400一个完整的调试和跟踪解决方案,包括如下组件:

• 控制和接入组件:

• DAP(Debug Access Port):用来连接外部硬件调试工具的物理接口,允许外部调试工具访问芯片上CPU、CoreSight、DDR等。

• ECT(Embedded Cross Trigger)

• 跟踪数据源:跟踪源是CoreSight中用于产生跟踪信息的组件。每个跟踪源组件都会产生一种格式的信息,最终可以组合在一起并且通过跟踪链接到输出端口。

• PTM(Program Trace Macrocell):监控处理器运行状况,将处理器执行过的指令信息进行压缩传输。

• STM(System Trace Macrocell):捕捉系统的事件信息并以获取数据跟踪形式传输到跟踪漏斗或跟踪输出组件。

• ETM(Embedded Trace Macrocell):监控处理器运行状况,将处理器执行过的指令信息进行压缩传输。跟踪指令执行、数据搬运、PE(Processing Element)事件。

• 连接:

• Synchronous 1:1 ATB bridge:

• Replicator:可以把单个输入复用到两个分支输出,可以使得CoreSight系统跟踪信息同时传输到两个或多个输出。

• Trace Funnel:把CoreSight系统中多个跟踪源产生的信息组合在一起并以单个流输出到高级跟踪总线ATB。Funnel之间可以级联,一个Funnel最多可以支持6个跟踪源信息输入。

• 跟踪输出节点:

• ETR(Embedded Trace Router):把跟踪数据存储到调试目标平台的系统内存上,存储系统内存空间是可配置的。

• ETF(Embedded Trace FIFO):主要是缓冲数据的输出,尤其当当量数据在瞬间产生式,通过ETF可以平滑数据的输出速率。缓存可以被配置为FIFO或Circular Buffer;FIFO满了之后就会反压,源头停止输出跟踪数据;Circular Buffer满了后则会覆盖。

• TPIU(Trace Port Interface Unit):把捕捉到的数据导出到外部调试适配器,如DSTREAM。

• ETB(Embedded Trace Buffer):是芯片内一块RAM,用来存储捕捉到的跟踪信息。可以通过DAP访问存储在ETB中的数据。

• TMC(Trace Memory Controller):在芯片设计时可配置,配置成ETB时跟上面介绍的ETB功能一致。还可以配置成ETR和ETF。

时间戳组件:产生CoreSight或处理器所需的时间戳。通过Narrow timestamp replicator分发到多个目的设备。路径:时间戳发生器->时间戳编码器->Narrow timestamp replicator->时间戳解码器->CPU/CTI等。

• 时间戳发生器

• 时间戳编码器

• 时间戳解码器

• AMBA AHB跟踪宏单元(HTM)

• 调试访问接口(DAP),

• 嵌入式交叉触发器(ECT),

• AMBA跟踪总线(ATB),

• 桥和复制器(replicator),

• 跟踪聚合器(funnel),

• 跟踪端口接口单元(TPIU),

• 嵌入式跟踪缓冲器(ETB),

• 测量跟踪宏单元(ITM/STM)

更详细的可以阅读【ARM:CoreSight、ETM、PTM、ITM、HTM、ETB等常用术语解析】

一、coresight

coresight是ARM公司提出的,用于对复杂的SOC,实现debug和trace的架构。该架构,包含了多个coresight组件。众多的coresight组件,构成了一个coresight系统。

我们也可以根据coresight架构,实现自己的coresight组件。

每个coresight的组件(component),都要遵循coresight架构的要求。

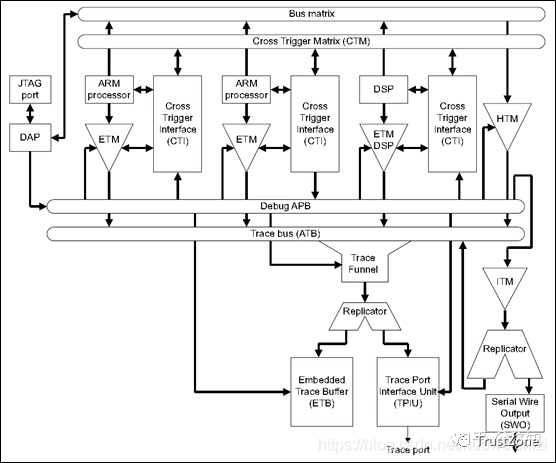

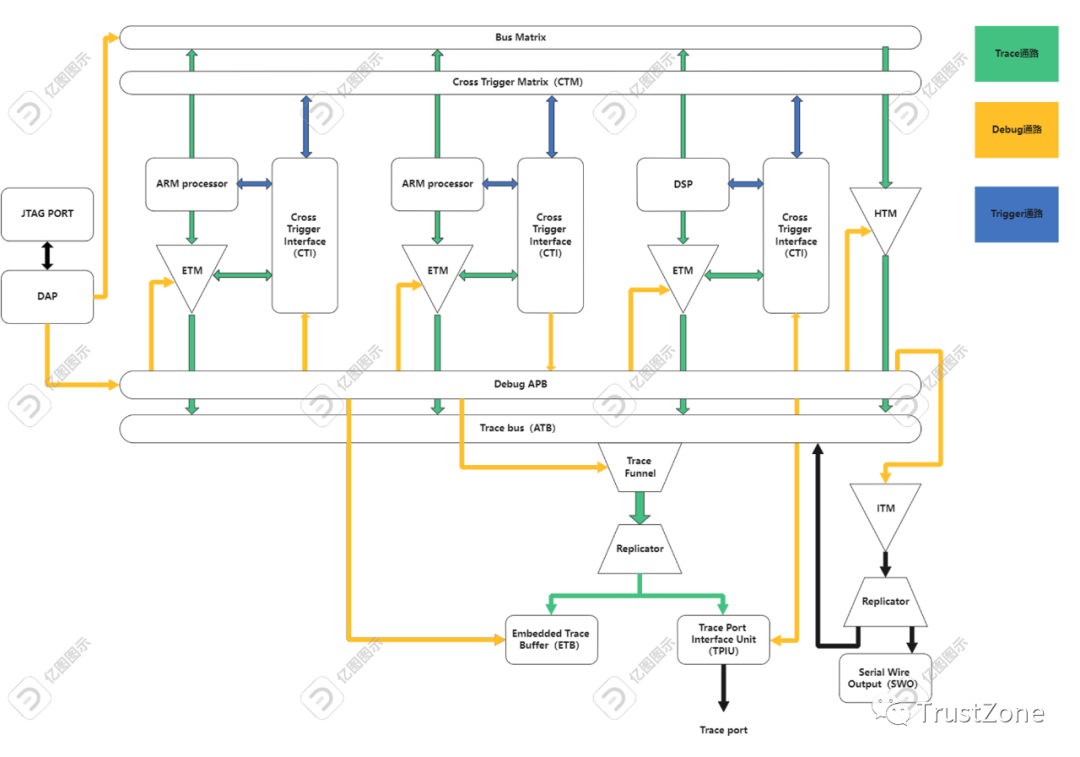

1、 典型的一个coresight的环境

以下是一个典型的coresight环境,包含了两个ARM core,一个DSP,和众多的coresight组件。

这个coresight组件,实现对core,DSP的debug和trace功能。

环境中,总共包括3个通路

• trace通路:将core和DSP内部信息输出到外部

• debug通路:对core和DSP实现debug

• trigger通路:用于core和core之间,core和DSP之间,传输trigger信号

1.1、trace通路

trace通路,实现对master组件的数据追踪功能,使用ETM来追踪。

• ETM负责追踪处理器和DSP的信息,将信息打包,通过ATB总线发送到trace bus上。

• trace bus上有trace funnel,funnel接收多个ATB总线数据,然后合并成一个ATB总线数据,发送给replicator。

• replicator接收到ATB数据,根据配置,将ATB数据发送给ETB和TPIU。

1.2、debug的通路

debug通路,用于外部的debugger,对ARM core和DSP进行调试功能。

上图中,只考虑了JTAG的port。其实还有SW的port。

DAP接收外部端口的JTAG数据,然后转化成对DAP内部的AP的访问,然后AP再转化为memory-mapped的总线访问,去访问soc内部的资源。

上图中,DAP输出两个memory-mapped总线,

• 一个是debug apb总线,连接到debug APB互联上,用于访问debug组件的寄存器,

• 一个是system bus,连接到bus matrix,用于访问soc的内部的资源。

debug APB互联,连接了有CTI,ETM,HTM,ITM,ETB,TPIU等coresight组件,因此外部的debugger可以通过JTAG port,对这些coresight组件进行访问。

bus matrix一般是连接soc的一些外设,如memory,串口等,因此外部的debugger可以通过JTAG port对这些外设设备进行访问。

1.3、trigger通路

trigger通路,用于给指定的组件发送trigger信号,或者接收指定的组件的trigger信号。

这个功能由CTI和CTM来实现。

CoreSight交叉触发接口(CTI)是一种硬件设备,它将被称为触发器的单个输入和输出硬件信号带到设备和从设备输出,并通过交叉触发矩阵(CTM)将它们通过编号信道互连到其他设备,以便在设备之间传播事件。

每个core和DSP都有一个CTI组件相连,CTI可以给处理器(DSP)发送trigger信号,也可以接收处理器(DSP)的trigger信号。

所有的CTI和CTM相连,因此可以实现多个CTI之间的trigger信号的相互发送与接收。

2、coresight组件的种类

2.1、control component

trigger的coresight组件

• ECT(embedded cross trigger)

• CTI(cross trigger interface):接收和发送trigger信号

• CTM(cross trigger matrix):CTI之间的trigger信号传递

2.2、trace sources

trace的coresight组件:

• ETM(embedded trace macrocells):追踪指定设备(处理器,DSP)的trace信息,每个设备(处理器,DSP)均有自己的ETM。

• AMBA trace macrocells:追踪AMBA总线的trace信息。

• PTM(program flow trace macrocells):

• STM(system trace macrocells):追踪总线互联上的trace信息

2.3、trace links

trace信息传递过程中所需要的中间coresight组件:

• trace funnel : 将接收的多个ATB总线数据合并成一个ATB总线数据

• replicator: 将一个ATB总线数据,分发成多个ATB总线数据发送

• ATB bridge: ATB 桥,用于两个不同的ATB域之间数据传输

2.4、trace sinks

最终接收trace信息的coresight组件

• TPIU(trace port interface units):将ATB数据通过trace port发送给外界

• ETB(embedded trace buffers):存储ATB数据的buffer

• TMC(trace memory controller):

每个trace sink可以有一个trace formatter。

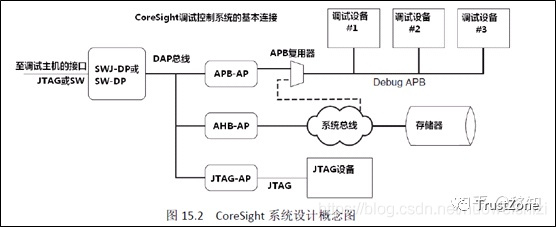

2.5、debug access port

DAP不属于coresight的组件,但是我们会通过DAP来对coresight的组件进行访问。DAP包括以下:

• APB access port(APB-AP)

• AHB access port(AHB-AP)

• AXI access port(AXI-AP)

• JTAG access port(JTAG-AP)

• serial wire JTAG debug port(SWJ-DP)

• JTAG debug port(JTAG-DP)

• ROM table

DAP主要是由DP和AP组件。DP负责接收外部的JTAG或SW数据,然后转化为对AP的访问,而对AP的访问,是可以发起memory-mapped的访问。因此就可以对内部的资源进行访问。

如上图:DAP包括了三个AP

• APB-AP:对挂接到debug APB总线上的内部调试设备的访问

• AHB-AP:对挂载在AHB系统总线上的设备的访问

• JTAG-AP:对JTAG设备的访问。这个是兼容以前较早的ARM处理器,如ARM9。这些较早的处理器内部是用JTAG来调试的。但是现在的ARM处理器,已经不用这种方式,统一用memory-mapped方式进行调试。

目前的ARM soc中,一般至少会包括一个DAP。而一个DAP可以包括1-256个AP(access port),AP受DP的控制。

只有对AP的访问,才可以转化成memory-mapped总线,对soc的内部资源进行访问。

memory-mapped bus通常指的是将设备的寄存器映射到内存地址空间中,使得CPU可以通过读取和写入这些内存地址来访问和操作这些设备。这种方式使得CPU可以像访问内存一样访问这些设备,简化了设备的访问和控制方式。

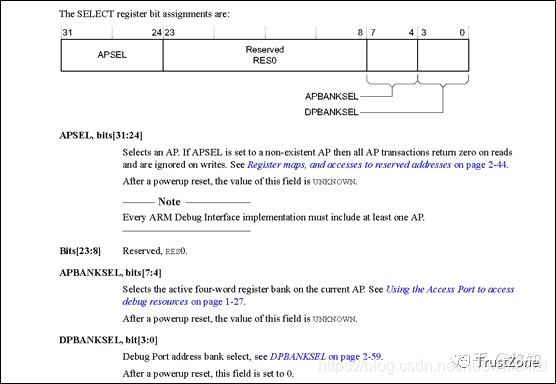

DP中有一个SELECT寄存器,该寄存器用来选择,DP对AP的访问,是针对于哪一个AP进行访问。

DAP中,是可以有多个AP的,而每次,只能对一个AP进行访问。因为需要对AP进行编号,编号的值就在APSEL位域中。因为这个位域有8位,因此DAP中可以最多有256个AP。

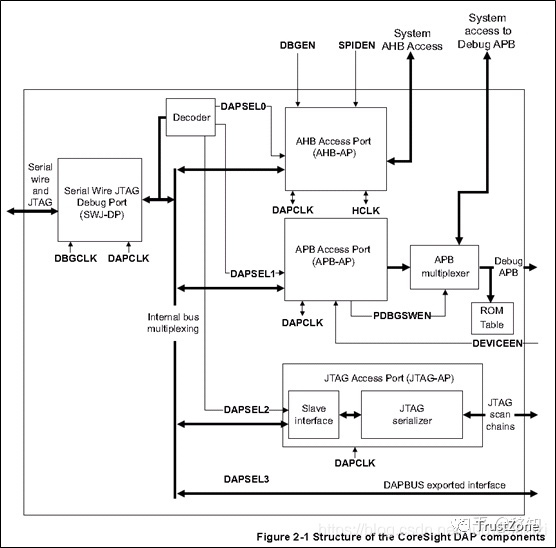

DAP的内部结构如下图:

包括了一个DP,和3个AP,依次是AHB-AP,APB-AP,JTAG-AP。

DP通过JTAG或者SW管脚,连接外部的debugger,和外部debugger进行通信。

DP接收到外部debugger发送的JTAG或SW数据,转化为对内部AP的访问。经过decoder模块,判断是对哪一个AP进行访问,然后将访问信息发送给对应的AP。

AP接收到DP的访问后,转化为对应的总线访问,去访问内部资源。

然后将访问的信息,才回送给DP,DP再通过JTAG或SW,将访问信息返回给外部的debugger。

以上就是本文全部内容,希望看完能对coresight有一个宏观了解。

文章来源:TrustZone

审核编辑:汤梓红

-

采用UltraScale/UltraScale+芯片的DFX设计注意事项2024-01-18 2181

-

DFX可制造性设计与组装技术2023-12-11 1737

-

芯片DFX:Coresight的寄存器一览2023-11-02 2574

-

来讲讲与工具密切配合的CoreSight2023-10-30 3663

-

什么是DFX技术?DFX设计一定要执行设计规则检查吗?2023-09-21 10271

-

Arm CoreSight ETM-M33技术参考手册2023-08-17 653

-

ACPI for CoreSight™性能监控单元架构1.0平台设计文档2023-08-11 681

-

CoreSight性能监控单元架构2023-08-09 722

-

2021华为开发者大会亮点 HarmonyOS架构演进与关键技术-HarmonyOS对DFX能力的要求是什么2021-10-23 3297

-

简述DFX理念与产品研发(一)2021-09-28 4317

-

CoreSight是什么?其功能有哪些?2021-07-16 1172

-

PCB板DFX工艺性要求2016-07-26 1528

-

ARM调试CoreSight、ETM、PTM、ITM、HTM、ETB等常用术语解析2014-10-13 4486

全部0条评论

快来发表一下你的评论吧 !