RF-ADC后台校准原理及收敛时间测量

描述

各位亲爱的老铁们,转眼间,2023年就只剩最后的一个季度了,相信各位在座的时间管理大师已经在“决战四季度,大干一百天”的觉悟中疯狂输出。今天超强冷空气杀过来,各位已经能感受到什么是真正的寒冬将至。虽然工作时间紧迫,但是学习依然不能落下,今天主要给大家介绍一下RF-ADC后台校准原理及收敛时间测量,内容实属硬核,大家需要慢慢品。

知识背景介绍

对于高速数字信号应用来说,实现更高采样率的高精度ADC 的行之有效的方法是采用多通道时间交织(Time-Interleaved)结构,即使用M 片ADC芯片通过并行交替采样方式来实现更高的采样率。系统采样率相对于单片ADC 提升了M 倍。

由于信号延迟以及制造工艺等原因,各通道间总存在一些非理想因素如偏置失配、增益失配以及时序失配等,这些失配导致ADC 系统性能下降,因此需要采取校正措施抑制或者消除这类失配。

本文首先介绍TI-ADC的原理及通道间各类失配对ADC性能的影响;然后测试并分析RF-VU3P中后台校正大致完成时间,为后续快速校准的工作提供理论基础。

知识点1:TI-ADC基本原理及误差分析

本节首先介绍TI-ADC的工作原理,建立了包含各类通道间失配的失配模型,在此基础上分析不同失配对TI-ADC性能影响,为后续测试提供理论依据。

1.1TI-ADC工作原理

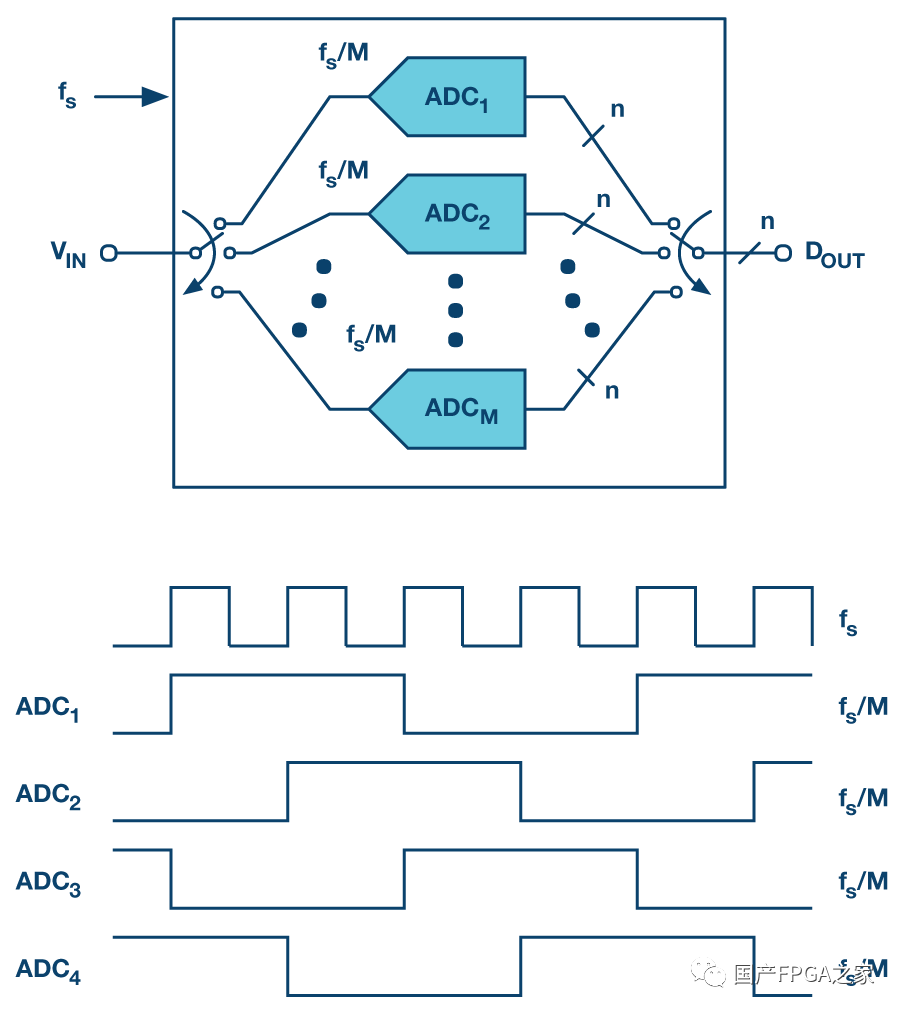

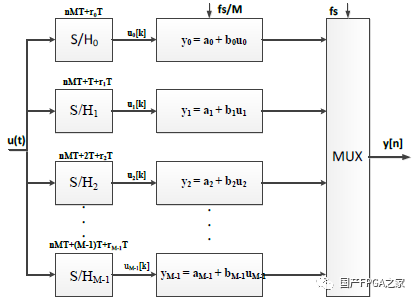

时间交织ADC 的系统结构如图1所示:

图1 M次时间交织ADC阵列及时钟方案

系统包含了M 个并行相同的子ADC(sub-ADC)。每个sub-ADC都有独立的采样保持器(Sample and Hold),分别对同一个模拟输入信号x(t)进行采样,相邻两个sub-ADC相位差为2π/M。从整个时间交织系统看,输入信号x(t)被以 fs=M*fsub 的频率采样,系统采样率提高了M 倍。理想情况下,每个sub-ADC 的性能完全相同,采样间隔均匀,整个ADC系统的转换速率相对于sub-ADC 提升M 倍。

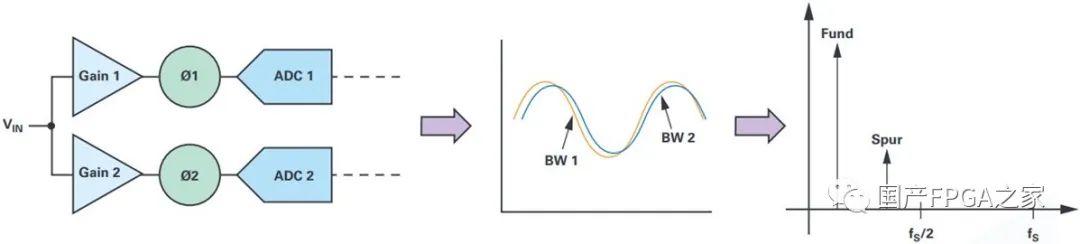

现在对信号x(t)以系统频率为fs采样。理想情况下,相邻子通道的采样间隔为MTs,相邻两个子通道ADC 之间采样的相位差为2π/M,以间隔为MTs的冲激串Pm(t)采样得到的采样序列为:

1.2时间交织ADC失配建模

时间交织技术优势是增加了带宽,使得频率规划更为轻松,并且可以降低在ADC输入端使用抗混叠滤波器带来的复杂性以及成本。理想情况下,TI-ADC各通道等时间间隔地采样数据,然而受限于工艺制造技术等现实问题,导致各sub-ADC参考电压不一致,引入偏置误差;sub-ADC间运放的放大倍数不一致,引入增益误差;采样时钟的相位间隔不同,引入了时序失配。

这些失配在输出频谱上表现为周期性杂散,降低TI-ADC的SNR及SFDR等动态性能。随交织通道数目的增加,通道间失配对TI-ADC的性能影响越严重。因此需要对TI-ADC失配误差进行建模,量化各类失配误差对TI-ADC的影响。

1.2.1偏置失配

图2以2路交织采样为例,展示sub-ADC参考电压不一致造成的杂散:

图2 偏置失配

TI-ADC输出以 fs/M 在M路sub-adc中切换,且由于偏置失调为直流分量,因此固定在输出频谱 ±k*fs/M 处产生杂散,杂散幅度取决于偏置失调幅度。

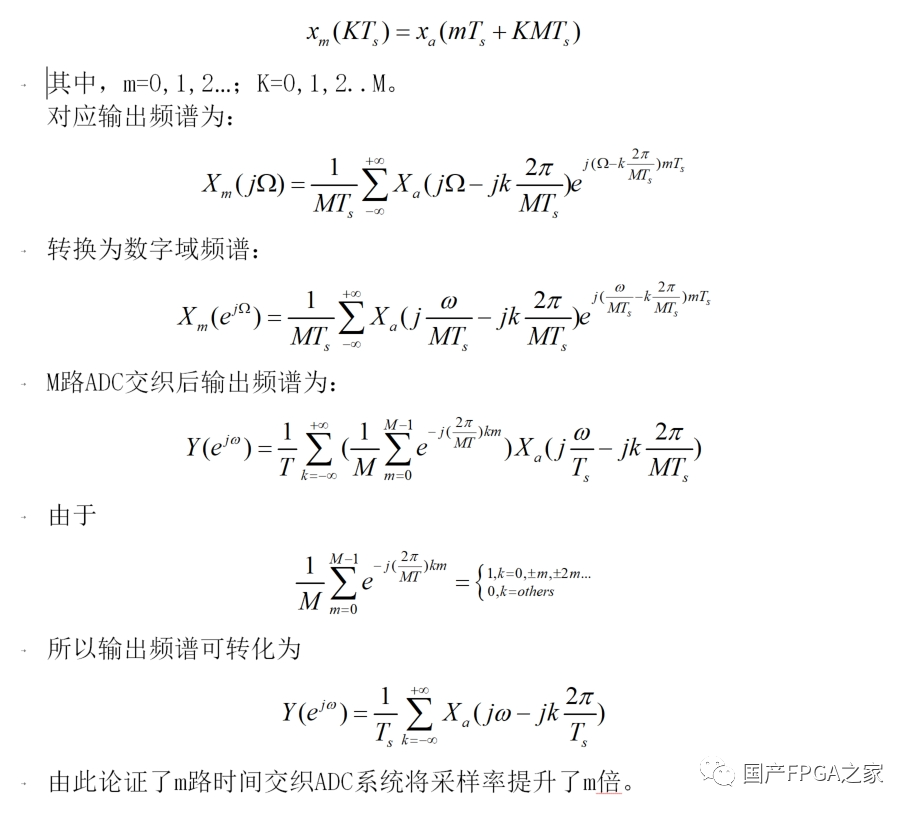

1.2.2增益失配

图3以2路交织采样为例,展示sub-ADC增益失配造成杂散:

图3 增益失配

增益失配将会产生位于 ±(k*fs/M±fin) 处的杂散。校准过程中为了降低增益失配引入的杂散,将其中一个sub-ADC作为基准,调整其他sub-ADC的增益为与基准尽可能接近的值。各sub-ADC的增益匹配度越高,该杂散越小。

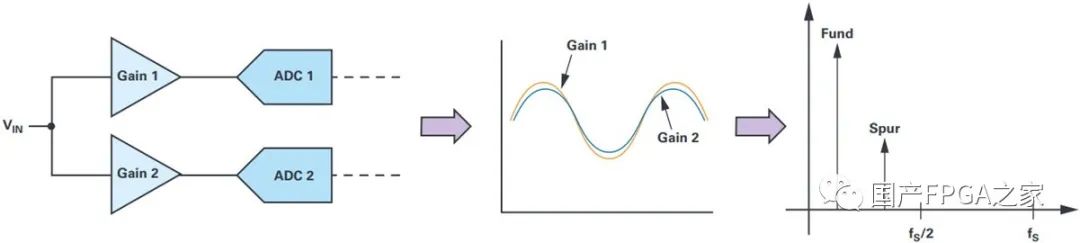

1.2.3时序失配

图4以2路交织采样为例,展示sub-ADC时序失配造成杂散。与增益失配类似,时序失配产生的杂散位于±(k*fs/M±fin) 处。

图4 时序失配

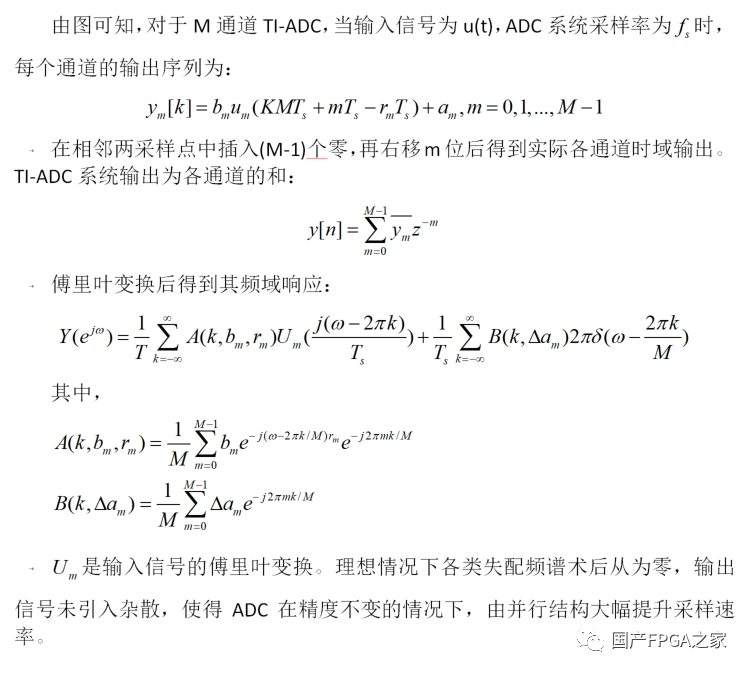

1.2.4TI-ADC失配模型

图5为M通道TI-ADC包含偏置失配、增益失配和时序失配的失配模型。其中,a0,a1,...,am为各sub-ADC通道的偏置;b0,b1,...,bm 为各通道的增益;r0T,r1T,...rmT为各通道采样时钟偏差,|rm|<1,m=0,1,2,...,M-1。

图5 M通道TI-ADC失配误差模型

知识点2:TI-ADC后台校准时间测量

本节定量分析三类通道间失配对TI-ADC性能的影响。输入信号采用正弦信号;分析某类误差时,将其他两类失配置零。由上节失配模型可知,仅存在偏置失配时,杂散位置位于:±kfs/M ;其他两类杂散位置位于:±(kfs/M±fin) 。

RF-VU3P中使用校正技术来降低各类失配带来的影响,从而实现高精度高采样率的TI-ADC。通道间校正分为前台校正和后台校正两阶段。前台校正在RF-ADDA硬核上电过程中ip控制下自动完成,本文不做研究;后台校正用于校正由温度等环境影响引入的通道间失配,共有三种校正算法:偏置校准(ocb)、增益校准(gcb)和时序校准(tscb)。

RF-VU3P中ocb校准参数寄存器不可见。通过抓取后台校准过程中,gcb和tscb系数的变化曲线,使用失配模型分析后台校准系数收敛时间。

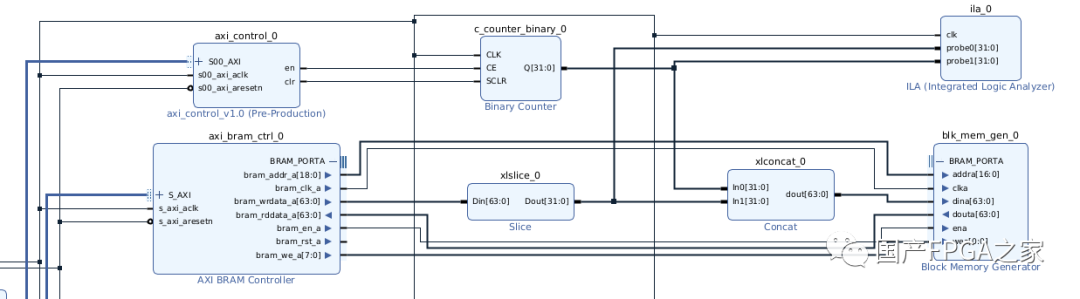

2.1RF-VU3P后台校准系数捕获

后台校准系数捕获及收敛时间计算过程:

冻结校准;

DAC发送正弦波;

校准解冻[start time];

启用计时器 && 捕获系数;

计算系数收敛时间。

图6 系数捕获模块

RF-VU3P工程基于RFDC example design制作,添加了图6所示结构捕获后台校准寄存器系数。制作了Vitis工程来编写microblaze的驱动文件,用于和下位机进行命令收发和数据传递。

2.2后台校准系数收敛时间量化

测试条件如下:

ADDA采样率:3932.16MHz;

AXI_Lite时钟:57.5MHz;

系数分辨率:1ms;

输入信号:200MHz单音信号。

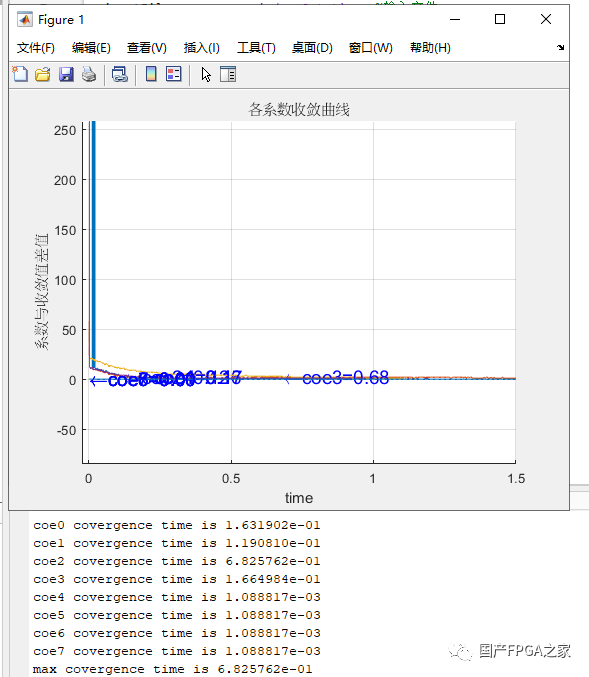

2.2.1收敛时间粗量化

图7为gcb寄存器系数随时间变化曲线。每个Tile的ADC共有4个gcb参数寄存器,每个寄存器为32bit。gcb_regN[27:16]为校准code,gcb_regN[15:0]仅参与系数收敛计算,gcb_regN[31:28]恒为0。

图7 gcb各系数寄存器系数随时间变化曲线

此处系数收敛判断条件是,系数中的校准code与最终收敛的校准code差值小于等于1个lsb,且持续时间大于5个捕获周期。此方法评估gcb系数收敛时间为0.68s。

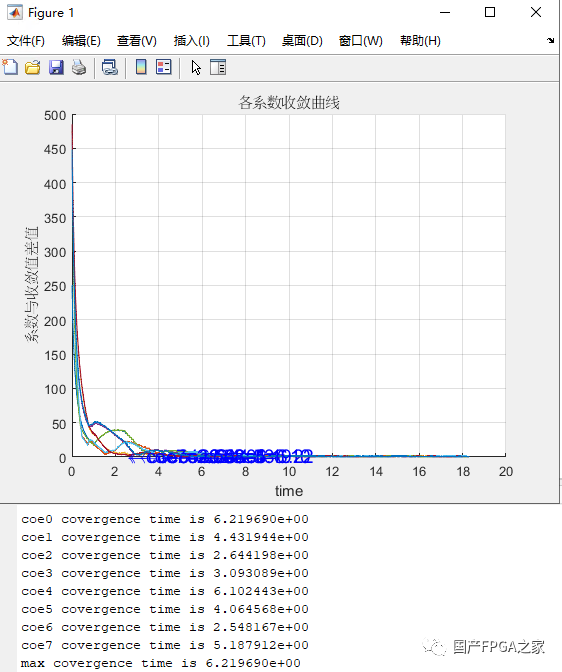

图8为tscb寄存器系数随时间变化曲线。每个Tile的ADC共有8个tscb参数寄存器,每个寄存器为32bit。tscb_regN[23:16]和tscb_regN[7:0]为sub-ADC N的校准code,其余位为0。

图8 tscb各系数寄存器系数随时间变化曲线

此处系数收敛判断条件是,系数中的校准code与最终收敛的校准code差值小于等于1个lsb,且持续时间大于5个捕获周期。此方法评估tscb系数收敛时间为6.22s。

2.2.2收敛时间模型量化

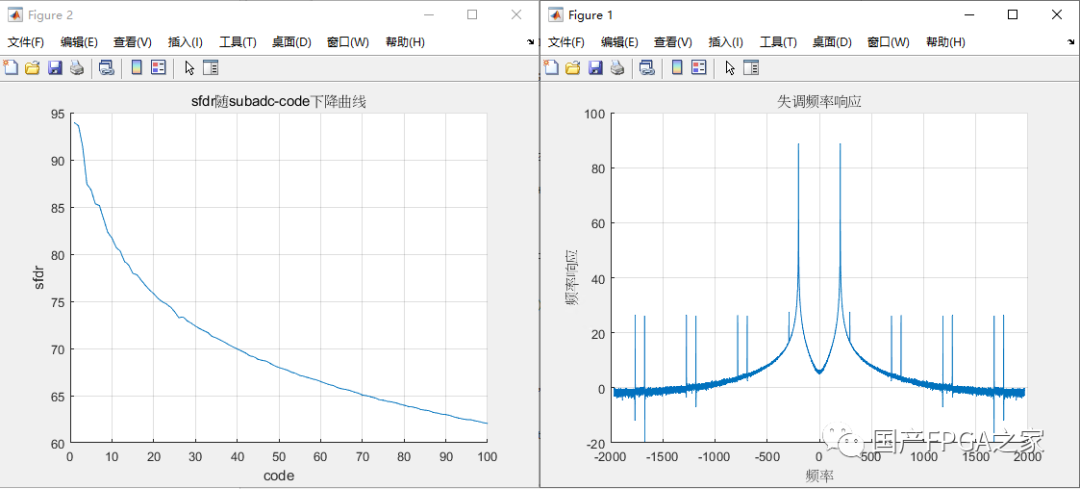

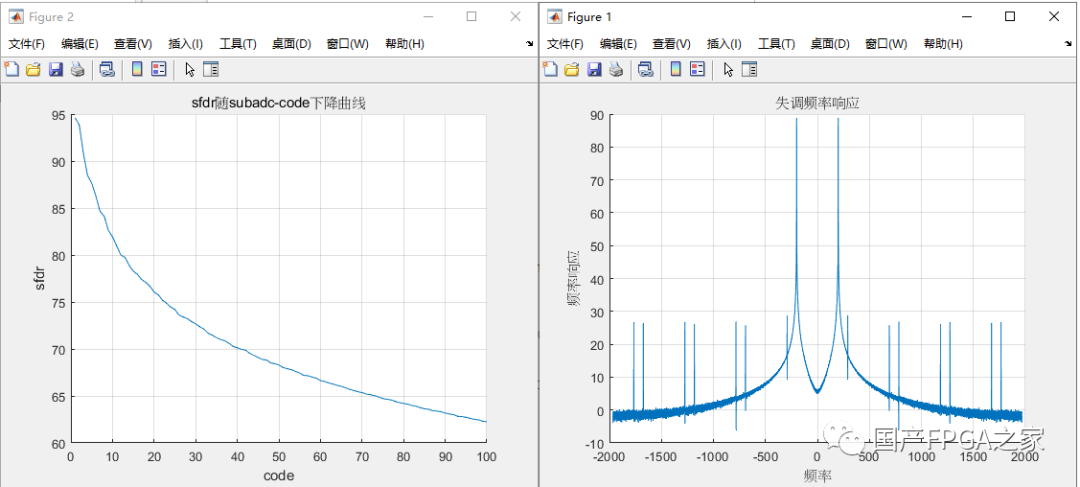

图9左图为基于失配模型计算得到的SFDR随单通道tscb校准code误差变化曲线,右图为误差code=100时频率响应。

图9 sfdr随tscb校准code变化曲线

图10左图为基于失配模型计算得到的SFDR随单通道gcb校准code误差变化曲线,右图为误差code=100时频率响应。

图10 sfdr随gcb校准code变化曲线

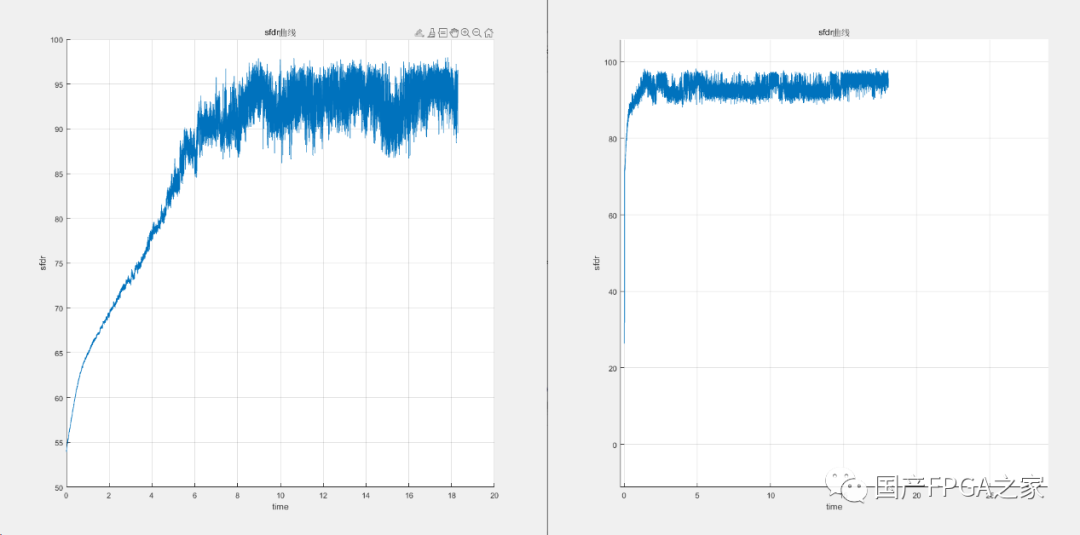

图11为基于失配模型计算得到的SFDR随时间变化曲线,左侧为tscb,右侧为gcb。由图可得tscb、gcb收敛时间和粗量化时间大致相同。

图11 基于失配模型得到SFDR随时间变化

战术总结

今天主要给各位介绍了RF-ADC后台校准原理及收敛时间测量,由于内容太硬了,为了方便大家硬饭软吃,欢迎大家在评论区交流讨论,一起学习进步。

审核编辑:汤梓红

-

精密ADC中的系统校准和背景校准2022-12-05 4859

-

RF校准的作用是什么,是校准RF频率吗?2024-06-07 698

-

使用ADC12D1800RF校准功能时,在校准过程中会不会对ADC12D1800RF寄存器的值进行修改?2025-01-16 318

-

请问使用ADC12D1800RF校准功能时,在校准过程中会对ADC12D1800RF寄存器的值进行修改吗?2019-05-17 1522

-

RF功率校准是怎么提高无线发射机性能的2019-06-25 2184

-

请问如何收敛高速ADC时序?2021-04-14 1469

-

ADC电流检测未校准导致测量值异常如何解决2021-10-13 2365

-

时间交织ADC时间失配后台数字校准算法_邓红辉2017-01-08 829

-

RF检波器揭秘2018-06-04 6647

-

RF检波器的类型及应用范围2019-07-10 6466

-

独立器件的自动校准和测试测量2020-07-29 5715

-

CN0150 利用对数检波器AD8318构建软件校准的1 MHz至8 GHz、70 dB RF功率测量系统2021-06-03 1095

-

CN0178 通过软件校准的50 MHz至9 GHz RF功率测量系统2021-06-04 1289

-

如何实现Kinetis ADC自校准2021-09-18 818

-

如何校准adc以提高精度2024-10-31 5832

全部0条评论

快来发表一下你的评论吧 !