用于半导体封装工艺中的芯片键合解析

电子说

描述

芯片键合,作为切割工艺的后道工序,是将芯片固定到基板(substrate)上的一道工艺。引线键合(wire bonding)则作为芯片键合的下道工序,是确保电信号传输的一个过程。wire bonding是最常见一种键合方式。

Gold Bonding Wire: 半导体键合金线/金丝

用于半导体封装工艺中的芯片键合。

Wire Bond/金线键合: 指在对芯片和基板间的胶粘剂处理以使其有更好的粘结性能后,用高纯金线把芯片的接口和基板的接口键合。

成分为金(纯度为99.999%),掺杂银、钯、镁、铁、铜、硅等元素。

掺杂不同的元素可以改变金线的硬度、刚性、延展度、电导率等参数。

一、 目的:建立基本的 wire bonding 标准,制定生产过程中产品合格/不合格的判断标准。

二、 范围:本标准只适用于金线球焊工艺。

三、 基本焊接条件:热压超声波焊接用于金线键合,所需的温度、压力、超声波功率及时间视不同机型、不同材料有很大不同,具体根据机型、材料特性科学设定。

四、 品质判断标准:

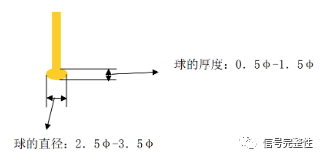

1) 球形标准,如下图所示:

① 球的直径:以2.5φ-3.5φ为标准 ,低于2.5φ为球小,大于3.5φ为球大。

② 球的厚度:以0.5φ-1.5φ为标准,低于0.5φ为球扁,大于1.5φ为球厚。

③ 球畸形:焊线偏离焊球中心超过1/2φ为球畸形。

注:以上φ为金线直径,以下类同。

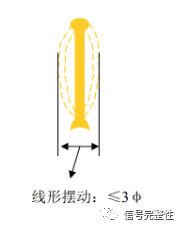

线形标准:

① 线形不良:线摆动以≤3φ、S 形≤2φ为标准,超过此标准为线形不良。线形摆动如下图所示

② 线受损:以≤1/4φ为标准,超过1/4φ为线受损不可接受。

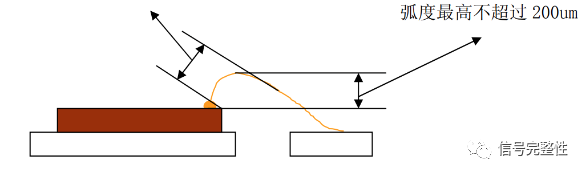

③ 弧形标准:晶粒边距金线垂直距离至少1.5φ,少于1.5φ为线低;晶粒面距线形最高不超过 200um,如下图所示。

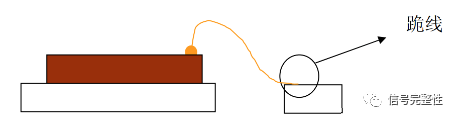

④ 跪线:如下图所示,圆圈处所指的金线贴在焊接表面上为跪线,不可接受。标准线形为圆圈处所指的金线与焊接表面应有一定角度。

3) 焊口标准:

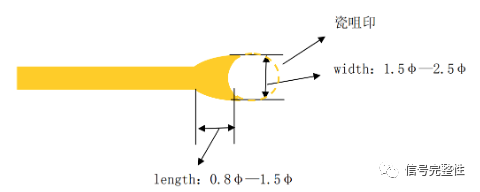

① 焊口:长为0.8φ—1.5φ,宽为1.5φ—2.5φ,且瓷咀印必须完整,超出此规格范围为不可接受,如下图所示:

② 线尾:线尾长度必须≤1φ,大于1φ时为线尾长,不可接受。跪线 length:0.8φ—1.5φ width:1.5φ—2.5φ 瓷咀印

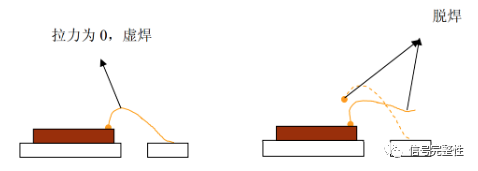

③ 虚焊、脱焊:焊球与Die面接触,焊口与Frame 表面接触,拉力测试为0时为虚焊;焊球或焊口中有一个不与焊接表面接触时为脱焊。如下图所示

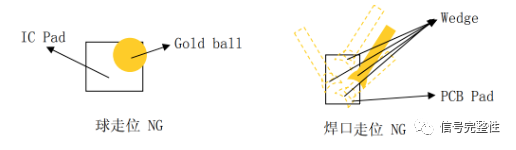

4) 位置标准:

① 走位:球走位:焊球须在IC pad位置内或恰好压在 Pad 边上,超出pad位置为球走位。焊口走位:焊点须在PCB金手指内,焊口离金手指边至少 1φ。超出金手指 为焊口走位。

② 漏线:应焊线的位置没有焊线。

③ 焊错位:金线没有焊在指定 Pad 上而是焊在别的 Pad 上。

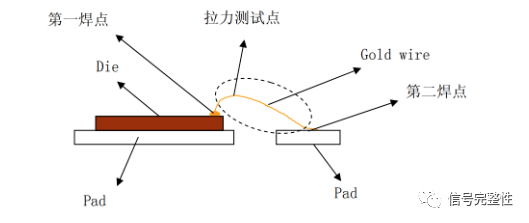

5) 拉力及推球标准:

① 拉力测试方法:拉力测试时以靠近焊球金线弧形最高处为基准,如下图所示:

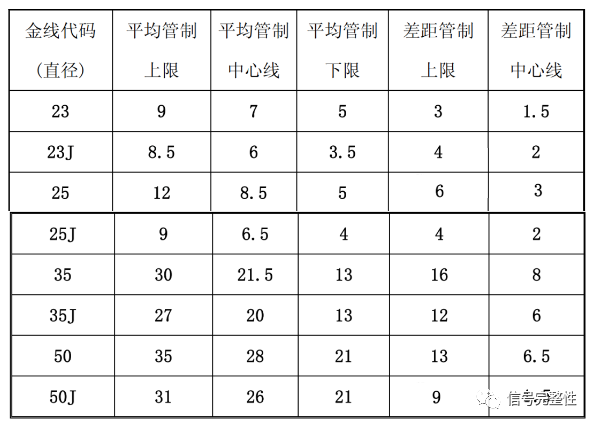

金线拉力管制,如下表:

备注:23、23J 为同一直径的金线,对 SOT-54、SOT-23 产品 Wire bonding 时有两个引线方向,方向不同金线的管制拉力不同,用J来区分,其余类同。

③ 推球不良:推球时使用推球机做推力实验,推球力至少16g以上,金线在pad上残留量≥60%,不满足此规格为推球不良。

审核编辑:汤梓红

-

介绍芯片键合(die bonding)工艺2023-03-27 16948

-

什么是倒装芯片 倒装芯片技术的优点 倒装芯片封装工艺流程2023-07-21 8276

-

半导体引线键合清洗工艺方案2010-04-22 17884

-

招聘半导体封装工程师2015-02-10 3719

-

《炬丰科技-半导体工艺》用于半导体封装基板的化学镀 Ni-P/Pd/Au2021-07-09 3935

-

半导体生产封装工艺简介2020-03-27 9602

-

半导体封装:键合铜丝的性能优势与主要应用问题2022-12-15 4413

-

半导体后封装工艺及设备2023-07-13 1212

-

半导体封装技术简介 什么是倒装芯片技术?2023-08-21 2100

-

半导体封装工艺的研究分析2024-02-25 1880

-

闲谈半导体封装工艺工程师2024-05-25 3811

-

半导体芯片键合装备综述2024-06-27 3102

-

电子封装 | Die Bonding 芯片键合的主要方法和工艺2024-09-20 2685

-

铝带键合点根部损伤研究:提升半导体封装质量2024-10-16 2111

-

芯片键合工艺技术介绍2025-10-21 1985

全部0条评论

快来发表一下你的评论吧 !