运放稳定性,你真的懂了吗?

电子说

描述

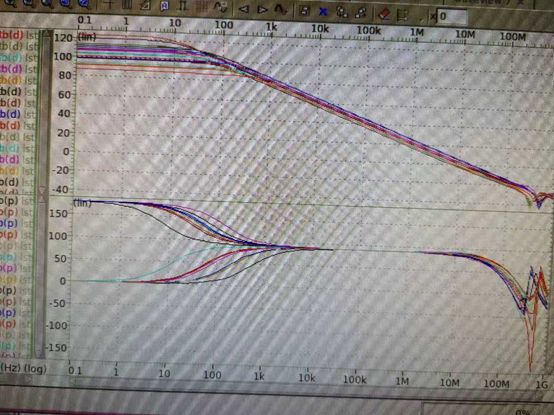

一个运放,使用电阻接成负反馈的形式,闭环放大倍数为-1。进行环路stb仿真,有些corner下相位曲线从0开始,但其他corner正常。这种是什么原因?该怎么解决?

注0:本文来源于某天微信群的讨论。感谢提问者和解答****的大神们。

注1:本文涉及到的运放经确认是一个折叠式输入,class AB输出,使用电阻配置为闭环增益负一的运放。

注2:stb仿真指的是stability,主要仿的是电路的环路稳定性。

注3:由于某些“你懂的”原因,图片只能拍照,无法截取高清图。特补上另一个图片,这个图片来自于文末Designer guide网站。

电路上来说,确实是负反馈。如果相位从零开始,那么低频时,岂不是正反馈?对于仿真器,如何计算的,大家是怎么理解的呢?

大神1给出了一个解答,原文如下:

这个问题来源应该是内部补偿的minor loop还在导致的,如果没有minor loop,stb仿真就不会出现这种问题。。。。stb用的Middlebrook那个double injection方法会常常出现这个问题,大家好像都忽略这个问题,没看见谁去深究过这个主要是Middlebrrok的文章太难懂了...

这时,大神2补充道:

第一,spectre的STB仿真时基于“Middlebrook方法”,仿真时将输入与输出断开,引入交流源,得到Tv=Vy/Vx 。第二,在反馈环路引入电流源ix、iy,Ti=iy/ix

仿真时假定Tv=T=LG。对于CMOS工艺,低频gate阻抗无穷大,ix≈0,Ti∞,所以T≈Tv。高频时,由于有漏电流,Ti不断减小,T≠Tv。所以在低频是得到的LG是一致的,高频时会有一定区别在Ti大、Tv比较小情况下,由于spice是单独计算Ti和Tv。若Tv非常小,spice计算出来的TV与实际值会有δTv的差值,经过很大的Ti放大后,最终得到的环路增益会有很大的误差值。

大神1此时又做了更为详尽的补充:

反正我估计这篇论文,包括我在内的大多数人看了也只能是知其然,但不知道其所以然。还是解释不了为何某些corner会从0度开始,反正从我直觉上猜测是因为里面还有个小环路导致的。。。对于multi-loop的loop gain我也一直有些confuse,因为很明显stb在不同地方加probe仿出来的phase margin是不一样的,因为断的位置不一样确实也是不同的loop,如果按照middlebrook这个理论怎么更好的去解释呢?

所有3-stage及以上的opamp论文都不看loop gain,稳定性就只看close-loop gain的极点是不是在左半平面,可以判断是否稳定,但是close-loop gain是告诉不了你margin还有多少的,因此文章通常都是看阶跃响应的ripple来估算。从mason定理来讲,不管你in/out是哪个点,close-loop gain的分母永远是一样的,也就是说闭环极点是唯一的,所以稳定性也是确定的。所以感觉上stb仿真不管在哪里加probe,即使仿出来的phase margin有的大有的小也没关系,反正都会是稳定的。随便举个例子,可能在某个地方断环稳定性的PM随pvt corner变化5070度之间,在另一个地方断环PM在3540度之间,其实都是正确的,不要因为phasemargin不够大而非要强行把后一个值也要做到60度,可能他值不大但是variation也比较小。

尤其是在做哪种leapfrog的filter的时候,可能某些结构在某些地方断环的话,即使理想opamp也可能phasemagrin只有40度而已,这不代表opamp有问题,而是因为这些极点可能是filter的intrinsic pole @瓜在stb断环时通常大家习惯在高阻地方断环,也是为了Ti≈0,更简单。但照理讲Ti即使不等于0也是可以的。或者不说是断环吧,就是指stb probe放的位置。

-

运放稳定性的判断原理的补偿原理?2024-05-06 2016

-

运放电路闭环稳定性的判断方法2023-11-06 3242

-

运放的稳定性仿真分析2023-10-16 2881

-

运放稳定性的标准及测试2021-04-06 4647

-

以运放OP07为例分析运放稳定性2021-01-12 3022

-

运放稳定性理论计算示例2020-04-06 3123

-

运放电路稳定性,这篇给你讲全了!2020-03-12 8134

-

C-Load TM运放稳定性2019-07-10 1545

-

使用SPICE工具检查运放稳定性2018-09-21 2588

-

讨论电容对运放稳定性的影响2018-05-05 20231

-

运放传递函数推导和零极点分析(TI运放稳定性合集第10部分)2018-02-28 17495

-

运放稳定性分析详解(五)2016-08-08 963

-

【运放稳定性分析】TI 高精度实验室 运放培训笔记2016-04-03 4863

-

运放稳定性分析2016-02-19 1057

全部0条评论

快来发表一下你的评论吧 !