高速ADC/DAC的测试方法分享

电子说

描述

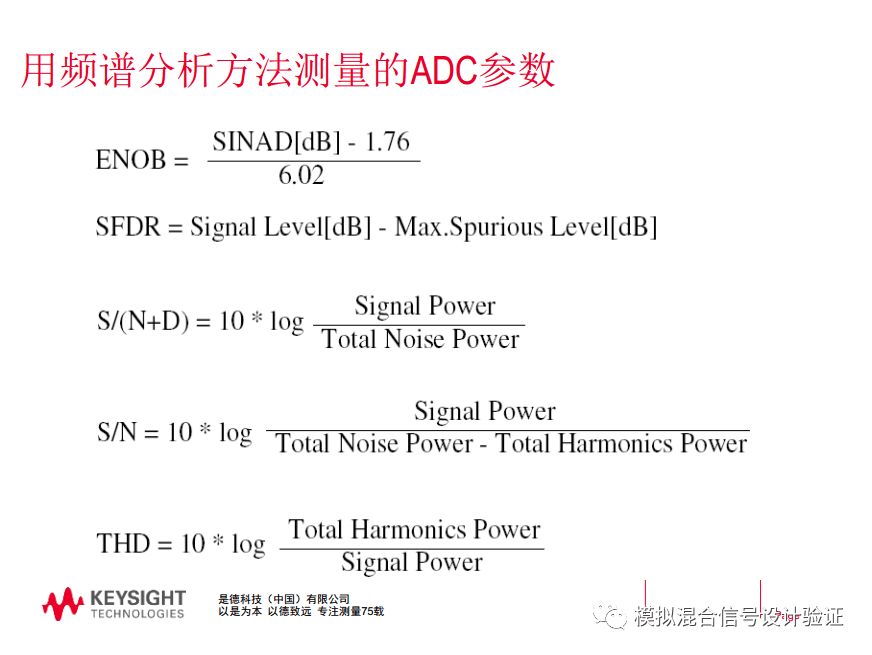

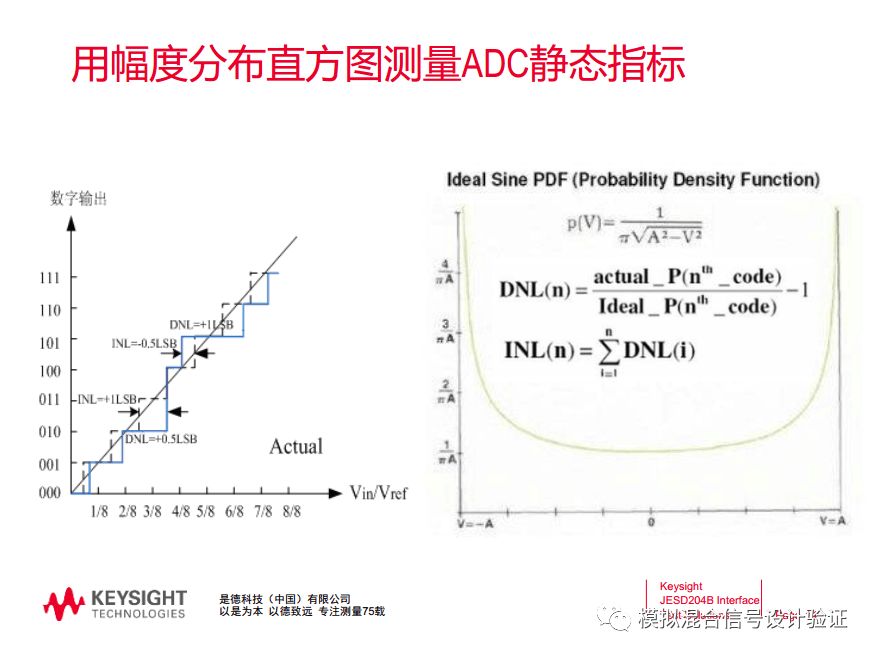

ADC主要的测试指标分为静态指标和动态指标两类:静态指标,包括INL、DNL;动态指标,主要是基于SFDR,在此基础之上计算的ENOB(有效位数)。尽量言简意赅吧。

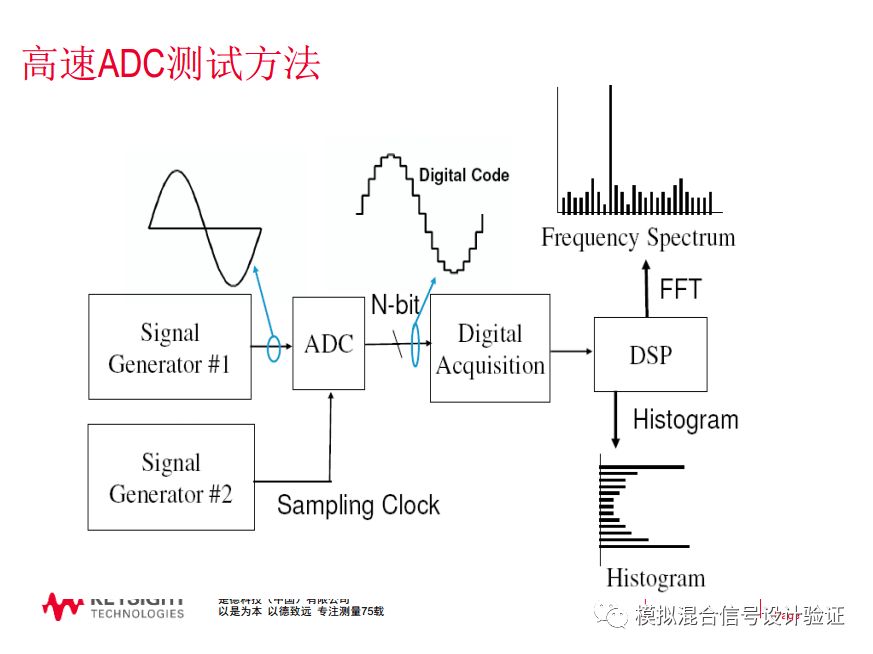

ADC的测试方法,其实简单来说,就是输入和输出,输入怎么给?输出怎么测?怎么计算?以及换算到spec。输入主要是两部分:数据和clk。大家知道ADC的数据和clk都用什么给信号吗?

听众答:ADC的数据是指输入的模拟信号吗?

任老师:哈哈,是的,信号发生器;然而对于ADC,尤其是高精度的ADC,最关键的是信号源的选择,这里需要的是高精度的信号源,也就是说信号源的动态范围要高于被测ADC两个精度位以上,这是关键之一。第二,就是信号源和clk的同步。

接着,我们来看输出,ADC输出的是digital信号,也就是说输出采样到的是数字信号。但是ADC的动态参数表示都是基于频谱分析的方法。也就是说要将输出、采样到的数字信号用FFT变换到频域,这就是大家看到ADC的测试程序为什么主函数是FFT 函数的原因。我记得我们当时实验室测得,10bit以上ADC,都至少是1024点。

听众问:或者转到频域,频率精度到什么精度才合适?

任老师:实测的时候,你有时会发现,FFT点数选的少,测试结果会好,不知大家有没有碰到过这种情况?嗯,但其实这是一种假象。你想10bit ADC输出的全位分辨率就是1024,如果没有采到1024个点,说明丢失了部分数据,不能真实反映ADC的性能。所以大家测试的时候,不能追求偶尔测到一个好的spec, 而应该重点关注自己的测试方法和计算方法,是否真实反映了芯片的性能。

刚刚讲了动态指标,静态指标就相对容易,用高阶的数字万用表,不是手持的那种哦,是专业的可编程的6位半的万用表,把输出全部采下来,使用简单公式就可以计算出INL和DNL,这个就不会用错。动态指标SFDR和ENOB会由于FFT取样点数的变化而变化;但INL和DNL算出来什么就是什么,没有数字转换的问题。数据频率是ADC可以接受的最大输入信号的频率,比方说100M;而时钟频率是采样率,比方说1GS/s。我们在学校的时候,可能觉得测到一个好的spec发个paper就好了;但是工作之后就不一样了。芯片到底怎么样,你心里能没点底数么?我用一张图总结一下最基础的ADC,尤其特指并口ADC的测试基础方法;后面我们再谈串口ADC。

听众问:6位半万用表测ADC?应该是DAC吧?

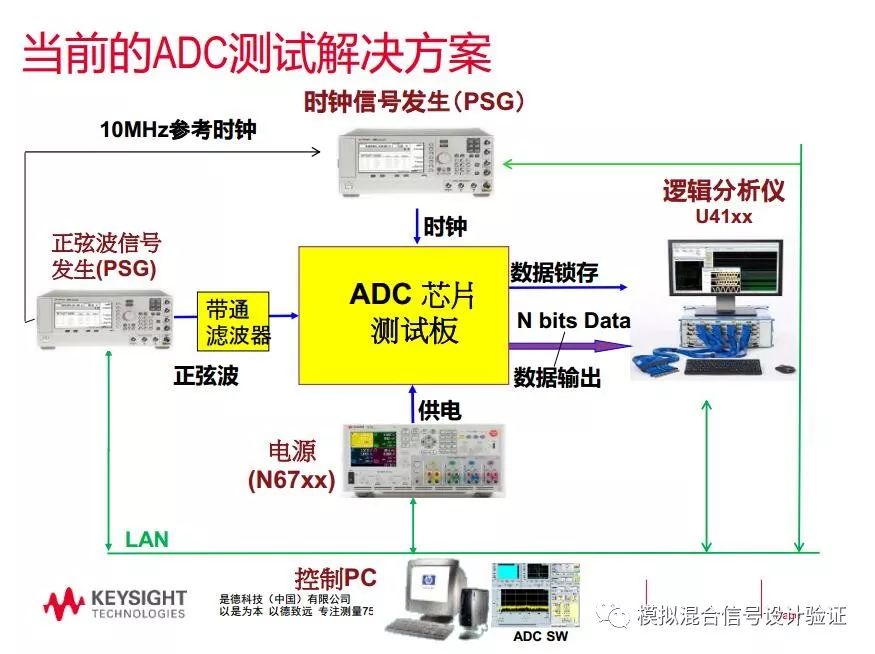

任老师:是ADC哦,ADC输出的digital, 用万用表可以测到;DAC输出的是analog,是连续的模拟信号,直接用频谱仪就可以看了。看这张图,其实动态指标全部都是用逻辑分析仪采集。刚才说INL和DNL大家如果觉得逻辑分析仪复杂的话,用万用表也可以完成。但是动态指标就必须得用逻辑分析仪采集了。哦,漏了一点,信号源和ADC的输入之间,要接带通滤波器,把频点选出来。

Times问:用逻辑分析仪抓出来的数据,放到MATLAB里分析,以前adi有MATLAB例程。

任老师:Times 对!专业!所以大家测试ADC的时候,有一个必须的投入,就是得多买几个质量好的滚降系数高的带通滤波器。带通滤波器推荐大家用那个 mini circuits, 上次分享的李玮韬,是我的闺蜜,她在我们实验室的时候,我们老师给她出钱买了好多好用的带通滤波器,嘿嘿。因为整个信号通路上,如果信号源质量特别好,特别纯净;ADC的能力也很好,但是带通滤波器滤不净,引入杂波,就得不偿失了。

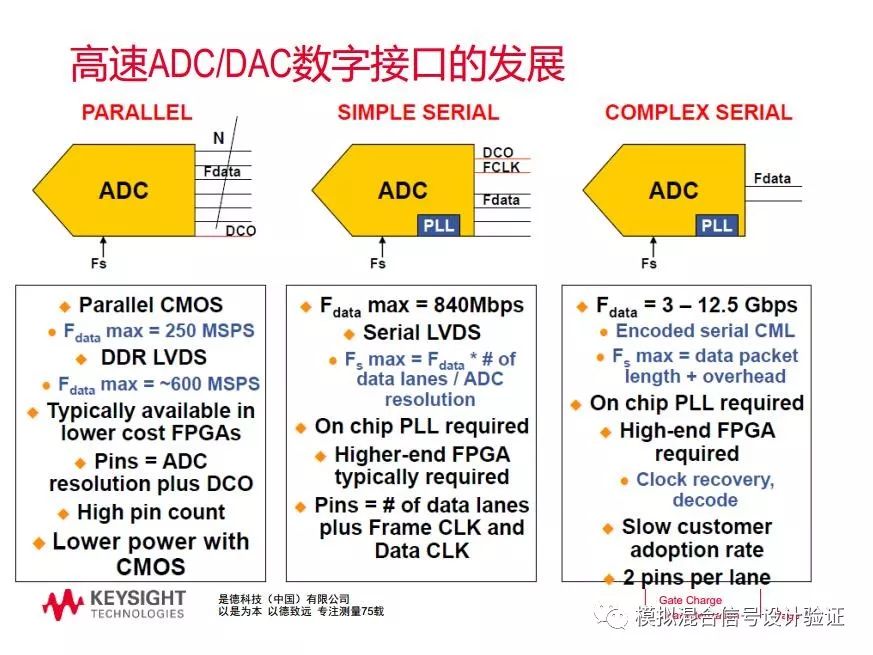

大家好,刚才我发的那个最后一张图片大概就是最上面的一个总结。这个是典型的一个并口,就是并口的ADC,因为如果少的话慢的话,我们传统都是采用并口输出码,那接下来呢,我会讲一点串口。因为群里如果有AD的大神,就知道现在公司里面做的。高速的ADC用的都是串口,并口已经是一种,就是比较早一点的技术。

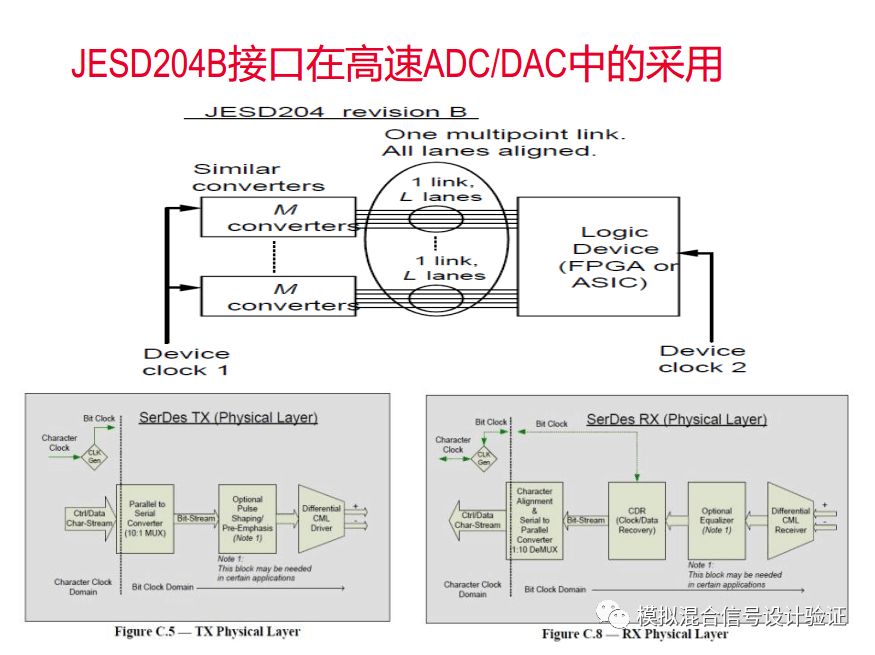

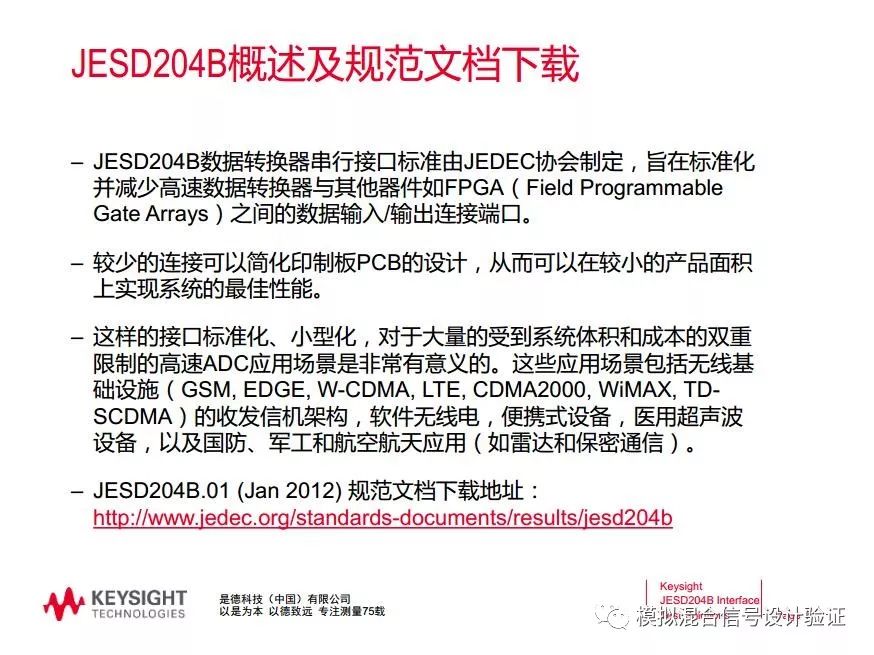

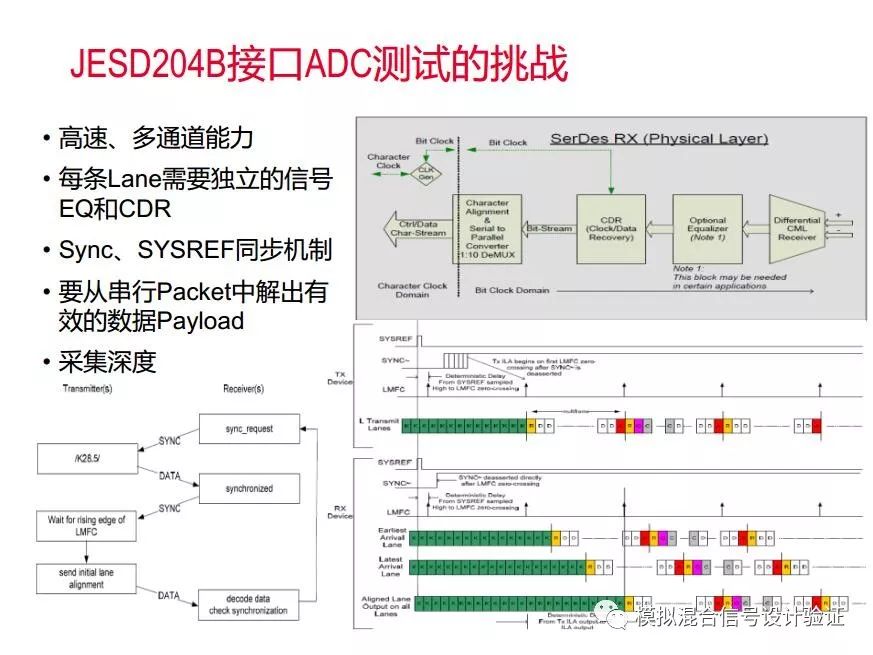

串口就是这样子的哈。JESD204B是SerDes的接口规范。

听众问:以12位ad为例,即便输入稳定电平,噪声本身可能就会引起低2位的跳动,如何能够用万用表测到准确的INL DNL呢?

任老师:大家现在看到ADI做出来的新的2GS/s以上的ADC/DAC都是这种接口的了,很高级~~我换算一下啊,6位半的万用表就是可以测到小数点之后6位半。如果10bit ADC, 输入1V,最小格是1/1024,那4位半的万用表就够了。

听众问:lsb,并不是绝对值。

任老师:哦~~ 那你说的噪声是来源于哪里呢?电源?AD本身,还是输入源?哈哈,那等一下我们再讨论这个哈。

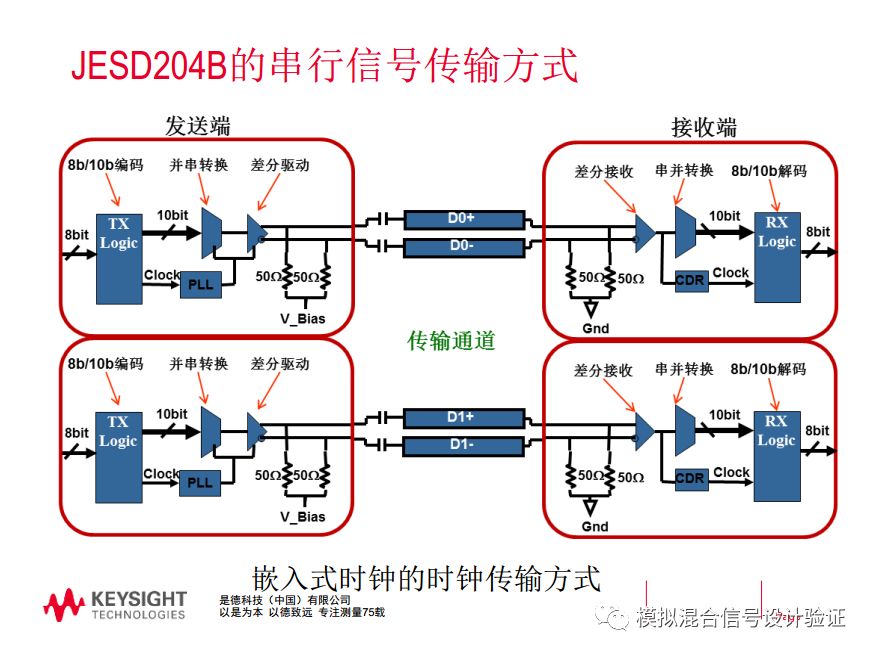

SerDes的信号,大家看到和并口主要的区别是在发送端和接收端上的并串/串并转换、8b/10b编码,差分驱动几个模块.虽然大家设计的时候在这几个部分都要花很大的精力,可是在测试的时侯,就变成了一个黑盒子,主要考虑的还是如何把输入信号给进去、时钟怎么同步、怎么把输出信号采集出来三大问题了。

我长话短说,

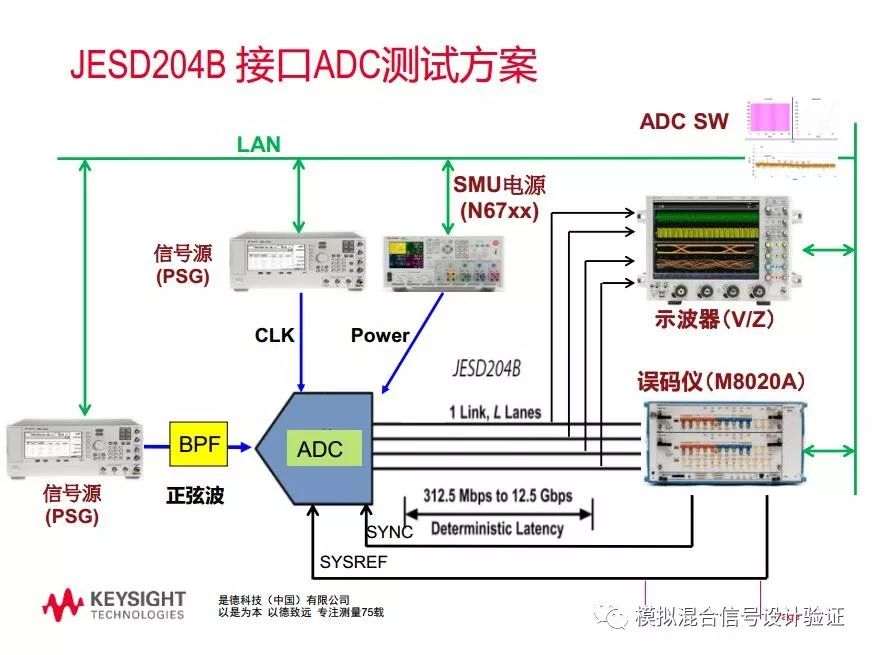

关于Serdes测试的时候,和并口测试的不同,大家看这张ppt ~好在Serdes的测试方法现在也都是十分成熟的了,主要的ADC设计公司用的方法大致相同。

听众问:感觉其中时钟PLL是个关键环节。你们keysight出一个支持204B的接口的逻辑分析仪选件就好了。对测试工程师来说看到的就是被测数据。

任老师:你说的对。Serdes和刚才的并口测试相比,输入信号没变,还是用高纯度的信号源,高纯度、单频点源,就是ADC输入的唯一需求,一旦拥有,别无所求,差别在于输出部分,其实就是支持204B的接口的逻辑分析仪 .被大家猜中了结局。

听众问:204b接口的adc测试时可不可以用带高速口的FPGA?

任老师:可以的只要接口匹配,精度足够,就可以采样率够,和时钟可以同步。你们自己设计的FPGA板吗?测多少bit的ADC?

听众问:ADC数字输出的?

任老师:万用表是测DAC,给输入。没有测ADC的。FPGA 和逻辑分析仪的道理一样的,都是数据采集板。

听众问:DNL vs Noise,INL vs SFDR

任老师:就是我记得我们实验室以前用FPGA 的时候,一直没搞定时钟同步。

-

soctest

2024-04-08

0 回复 举报写的简单易懂,非常好 收起回复

soctest

2024-04-08

0 回复 举报写的简单易懂,非常好 收起回复

-

高速ADC的特征测试和生产测试方法2023-11-28 580

-

高速转换器组表征高速数模转换器(DAC)的性能测试方法2023-11-27 547

-

并行接口的ADC、DAC的测试方法2023-11-07 3389

-

blog高速ADC、DAC测试原理及测试方法2021-09-17 1362

-

高速ADC测试和评估方法2021-09-16 1326

-

AN-928: 了解高速DAC测试和评估2021-03-20 866

-

ADC主要两大测试指标及分享方法2019-07-08 3685

-

高速ADC/DAC的测试方法2018-05-14 21479

-

高速 ADC/DAC 测试原理及测试方法2018-04-03 10667

-

高精度、高速ADC/DAC测试原理及测试方法的介绍2017-11-14 2965

-

多片高速ADC和DAC的作用2017-09-15 1111

-

高级模拟IC设计工程师(ADC DAC 高速接口)-上海2017-07-19 3194

-

高速ADC和DAC设计指南2011-09-07 2320

全部0条评论

快来发表一下你的评论吧 !