四层板的常见PCB叠层

PCB设计

描述

具有电源层和接地层的堆叠

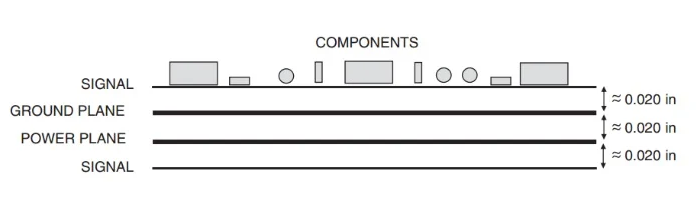

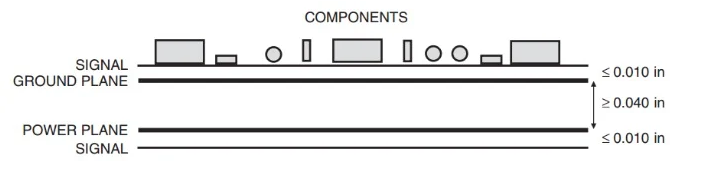

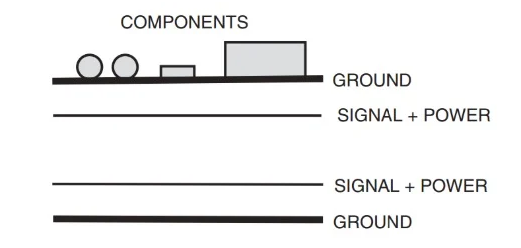

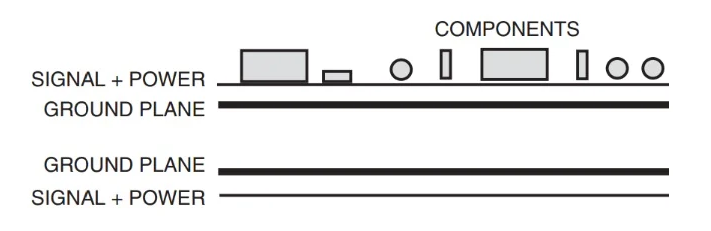

图 1 和图 2 显示了两种常见的四层板叠层。对于这两种板,层的顺序完全相同,但厚度不同。这看起来像是一个很小的修改,但我们会看到不同层之间适当的间距可以提高电路板的性能。

图 1.图片由电磁兼容性工程公司提供。

图 2.图片由电磁兼容性工程提供。

正如您所看到的,两个信号层都位于平面层(接地层或电源层)旁边。因此,给定信号的返回电流可以在相邻平面上流动。这样可以通过化电流产生的环路面积来化电流返回路径电感。低电感返回路径可提高噪声性能并减少电路板辐射(差分和共模发射)。

一般来说,与两层板上实现的相同电路相比,四层板的辐射可减少约 20 dB。保持信号靠近固体平面是这里发挥作用的关键因素。因此,为了进一步改善噪声和EMI性能,我们可以使信号层与其相邻平面之间的绝缘体更薄。这个简单的技巧为我们提供了图 2 所示的改进层叠,其中信号层和层之间的耦合增加,但代价是接地层和电源层之间的耦合减少。这可能不是一个严重的缺点,因为实际上这两个叠层都不能提供足够的平面到平面耦合。我们稍后将更详细地讨论这个问题。请注意,两个叠层具有相同的整体板厚度。

图 1 和图 2 的叠层是常用的,但它们有两个缺点,这两个缺点都是由于接地层和电源层彼此距离不够近,因此仅存在很小的层间电容。它们之间。

传统四层堆叠的缺点

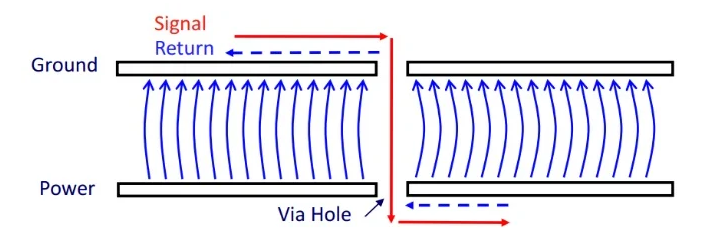

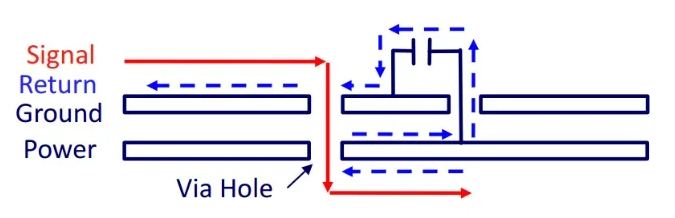

当走线从第 1 层更改为第 4 层或反之亦然时,图 1 和图 2 中的层叠的个问题就会出现。如图 3 所示。

图 3.图片由Altium提供。

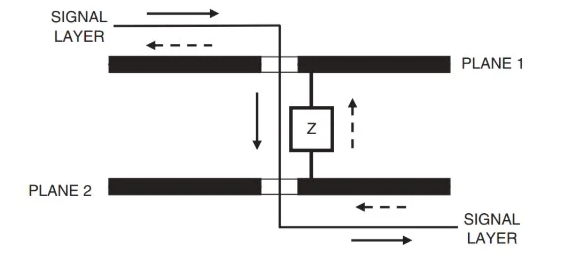

该图显示,当信号走线从第 1 层到第 4 层(红线)时,返回电流也必须改变平面(蓝线)。如果信号的频率足够高并且平面靠得很近,则返回电流可以流过接地层和电源层之间存在的层间电容。然而,由于缺少返回电流的直接导电连接,会导致返回路径中断,我们可以将这种中断想象为平面之间的阻抗(见图 4)。

图 4.图片由电磁兼容性工程提供。

如果层间电容不够大,电场将分布在电路板相对较大的区域上,从而层间阻抗减小,并且返回电流可以流回顶层。在这种情况下,该信号产生的场可能会干扰附近改变层的信号的场。这根本不是我们所希望的。不幸的是,在 0.062 英寸的 4 层板上,各层之间的距离较远(至少 0.020 英寸,如图 1 和图 2 所示),并且层间电容很小。因此,就会出现上述的电场干扰。这可能不会导致信号完整性问题,但肯定会产生更多的 EMI。这就是为什么在使用图 1 和图 2 所示的层叠时,我们避免更改层,特别是对于时钟等高频信号。

通常的做法是在过渡过孔附近添加一个去耦电容器,以降低返回电流所经历的阻抗(参见图 5)。然而,这种去耦电容器由于其自谐振频率较低,因此对于甚高频信号无效。对于频率高于 200-300 MHz 的交流信号,我们不能依靠去耦电容器来创建低阻抗返回路径。因此,我们需要一个去耦电容器(对于 200-300 MHz 以下)和一个相对较大的板间电容以用于更高的频率。

图 5 图片由Altium提供。

通过不改变关键信号的层可以避免上述问题。然而,四层板的小板间电容导致了另一个严重的问题:电力传输。时钟数字IC通常需要大的瞬态电源电流。随着 IC 输出的上升/下降时间缩短,我们需要以更高的速率提供能量。为了提供电荷源,我们通常将去耦电容器放置在非常靠近每个逻辑 IC 的位置。然而,存在一个问题:当我们超出自谐振频率时,去耦电容器无法有效地存储和传递能量,因为在这些频率下,电容器将像电感器一样工作。

由于当今大多数 IC 都具有快速上升/下降时间(约 500 ps),因此我们需要一个额外的去耦结构,其自谐振频率高于去耦电容器的自谐振频率。电路板的层间电容可以是一种有效的去耦结构,前提是各层彼此足够接近以提供足够的电容。因此,除了采用常用的去耦电容器外,我们更喜欢采用紧密间隔的电源层和接地层来为数字 IC 提供瞬态电源。

请注意,由于通用的电路板制造工艺,我们通常在四层板的第二层和第三层之间没有薄绝缘体。在第 2 层和第 3 层之间具有薄绝缘体的四层板的成本可能比传统的四层板高得多。

两个改进的堆栈

下面的图 6 和图 7 显示了四层板的两种改进的叠层。

图 6.图片由电磁兼容性工程提供。

图 7.图片由电磁兼容性工程提供。

与图 1 和 2 的叠层一样,信号走线应邻近平面,并且电流返回路径电感应化。在这方面,图 6 中的堆叠可能并不理想,因为安装的组件将阻止我们在第 1 层上拥有坚固的接地层。假设我们可以在接地层的坚固部分上布线大部分信号迹线,我们观察到信号层和平面之间的绝缘体很薄,这是非常理想的。

图 6 和图 7 中的叠层有两个接地层。这使我们能够拥有低阻抗接地结构并减少共模辐射。此外,在图 6 中,接地层包围信号层。作为屏蔽层,这些平面可以容纳来自高速信号迹线的辐射。我们甚至可以在电路板的外围放置缝合过孔,将两个接地层连接在一起。这将创建一个法拉第笼并进一步遏制辐射。图 7 中的层叠平面不能充当屏蔽层。

通过这两个堆叠,我们就没有电源层了。我们可以使用电源浇注或网格电源结构。如果我们可以布置信号和电源走线并将组件安装在一层(第 1 层)上,则可以采用图 7 中的叠层(该叠层具有坚固的接地层)。然而,如果我们没有足够的空间来容纳所有这些,我们可以使用图 6 中的堆栈。

尽管这两个叠层没有坚固的电源层,但电源层非常靠近接地层。因此,功率注入和接地层将产生相对较大的电容,可以充当高频下的去耦结构。备受尊敬的 PCB 设计师 Rick Hartley 提供了测量数据,证实图 6 和图 7 的电源层和平面之间的去耦优于传统四层板的接地层和电源层提供的去耦(图 1 和 2 ))。使用改进的叠层的去耦结构以及常用的去耦电容器,我们可以更轻松地为高速数字 IC 提供瞬态电源。

-

四层pcb板是哪四层2023-10-17 10427

-

6层PCB叠层设计指南2023-10-16 4478

-

pcb叠层设计原则 如何设计PCB叠层?2023-07-19 3588

-

PCB叠层的几种不同变体2023-04-20 1151

-

PCB线路板叠层设计的注意事项2022-12-08 1797

-

PCB叠层结构设计详解2022-09-30 2913

-

【资料】PCB的EMC设计之常见的PCB叠层结构2021-03-29 2794

-

为什么要进行PCB叠层2020-11-03 6061

-

示例:从两层板到八层板的PCB叠层2020-10-30 3719

-

PCB刚柔叠层设计优化2020-09-16 3008

-

如何设计4层PCB叠层2019-07-31 20818

-

设计四层PCB电路板时,叠层一般怎样设计呢?2018-04-13 28456

-

PCB叠层设计2016-05-17 4652

全部0条评论

快来发表一下你的评论吧 !