数字IC前端设计+后端设计流程实现

电子说

描述

一、IC 前端设计流程(RTL to Gate-Netlist)

1、 芯片架构 :考虑芯片定义。

2、 RTL 设计 :芯片功能设计。硬件描述语言如 Verilog、VHDL、SystemVerilog。

3、 功能仿真 :验证芯片功能设计的正确性。EDA 工具如 Synopsys 的 VCS、Cadence 的 NC-Verilog、Mentor 的 ModelSim。

4、 逻辑综合 :将 RTL 转换成门级网表 Gate Netlist;逻辑综合要指定基于的库、工艺,设定约束条件。综合之前的仿真为前仿真,综合之后的仿真为后仿真,所以这里还需要一个后仿真。EDA 工具如 Synopsys 的 Design Compiler、Cadence 的 Genus。

5、 静态时序分析(STA) :检查建立时间(Setup)和保持时间(Hold)是否违例(Violation)。EDA 工具如 Synopsys 的 PrimeTime。

6、 形式验证 :在功能上,对综合后的网表进行验证。通过等价性检查(Equivalence Check)方法,以功能验证后的 HDL 设计为參考,对照综合后的网表功能,检查是否在功能上存在等价性,从而保证在逻辑综合过程中没有改变原先 HDL 描述的电路功能。EDA 工具如 Synopsys 的 Formality、Cadence 的 Conformal。

二、IC 后端设计流程(Gate-Netlist to GDSII)

作为 IC 设计的后端纳米工艺 VLSI 物理设计与实现流程详解文档,包括了 Cadence Genus 综合技术,物理设计与实现流程,RTL - to - GDSII 流程,让你了解库文件(网表库、时序库、物理库)、RTL 文件、时序约束文件、综合、平面布局规划(芯片大小、IO、电源规划、宏单元、布线光晕、摆放块等等)、摆放、布线(实验布线、特殊布线、真实布线)、时钟树综合(预时钟树和后时钟树综合)、时序分析、时序修正、电源分析、信号完整性分析、金属填充、物理验证、代工厂 Tapeout 等等。

0、 综合 Synthesis :将硬件描述语言转化成门级网表,即 RTL - to - Netlist。(这里隶属于前端,所以,以 0 表示)EDA 工具为 Cadence 的 Genus,输入文件为 .V + .LIB + .SDC(RTL 设计文件、工艺库文件、时序约束文件)。

1、 设计输入 Design Import :输入文件为网表库(.V)+ 时序库(.LIB)+ 物理库(.LEF)+ 时序约束文件(.SDC)+ IO 文件(.IO)+ 可选文件如规划布局文件(.FP)、工艺文件(.QRC)、版图文件(.GDS)、时钟树规范文件(.SPEC)、扫描链信息等等。

2、 平面布局规划 Floorplan :包括芯片大小(Die Size)的规划、I/O Pad 规划、宏单元(Macro)以及大量硬核或模块(Hard Cores、Hard Blocks)的规划等等,是对芯片内部结构的完整规划和设计。其中,电源规划是给整个芯片的供电设计规划出一个均匀的网络。Power Ring(电源环)指为了均匀供电,包围在芯片周围的环形供电金属,实现稳定供压的作用;Power Strips(电源条)指芯片内部纵横交错的 Power Grids(电源网格),主要是防止 IR Drop(电压降),也就是电路中有过高的压降会导致器件运行速度很慢;

3、 扫描链定义 Scan Chain :扫描链(Scan chain)是可测试性设计(DFT)的一种实现技术;它通过植入移位寄存器(Shift Register),使得测试人员可以从外部控制和观测电路内部触发器的信号值,从而使得设计具有可控性和可观察性。

4、 摆放 Placement :平面布局规划后,宏单元、I/O Pad 的位置和放置标准单元的区域都已确定,Placement 是将设计中的所有标准单元和块摆放到 Floorplan 的设计中;

5、 时钟树综合 Clock Tree Synthesis :通过插入缓冲器 Buffer 减小负载和平衡延时(主要是针对时钟偏差,能够消除 Clock Skew),时钟网络及其上一级一级的缓冲单元构成了时钟树;

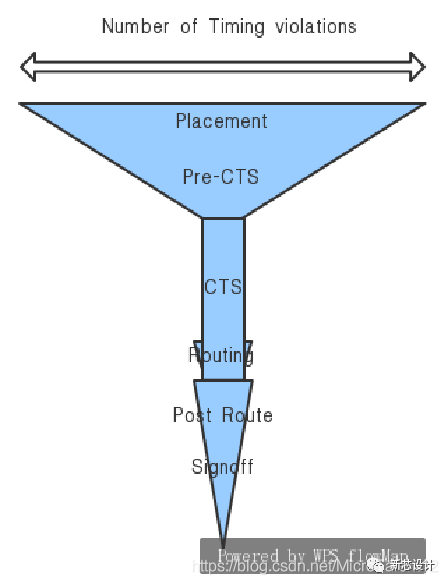

6、 静态时序分析 STA Static Timing Analysis :时钟树插入之后,每一个单元的位置都确定下来了,工具可以提出 Global Route 形式的连线寄生参数,此时对延时参数的提取就比较准确了;然后通过 EDA 工具指定提取模式如 RC 提取模式、指定延时计算模式等等来进行建立时间与保持时间分析;如果发生时序违例,那么则返回上一层设计,通过修改设计等等使其满足时序要求,从而达到时序收敛。通常,时序违例在不同的阶段有着不同的数目,如下所示:

时序违例在不同的阶段的不同数目

7、 布线 Routing :指的是在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束的条件下,根据电路的连接关系将各单元和 IO Pad 用互连线 Interconnect 连接起来;通俗地讲,就是将 Placement 摆放后的模块连接起来。Trial Route,实验布线,是一种快速的全局布线。Special Route,特殊布线,简称 SRoute,连接 Power Structure 的 Router。NanoRoute,真实布线,是一种 Smart Routing,大致分为 Global Route(全局走线)和 Detail Route(详细走线)。PR 的 EDA 工具如 Synopsys 的 IC Compiler、Cadence 的 SoC Encounter 和 Innovus。

8、 信号完整性 SI Signal Integrity :指的是分析信号在传输路径上的质量。信号完整性主要表现在延迟、反射、串扰、时序、振荡等几个方面。

9、 金属填充 Metal Fill :指的是在设计中添加金属线形状以满足 Foundary 厂金属密度规则的过程,如 Dummy Metal。另外,还有 Filler 的插入,如 Pad Filler 和 Cell Filler;Filler 指的是标准单元库和 I/O Pad 库中定义的与逻辑无关的填充物,用来填充标准单元和标准单元之间、I/O Pad 和 I/O Pad 之间的间隙。

10、 物理验证 Physical Verification :主要有连线 Connectivity、金属密度 Metal Density、几何形状 Geometry、过程天线 Process Antenna 等一些验证要素。DRC(Design Rules Check)是对芯片版图中的各层物理图形进行设计规则检查;LVS(Layout VS Schematic)是为了检查版图文件功能与原有电路设计功能的一致性,从而将版图与网表进行比较。

11、 流片 Signoff :指的是成功完成 IC 设计的所有检查和验证的一个标志。

-

【「数字IC设计入门」阅读体验】+ 数字IC设计流程2024-09-25 1286

-

IC前端和后端设计的区别2011-12-19 43926

-

IC设计流程2012-01-11 10771

-

数字IC后端(CAD)2013-04-08 3006

-

数字IC后端设计介绍,写给哪些想转IC后端的人!2020-12-29 4404

-

数字IC前端和后端有何区别2021-07-28 5817

-

数字IC的设计流程有哪些2021-10-20 2621

-

IC前端设计(逻辑设计)和后端设计(物理设计)的详细解析2017-12-25 34441

-

IC设计前后端流程与EDA工具介绍2018-04-19 12726

-

数字IC设计流程2020-12-09 8328

-

数字IC前端后端的区别,数字IC设计流程与设计工具2021-11-06 2477

-

数字IC前端设计流程及工具2023-06-25 3102

-

ic设计前端到后端的流程 ic设计的前端和后端的区别2023-08-15 7280

-

芯片设计分为哪些步骤?为什么要分前端后端?前端后端是什么意思2023-12-07 6712

-

数字电路设计中:前端与后端的差异解析2025-02-12 2207

全部0条评论

快来发表一下你的评论吧 !