电力输送、材料和互连领域即将发生巨大变化

电子说

描述

在设备互连方面,铜无可匹敌。其低电阻率和高可靠性为业界提供了出色的片上互连和芯片间连线服务。但在逻辑芯片中,随着互连堆栈上升到14级范围,并且阻容(RC)延迟在总延迟中所占的比例越来越大,晶圆厂正在寻求替代金属来维持性能。

减少RC延迟并帮助缩小标准尺寸单元的一种选择是背面供电。这种有点激进的主张通过芯片的背面而不是正面为设备供电,从而缓解了互连拥塞并改善了电力传输。第二种选择是混合键合,它具有多种优点,包括能够以较小的延迟组合不同的设备。

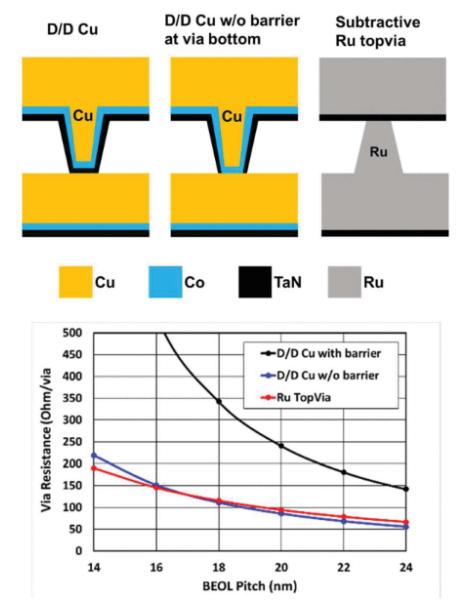

在开发出将铜互连沉积到线路和通孔中的双镶嵌方法之前,业界在减材沉积和蚀刻方案中使用铝。现在,由于衬里金属(通常是钴)和势垒对电阻率的影响,铜互连已达到其缩放值。替代金属不需要衬垫或阻挡层,但它们的集成可能需要过渡回沉积和蚀刻工艺。

在蚀刻期间和之后控制金属的氧化将是一个巨大的挑战,特别是在使用高深宽比金属线来获得较低电阻的情况下,需要在线之间集成气隙。空气是低k材料(k=1.0),但与低k电介质和二氧化硅不同,它牺牲了结构支撑。

英思特使用隔离物拉出方法的顶部通孔工艺流程,该方法类似于双镶嵌中的双图案化。自对准光刻-光刻-刻蚀(SALELE)步骤形成顶部通孔和底层金属线。为了尽可能扩展铜工艺,芯片制造商正在消除通孔底部的阻挡金属沉积(TaN),这对通孔电阻率有着影响。

图1

图1

背面电力传输互连

制造方式的另一个颠覆性变化涉及背面电力传输(BPD)——将电力传输转移到晶圆背面,以便晶体管上方的互连层仅传输信号。分开的原因是电力传输和信号传输有不同的需求。电源遵循低电阻路径(较粗的电线),但大电流使其容易受到电迁移的影响。对于信号,工程师需要低电容和小横截面,但一些电阻是可以的。先进逻辑中有12至14个金属层,功率密度有所提高,电源电压(IR压降)也很大。

英思特使用细间距 nanoTSV的方法(200nm 间距,320nm 深),从金属0向下延伸并降落在具有严格覆盖控制的埋入式电源轨上。将正面粘合到载体晶圆上,减薄晶圆,然后蚀刻并填充TSV。

事实上,混合键合正在用于实现背面配电。混合键合涉及铜连接和周围电介质的键合,每单位面积的连接数比铜微凸块多1,000倍。

晶圆到晶圆(W2W)混合键合比芯片到晶圆(D2W)混合键合更加成熟。芯片到晶圆的对准要复杂得多,因为要管理的是芯片四个角的位置,而不是两个晶圆的整体位置。晶圆对晶圆键合常用于将像素阵列键合至相机图像传感器中的底层芯片。

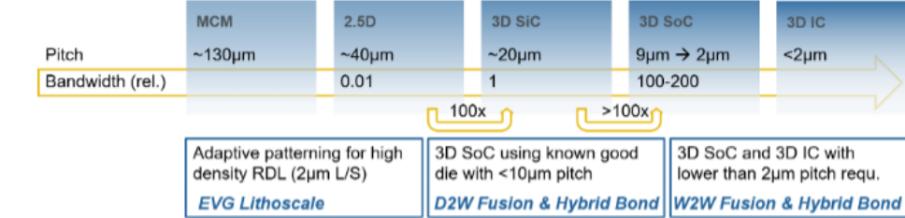

图 2:不同集成度的互连间距和带宽

图 2:不同集成度的互连间距和带宽

先进封装

从SoC到多芯片封装和系统的巨大转变确实将性能、功耗和成本指标从芯片转移到了系统。性能问题不再只是一个芯片问题。向小芯片的过渡意味着这些小芯片之间需要高带宽接口,这是先进封装的驱动力。高带宽和小芯片尺寸需要高信号速度,并且通常需要宽接口总线。后者给具有更紧密凸块间距的较小芯片凸块带来了相当大的压力。反过来,这需要更先进的设备来实现芯片和互连之间的良好对准。

结论

随着业界越来越多地采用新型互连材料、背面供电、混合键合和先进封装,人们将了解更多有关这些工艺的制造细节。在用尽所有途径之前,特别是在新的集成方案带来重大挑战的情况下,将对铜互连进行小幅改进。

-

2014年托福考试面临着怎么样的巨大变革?2014-02-20 2647

-

云计算环境下,UPS电源市场将发生巨大变化2018-08-20 2993

-

全球半导体“疯狂”并购退潮,巨头出击细分领域2018-09-12 3024

-

新款iPhone天线结构将发生巨大变化2019-05-06 3176

-

随着技术进步 作为安防子系统的出入口控制系统也发生着巨大变化2019-05-15 1084

-

解读鸿蒙系统带给生活的三大变化2019-08-19 4324

-

医疗保健行业采用大数据将使其发展方式产生巨大变化2019-08-26 3517

-

楼宇对讲产品行业正在发生着巨大的变化2020-03-15 2351

-

可穿戴传感器或将促进医疗健康领域的巨大变革2020-04-03 3546

-

北京科博会展示5G时代日常文娱生活的巨大变化2020-09-18 1591

-

物联网技术的快速发展,会给环保领域带来巨大变化2020-10-18 2580

-

硅 MOSFET 的巨大优点及其变化2022-08-01 1955

-

芯片和封装级互连技术的最新进展2024-10-28 2251

全部0条评论

快来发表一下你的评论吧 !