低压栅极驱动器的结构组成和工作过程

描述

引言:对于中压或高压的电源系统,对MOS组的要求特别高,DrMOS已经不能满足设计参数要求,此时将DrMOS再次分拆开来,将驱动部分独立成为栅极驱动器。栅极驱动器的强度和抗扰度极佳,非常适用于电机驱动、家用电器、SMPS、电池供电应用和大功率照明。

1.结构组成

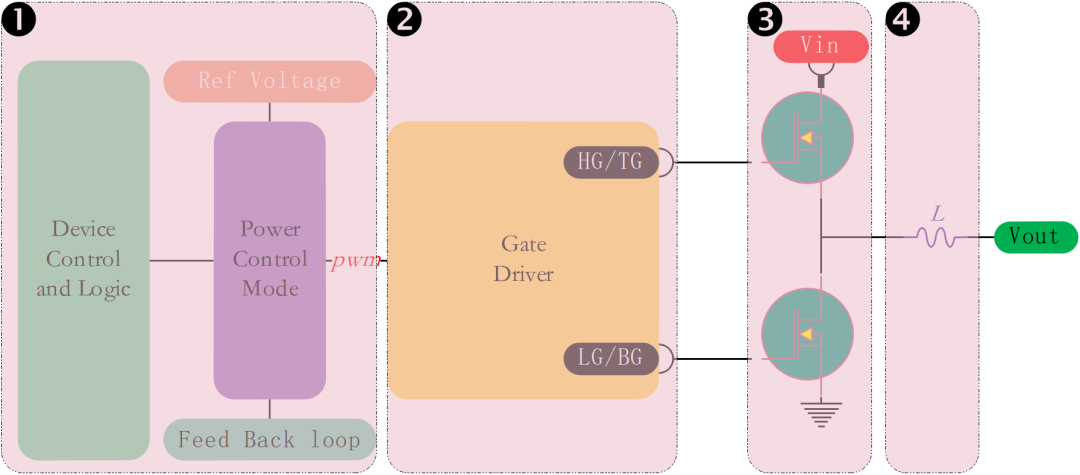

在SMPS中,如图8-1所示,(Low Voltage Gate Drivers)低压栅极驱动器 (半桥栅极驱动器)即是2部分。而在电机驱动中,两个半桥栅极驱动器就可以组成一个H桥驱动器,控制电机的转速和方向,在AC-DC/DC-AC中,还充当整流器和逆变器,例如无线充电链路。每一个功率器件都需要一个驱动器(驱动芯片)

图8-1:DC-DC结构层级

图8-1中是以PWM三态模式驱动,还有另外一种两态模式驱动,本节先介绍PWM模式,下节介绍HL两态模式。

2.PWM三态模式驱动

驱动结构

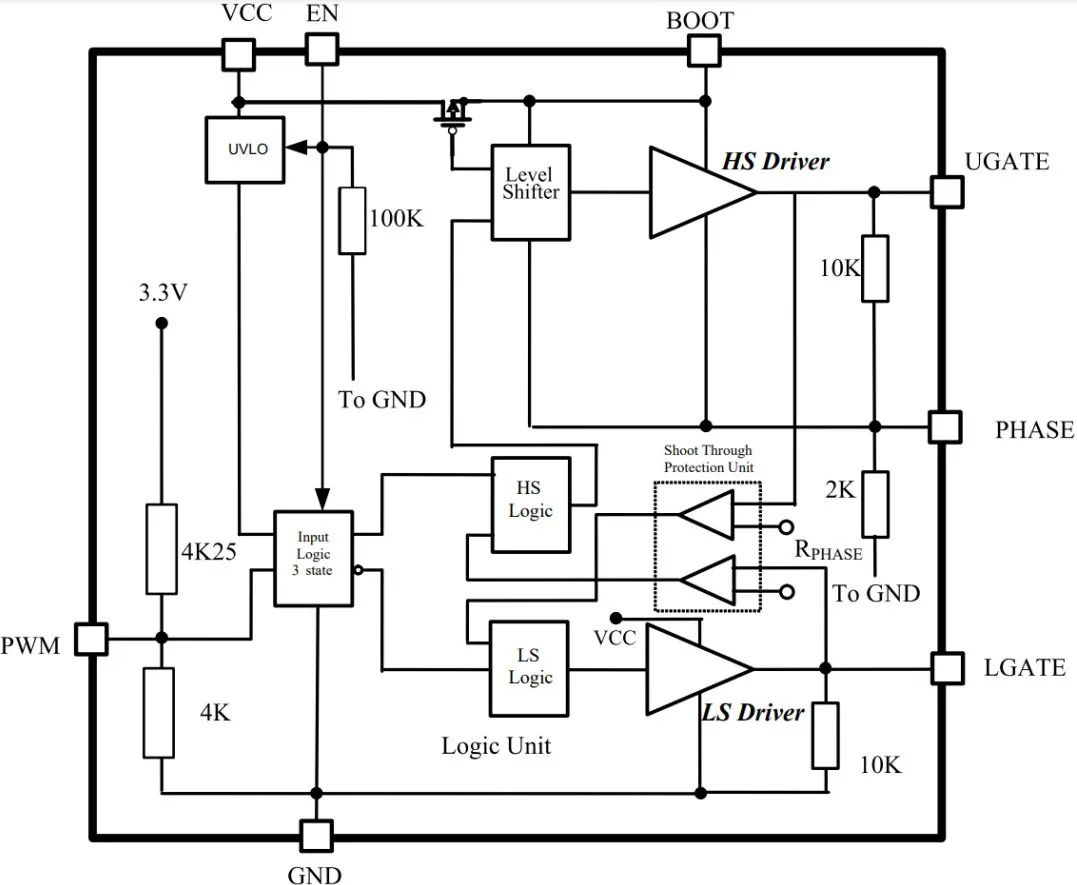

图8-2是一个和数字电源控制器搭配使用的半桥栅极驱动器IC内部结构图,其中VCC是独立供电引脚,BOOT和PHASE用于自举设置(BST),PWM来自于数字电源控制器的PWM输入,输入信号PWM参考SGND引脚,TG/BG(UG/LG)状态由该引脚处的电压决定。驱动器内部实现了一个嵌入式电阻器网络,如果该引脚是浮动的,内部电阻分压器会触发高Z模式,在该模式下BG和TG都关闭,Layout时该引脚上的寄生电容应最小化。

图8-2:典型的半桥驱动IC内部结构

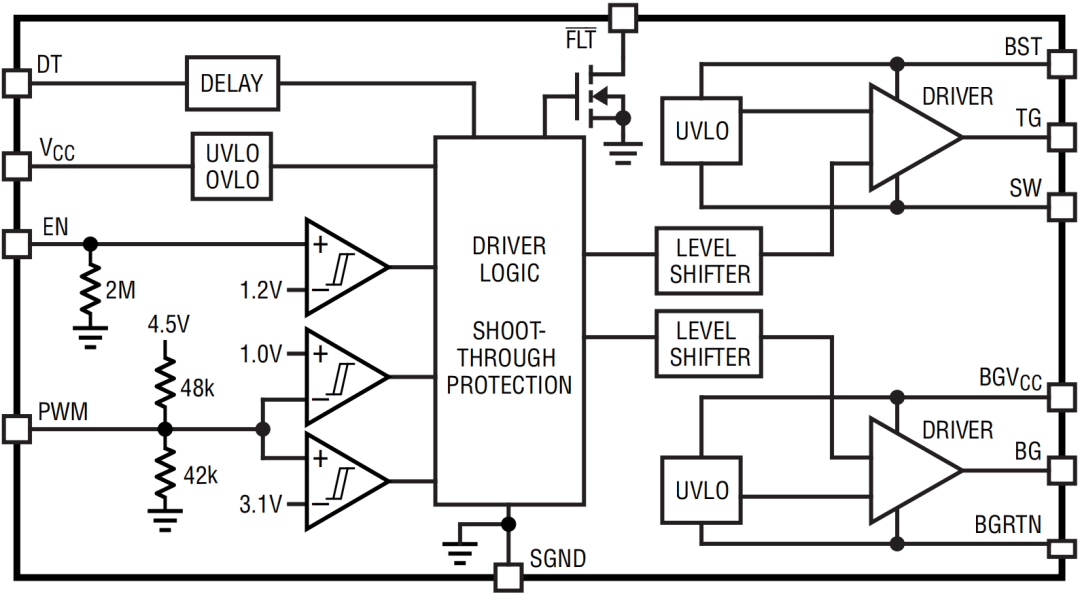

图8-3:典型的半桥驱动IC内部结构-2

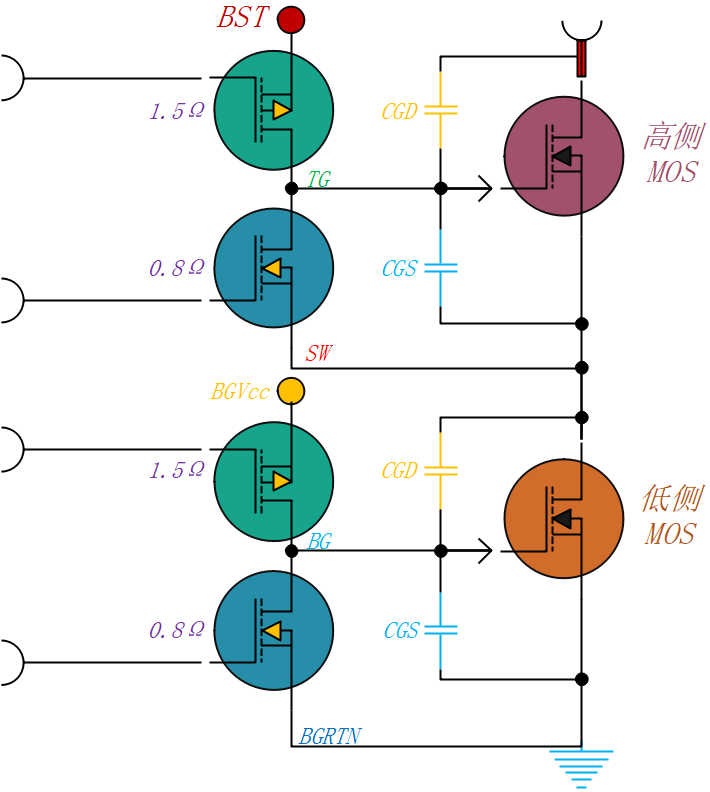

栅极驱动器接收以地为基准的低电压数字PWM信号,以驱动半桥配置中的两个N沟道功率MOSFET。低侧MOSFET的栅极被驱动为高或低,在BGVCC和BGRTN之间摆动,这取决于PWM引脚的状态。类似地,高侧MOSFET的栅极与低侧MOSFET互补地被驱动,在BST和SW之间摆动。低侧驱动器和高侧驱动器都是浮栅驱动器,独特的双浮动结构使栅极驱动器输出稳健,对地噪声不太敏感,对称设计允许半桥输出是输入逻辑的反相或非反相。

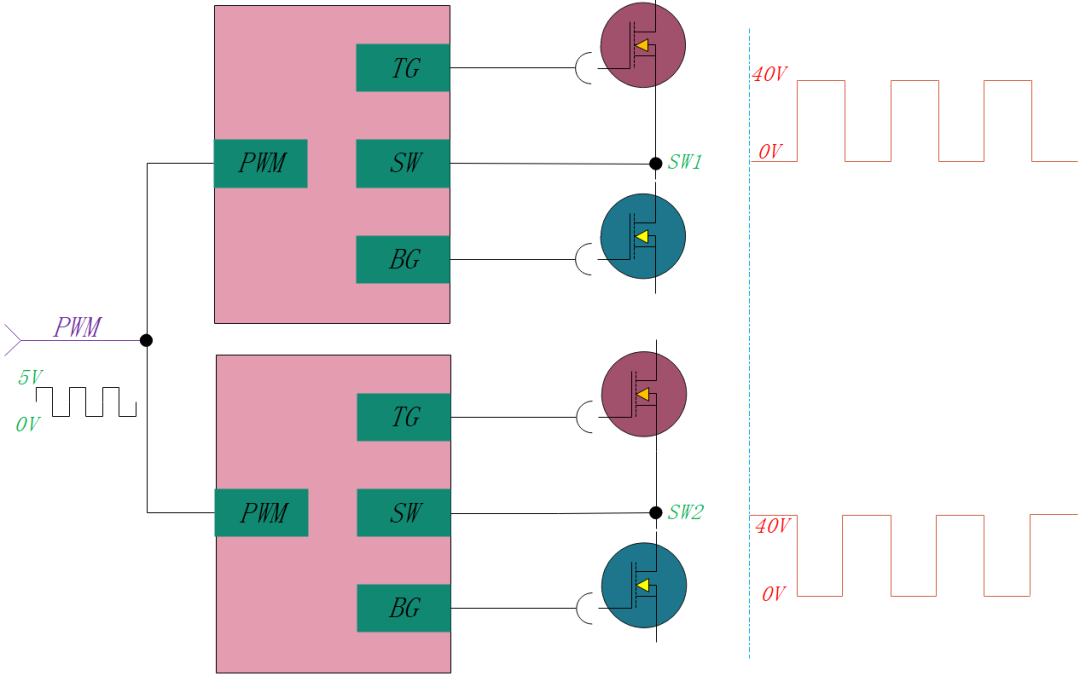

而同一个PWM波可以同时驱动多个驱动器,如图8-4所示:

图8-4:多驱动器模式

驱动逻辑

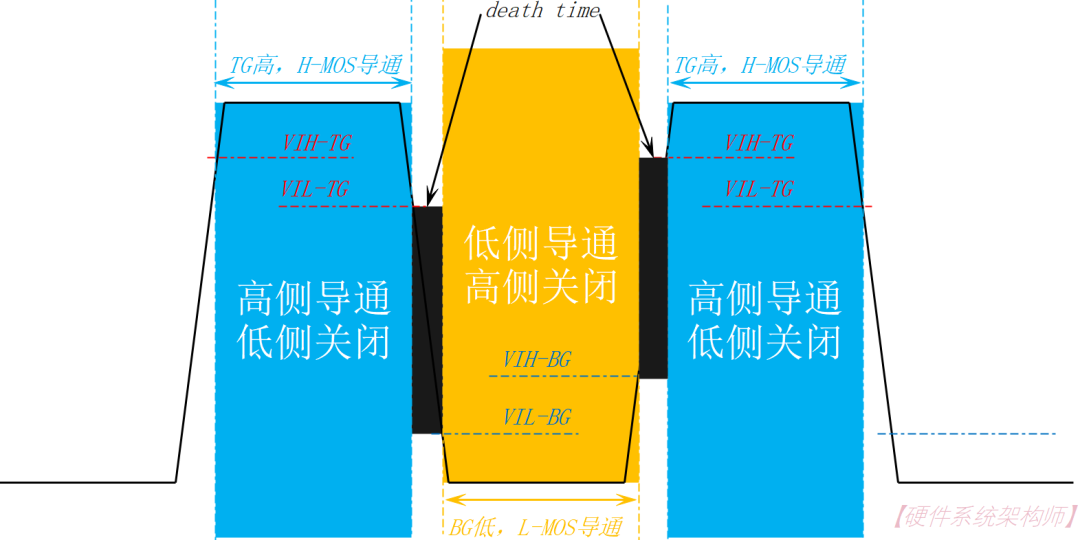

对于具有固定转换阈值的三态PWM输入,驱动器的转换阈值和三种输入状态之间的关系如图8-5所示。当PWM上的电压大于阈值VIH(TG)时,TG被上拉到BST,使高侧MOSFET导通,该MOSFET将保持导通,直到PWM降至VIL(TG)以下。类似地,当PWM小于VIH(BG)时,BG被上拉到BGVCC,使低侧MOSFET导通,BG将保持高电平,直到PWM增加到阈值VIL(BG)以上。

图8-5:三态及其转换阈值

驱动器还能够将两个外部MOSFET驱动到断开状态,当PWM信号电平进入关闭窗口或三态(通常在1.2V和2V之间)时,在关闭保持时间到期后,两个MOSFET都会关闭。当控制器想要减少活动相(多相架构)的数量以降低功耗时,此功能非常有用。原则上,三态也可以用于在重负载和轻负载转换期间提高性能。

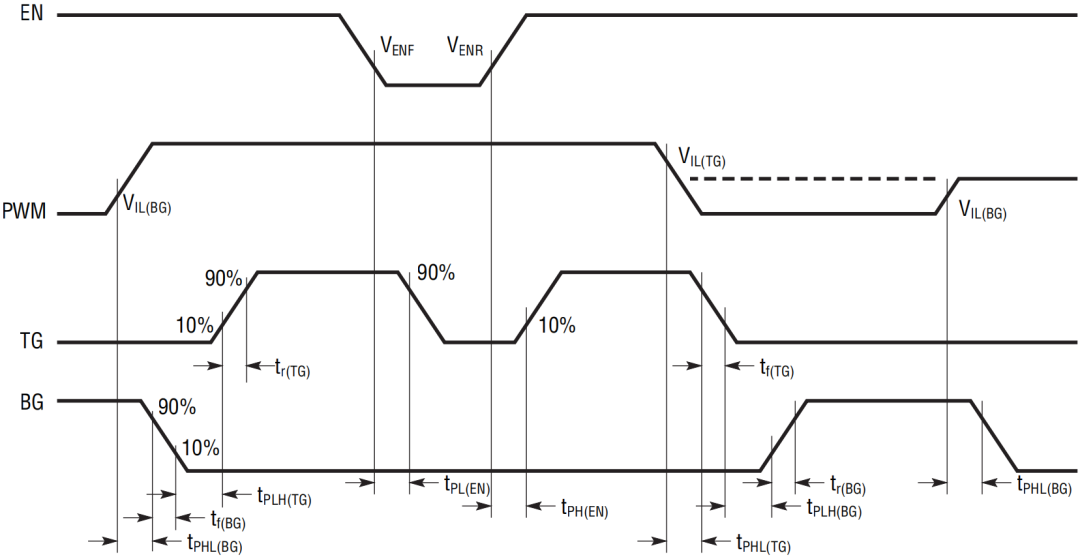

图8-6是驱动器的时序图,其中自适应交叉导通保护基于MOSFET在关断期间的栅极到源极电压,当PWM信号变低时,高侧MOSFET将开始关断,一旦高侧MOSFET的VGS放电到1V以下,低侧MOSFET就会开始导通。当PWM信号变高时,低侧MOSFET将开始关断,一旦低侧MOSFET的VGS在1V以下放电,高侧MOSFET就会开始导通。为了避免高侧MOSFET和低侧MOSFET之间的交叉导通,驱动器内部采用了自适应反击穿控制方案,这种自适应方案允许将各种不同的功率MOSFET用于不同类型的功率转换,但是为了最大限度地提高整体解决方案的效率,死区时间保持得尽可能短。

对应的VIH和VIL电平之间的滞后消除了由于开关转换期间的噪声而引起的错误触发,但是应注意防止噪声耦合到PWM引脚,特别是在高频、高电压应用中。

图8-6:三态栅极驱动器时序图

驱动能力

由于功率MOSFET通常占转换器中功率损耗的大部分,因此具备快速导通和关断特性的功率MOSFET非常重要,从而最大限度地减少转换时间和功率损耗。如图8-7所示,驱动器的典型1.5Ω上拉电阻和0.8Ω下拉电阻相当于10V驱动器电源下的3A峰值上拉电流和6A峰值下拉电流。BG和TG都可以驱动MOSFET的快速导通转变,具有以18ns上升时间驱动3.3nF负载的能力,所以一定要关注所选MOS的寄生电容和Layout电容。

图8-7:半桥配置中的简化输出级

3.工作过程 *

当VCC引脚电压超过VCC上升电压阈值(VUVLO_R)时,驱动器开始根据PWM状态进行操作。在VCC引脚电压达到VCC上升阈值之前,两个MOSFET都保持在断开状态。对于VCC,建议其上升沿的斜率高于上升UVLO阈值附近的5V/100ms。当PWM信号执行从低状态到高状态的转换(PWM电压高于2.5V典型值)时,在关断传播延迟时间之后,低侧MOSFET关断,接下来在导通传播延迟时间之后,高侧MOSFET导通。一旦接通时间到期,PWM信号从高状态转换到到低状态(PWM电压低于0.8V典型值),这将在关断传播延迟时间之后将高侧MOSFET从导通状态驱动到截止状态。

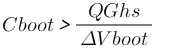

4.自举电容

高侧MOSFET通过自举电路供电,有的内部带自举电源,有的驱动器嵌入自举二极管,因此要完成Boot网络,只需要在PHASE引脚和BOOT引脚之间添加电容。在许多情况下,驱动器经过优化已具备最佳的开关动作,因此不需要外部电阻(串联栅极驱动电阻)。根据高侧MOSFET栅极电荷来选择自举电容,以下公式给出了由于高侧MOSFET的充电而引起的自举电容两端的电压降的准确估算:

ΔVBoot是自举电压的浮动值,这通常应尽可能低,以避免高侧MOSFET的Rdson下降,一般0.1V和0.01V之间的值是可以接受的。

低侧MOSFET驱动器通过VCC引脚供电,自举电容的相同考虑因素和公式可以应用于对VCC引脚进行滤波的电容。部分驱动器还支持将驱动电压从4.5V调整到8V,这样的灵活性使设计者能够以任何所需的方式塑造效率曲线。

5.注意点

驱动器输出上的强下拉防止了交叉传导电流,例如在图8-7所示的半桥配置中,当BG关闭低侧功率MOSFET,TG打开高侧功率MOSFET时,SW引脚上的电压可能会非常迅速地上升到VIN,该高频正瞬态电压将通过低侧功率MOSFET的CGD电容耦合到BG引脚。如果BG引脚没有被充分压低,BG引脚上的电压可能会上升到低侧功率MOSFET的阈值电压以上,从而瞬间使其重新导通,因此高侧和低侧MOSFET都将导通,这将导致大量的交叉导通电流通过MOSFET从VIN流到地,从而造成相当大的功率损失并且可能损坏MOSFET,因此建议BG和TG引脚的PCB走线尽可能短粗,以最大限度地减少寄生电感。

-

为什么需要栅极驱动器?栅极驱动器及其应用介绍2024-04-02 3186

-

单片机应用系统的结构与工作过程2017-07-05 2452

-

隔离式栅极驱动器揭秘2018-10-25 4278

-

隔离式栅极驱动器的揭秘2018-11-01 2722

-

栅极驱动器是什么2021-01-27 3802

-

栅极驱动器是什么,为何需要栅极驱动器?2021-07-09 6348

-

传感器的原理结构及工作过程2009-11-23 3125

-

了解您的栅极驱动器2017-04-26 4358

-

栅极驱动器电流多少正常啊,栅极驱动器电流怎么计算2023-07-14 4134

-

栅极驱动器芯片的原理是什么2024-06-10 4190

-

无刷电机驱动器的工作原理和结构组成2024-06-12 5903

-

什么是栅极驱动器?栅极驱动器的工作原理2024-07-19 25975

-

采用智能栅极驱动器的低压电机驱动操作2024-09-25 392

-

栅极驱动器的定义和结构2025-02-02 2129

-

LM5101系列 高压高压侧和低压侧栅极驱动器数据手册2025-05-21 1207

全部0条评论

快来发表一下你的评论吧 !